Fターム[5F004EA23]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | エッチングストッパー (168)

Fターム[5F004EA23]に分類される特許

41 - 60 / 168

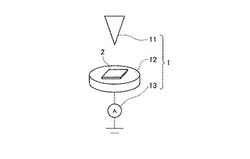

エッチング装置及びエッチング方法

【課題】集束イオンビームによりエッチングする際に精度良くエッチング深さを制御する。

【解決手段】ステージ12に電気的に導通させて固定した試料2を集束イオンビームによりエッチングする際に、グランドとステージ12の間に設置した微小電流計13によりエッチング電流を測定する。これにより、測定した電流の大きさ、変化に基づいて試料2の層毎の違いを検出できる。その結果、任意の深さでエッチングを止めて、エッチング深さを制御することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチ開口部に傾斜面を形成し、耐圧低下を防止できる半導体装置及びその製造方法を提供することができる。

【解決手段】本発明にかかる製造方法は、半導体基板10にトレンチ21を形成する工程と、絶縁膜23をトレンチ21に堆積させる工程と、プラズマエッチングによりトレンチ21底部の絶縁膜23をエッチングするとともに、トレンチ開口部21aに半導体基板主面10aに対して傾斜角αをなす傾斜面25を同時に形成する工程と、半導体基板10の上面からトレンチ21底部の絶縁膜23に亘って半導体基板10及びトレンチ21を被覆するゲート絶縁膜24を形成する工程と、ゲート絶縁膜24上にゲート電極22を形成する工程とを備える。

(もっと読む)

MEMSによるスプレイ装置用ノズル集積膜の製造方法、及び該ノズル集積膜を含むスプレイ装置

【課題】 MEMSテクノロジーで得られるスプレイ装置用ノズル集積膜を製造する方法、及び既知の技術が持つ欠点を有することのない上記膜を含むスプレイ装置を提案する。

【解決手段】 スプレイ装置のノズル膜を製造する方法は、基板(11)を設けるステップと、前記基板(11)上に膜層(13)を形成するステップと、前記膜層(13)内に複数のノズル(14)を形成するステップと、基板(10)内に複数の供給通路(15)を形成するステップとを含む。各供給通路(15)は、前記複数のノズルに含まれる個々のノズル(14)にほぼ直交して配置し、個々のノズル(14)と直接接触させる。

(もっと読む)

プラズマ処理装置

【課題】 低誘電率膜(Low-k膜、例えばSiOCH)において、膜ダメージを発生せず、高選択比で高精度なエッチングを実現可能な処理条件を提供する。

【解決手段】 BARCエッチングステップにてパターン寸法よりも溝又は孔を細く加工し、N2またはO2を含む高マスク選択比条件にてエッチングを行う。その後N2またはO2を含まず、ウエハに印加するバイアス出力を低下させて等方的なエッチングを行う、又はパターン寸法よりも溝又は孔をやや細く加工するN2またはO2を含む高マスク選択比条件と、N2またはO2を含まず、ウエハに印加するバイアス出力を低下させて等方的なエッチングを周期的に行う。

(もっと読む)

半導体装置の製造方法

【課題】デュアルダマシン法による解像限界以下の溝(トレンチ)及び凹部(孔又はビア)のパターンをCD値を高精度に形成することができる半導体装置の製造方法を提供する。

【解決手段】被エッチング層上に、第1のハードマスク膜と、第2のハードマスク膜とを成膜する成膜工程S11と、第1のピッチを有し、第2のハードマスク膜よりなるパターンであって、溝のパターンを形成する際のエッチングマスクとなる溝形成用マスクパターンを形成するための第1の溝形成用マスクパターン形成工程S12〜S14と、第4のピッチで設けられた開口部を有する第2のレジスト膜と、第2のレジスト膜の開口部と連通し、第2のレジスト膜の開口部の寸法より小さい寸法の開口部を有する第1の有機膜とよりなる第2レジストパターンを用いて、第1のハードマスク膜をエッチングする第1の凹部形成用マスクパターン形成工程S15〜S18とを有することを特徴とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】有機シロキサンを主成分とする絶縁膜にエッチング処理によって凹部を形成する際に、凹部の底部に異常形状が形成されるのを抑制する。

【解決手段】層間絶縁膜を構成する有機シロキサンを主成分とする有機絶縁膜2に形成された溝や孔等のような凹部4内に導体膜を埋め込むことで埋込配線構造を構成する半導体集積回路装置の製造方法において、有機絶縁膜2上にフォトレジスト膜3を形成した後、そのフォトレジスト膜3をエッチングマスクとして有機絶縁膜2に溝や孔等のような凹部4を形成する際に、その凹部4の底部に異常形状が形成されるのを抑制するために、CF系のガス/N2/Arガスを用いたプラズマドライエッチング処理を施すことにより凹部4を形成した。

(もっと読む)

3次元マルチゲートMOSFETの製造に有用であるバルクシリコンウェハー製品

3次元トランジスタの製造に用いられる半導体構造の作製方法を提供する。この半導体構造は、シリコン基板およびエピタキシャル層を備え、このエピタキシャル層は終点検出エピタキシャル領域を備え、この終点検出エピタキシャル領域は、炭素、ゲルマニウム、またはそれらの組み合わせからなる群から選択される終点検出不純物を含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】、デュアルダマシン法により低誘電率膜に埋め込まれた配線層を形成する場合において、オープン不良の発生を伴うことなく、設計通りの配線層を形成し得る半導体装置の製造方法を提供する。

【解決手段】ビアホール形成領域の低誘電率膜42、第1のハードマスク44及び第2のハードマスク46を除去することにより、低誘電率膜42にビアホール52を形成する工程と、配線トレンチ形成領域の第2のハードマスク46を除去する工程と、第2のハードマスク46をマスクとして第1のハードマスク44をエッチングすることにより、配線トレンチ形成領域の第1のハードマスク44を除去する工程とを有し、配線トレンチ形成領域の第1のハードマスク44を除去する工程では、ビアホール52底のバリア膜40をもエッチングすることにより、ビアホール52底のバリア膜40を部分的に除去する。

(もっと読む)

貼り合わせウェーハの製造方法

【課題】本発明の目的は、酸素イオン注入層が不連続な場合であっても、活性層の、膜厚均一性の確保及び欠陥発生の抑止が可能となる貼り合わせウェーハの製造方法の提供することにある。

【解決手段】酸素イオン層形成工程(図1(a))と、貼り合わせる工程(図1(b))と、熱処理工程(図示せず)と、活性層用ウェーハ除去工程(図1(c))と、酸素イオン注入層露出工程(図1(d))と、活性層露出工程(図1(e))とを有し、前記酸素イオン注入層露出工程は、所定条件下でドライエッチングにより行われることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】MONOS型のゲート電極を有するメモリセルと、通常のMOSトランジスタの各ゲート電極を同時に加工できるようにする。

【解決手段】メモリセル領域のゲート電極Gは、シリコン基板1上にゲート絶縁膜4、トラップ膜5、ブロック膜6、電極膜7が積層されている。周辺回路領域のゲート電極GPは、シリコン基板1上にゲート絶縁膜4、多結晶シリコン膜9、電極膜7が積層されている。また、多結晶シリコン膜9中には、下層側にシリコン窒化膜10、上層側にシリコン酸化膜11が直接接触しないように形成されている。ゲート一括加工時に、電極膜7をエッチングするときにシリコン酸化膜11がストッパとなり、ブロック膜6加工時にシリコン窒化膜10がストッパとなり、トラップ膜5加工時に多結晶シリコン膜9がストッパとなり、シリコン基板1がダメージを受けるのを防止できる。

(もっと読む)

半導体装置の製造方法

【課題】研磨粒子によるパターン形成不良を抑制して、高い歩留まりでデュアルダマシン配線を形成可能な半導体装置の製造方法を得ることを目的とする。

【解決手段】本発明における半導体装置の製造方法は、半導体基板1の上面上に絶縁膜6、配線溝パターン8を形成したハードマスク7を形成する。次に、配線溝パターン8を埋め込むように第1のレジスト膜9を形成し、ハードマスク7上の第1のレジスト膜9を除去して平坦化する。次に、第1のレジスト膜9の表面を除去し、第1のレジスト膜9の表面を洗浄する。次に、接続孔パターン14を形成した第2のレジスト膜13を形成し、第1のレジスト膜9および絶縁膜6の表層に接続孔パターン14を転写する。次に、ハードマスク7の配線溝パターン8をマスクとして、絶縁膜6をエッチングして配線溝8および接続孔14を形成する。次に、絶縁膜6に形成された配線溝8および接続孔14に金属を埋め込む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】コンタクト抵抗の上昇を防止することが可能な半導体装置の製造方法および半導体装置を提供すること。

【解決手段】シリコン基板1上に第1アモルファスカーボン膜24を形成する工程と、第1アモルファスカーボン膜24上にBPSG膜13を形成する工程と、BPSG膜13上に第2アモルファスカーボン膜16を形成する工程と、第2アモルファスカーボン膜16をパターニングし、第2アモルファスカーボン膜16をハードマスクとしてBPSG膜13を第1アモルファスカーボン膜24が露出するまでエッチングする工程と、露出した第1アモルファスカーボン膜24および第2アモルファスカーボン膜16をアッシングする工程とを備える。第1アモルファスカーボン膜24がエッチングストッパ層として作用する。よってシリコン基板1がオーバーエッチングによりダメージを受けることが防止される。

(もっと読む)

半導体素子の金属配線及びその形成方法

【課題】埋め込み金属配線の形成時に、イン-サイチュウ(in-situ)で平坦化を行うことができ、層間絶縁膜形成の回数を減らし、製造工程にかかる時間及び費用を減らすことができる半導体素子の製造方法を提供する。

【解決手段】半導体基板100上の第1の層間絶縁膜102にコンタクトプラグ104を形成する。第1の層間絶縁膜及びコンタクトプラグの上部にエッチング停止膜106a及びハードマスクパターンを形成する。ハードマスクパターンに沿ってエッチング停止膜をパターニングし、露出された第1の層間絶縁膜及びコンタクトプラグをエッチングしてコンタクトプラグの上部の第1の層間絶縁膜にトレンチを形成する。金属膜を形成後、エッチング停止膜までシリカ研磨剤とセリア研磨剤を混合したスラリーを用いて平坦化を行い、金属配線114aを形成する。エッチング停止膜を除去し、第2の層間絶縁膜116を形成する。

(もっと読む)

基板加工方法および接地部付き基板

【課題】エッチング加工用マスクを基板の表面に形成する回数を削減する。

【解決手段】基板10と、基板10の表面10pに形成されたGND部12と、基板10の裏面に形成された導電層14(例えば、Ni)と、基板10および導電層14を貫通する貫通孔14a、10cと、貫通孔14a、10cの内面ISと導電層14の表面14pを覆う導電性部材16とを備えた接地部付き基板1であって、導電層14のエッチングレートは、基板10のエッチングレートよりも小さく、導電層14の裏面14qが、導電層14の表面14pと対向し、基板10の裏面に接している。

(もっと読む)

ドライエッチング終点検出方法

【課題】コンタクトのホール加工等におけるドライエッチングにおいて、エッチング対象のパターン占有率が微小であっても、エッチング終点を安定して検出することができる技術を提供する。

【解決手段】ドライエッチング終点検出方法であって、コンタクトホール等のドライエッチング工程において、プラズマ発光のスペクトル分析を利用するものである。そして、2波長の発光強度比の時系列データを二次微分演算して第2変極点(just2)402でエッチング終点を検知することにより、エッチング終点検出の安定化を達成する。また、異常放電を同時に検出することにより、外乱を排除し、エッチング終点検出の安定化を達成する。

(もっと読む)

ナノ構造処理のための導電性補助層の形成及び選択的除去

一又は複数のナノ構造の作成方法が開示されており、当該方法は:基板の上部表面上に導電層を形成すること;導電層上に触媒のパターン層を形成すること;触媒層上に一又は複数のナノ構造を成長させること;及び一又は複数のナノ構造の間及び周囲の導電層を選択的に除去することを含んでなる。デバイスもまた開示されており、該デバイスは、基板、ここで基板は一又は複数の絶縁領域によって隔てられた一又は複数の露出金属島を含んでなる;一又は複数の露出金属島又は絶縁領域の少なくともいくつかを覆う基板上に配された導電性補助層;導電性補助層上に配された触媒層;及び触媒層上に配された一又は複数のナノ構造を含んでなる。 (もっと読む)

半導体装置の製造方法

【課題】ビアファースト方法を用いるデュアルダマシン配線の形成において、レジストポイズニングを抑制する。

【解決手段】半導体装置の製造方法は、基板101上に層間絶縁膜108を形成する工程(a)と、層間絶縁膜108にビアホール109を形成する工程(b)と、ビアホール109内にダミープラグ111を形成する工程(c)と、工程(c)の後、層間絶縁膜108上に第1のバリア絶縁膜120を形成し、更にその上に反射防止膜105を形成するする工程(d)と、第1のバリア絶縁膜120上に、配線溝形成用開口114を有するレジストマスク113を形成する工程(e)と、レジストマスク113をマスクとして層間絶縁膜108、第1のバリア絶縁膜120及びダミープラグ111のそれぞれ一部を除去することにより、ダミープラグ111の残存部分に接続する配線溝を形成する工程(f)とを有する。

(もっと読む)

半導体装置

【課題】高い耐電圧特性、および耐リーク特性を有する配線構造を備える半導体装置、およびその製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置は、半導体素子が設けられた半導体基板と、前記半導体基板上に形成された、上下層の導電部材を電気的に接続する接続部材と、前記接続部材と同じ層に形成された第1の絶縁膜と、前記接続部材の上面の一部と接する第1の領域、および前記第1の領域上に位置し、前記第1の領域よりも幅の広い第2の領域を含む配線と、前記第1の絶縁膜上に、前記配線の前記第1の領域の側面の上側から少なくとも一部、および前記第2の領域の底面に接して形成された第2の絶縁膜と、を有する。

(もっと読む)

パターン形成方法

【課題】微小パターン形成後にマスクを剥離することのできるパターン形成方法を提供する。

【解決手段】本発明の実施の形態によるパターン形成方法は、被処理体上に、第1のC含有膜と、並列配置された所定の方向に長手方向を有する第1の無機層のパターンと、を積層する工程と、前記第1のC含有膜および前記第1の無機層のパターン上に、第2のC含有膜と、少なくとも一部が並列配置されて前記第1の無機層のパターンと交差する第2の無機層のパターンと、を積層する工程と、前記第1および第2のC含有膜の、前記第1および第2の無機層のパターンの少なくとも一方の略直下以外に位置する領域をエッチングにより除去し、前記第1および第2の無機層のパターンならびにエッチング加工された前記第1および第2のC含有膜を含むエッチングマスクを形成する工程と、前記エッチングマスクを用いて前記被処理体にエッチングを施し、前記被処理体のパターンを形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタの性能向上を図ってスペーサを形成できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、ゲートを覆って、半導体基板上に、高誘電体材料を含むバリア絶縁膜を形成する工程と、バリア絶縁膜上に、スペーサ絶縁膜を形成する工程と、スペーサ絶縁膜を、異方性エッチングして、ゲートの側壁上にスペーサを残して除去する工程と、露出したバリア絶縁膜を除去する工程と、ゲート及びスペーサをマスクとして、半導体基板に不純物を注入し、エクステンションを形成する工程と、さらにサイドウォールを形成し、ゲート、スペーサ、及びサイドウォールをマスクとして、ソース/ドレイン領域を形成する工程とを有する。

(もっと読む)

41 - 60 / 168

[ Back to top ]