Fターム[5F005GA02]の内容

Fターム[5F005GA02]に分類される特許

1 - 14 / 14

窒化ガリウム結晶、ホモエピタキシャル窒化ガリウムを基材とするデバイス、及びその製造方法

【課題】ホモエピタキシャルLED、LD、光検出器又は電子デバイスを形成するために役立つGaN基板の形成方法の提供。

【解決手段】約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板上に配設された1以上のエピタキシャル半導体層を含むデバイス。かかる電子デバイスは、発光ダイオード(LED)及びレーザーダイオード(LD)用途のような照明用途、並びにGaNを基材とするトランジスター、整流器、サイリスター及びカスコードスイッチなどのデバイスの形態を有し得る。また、約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板を形成し、該基板上に1以上の半導体層をホモエピタキシャルに形成する方法及び電子デバイス。

(もっと読む)

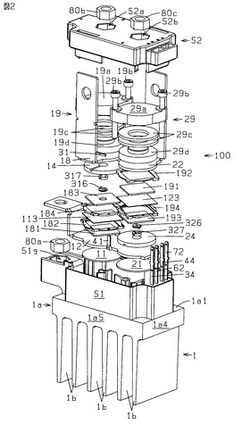

圧接型大電力用サイリスタモジュールおよびその製造方法ならびにその使用方法

【課題】水冷設備を準備できない使用環境でサイリスタチップを冷却する。

【解決手段】サイリスタチップ113,123を具備する圧接型大電力用サイリスタモジュール100において、複数の放熱フィン1bを有するヒートシンク1のベース部分1aに対して絶縁板11とコモンバー12とアノードサブスペーサ181とサイリスタチップ113とカソードサブスペーサ183とカソードスペーサ14とカソード端子バー18とを圧接手段19によって上下方向に圧接し、ヒートシンク1のベース部分1aに対して絶縁板21とコモンバー12とカソードスペーサ24とカソードサブスペーサ193とサイリスタチップ123とアノードサブスペーサ191とアノード端子バー22とを圧接手段29によって上下方向に圧接した。

(もっと読む)

半導体装置

【課題】トライアックが形成された半導体装置の性能を向上させる。

【解決手段】トライアック形成用の半導体領域が形成された半導体基板1の表面に電極T1,G1が形成され、裏面に裏面電極が形成されている。電極T1から裏面電極へ電流を流す場合と、裏面電極から電極T1へ電流を流す場合の両方の動作モードにおいて、ゲート端子である電極G1に電極T1よりも高電位の電圧を印加することで、半導体基板1に形成されたサイリスタをターンオンする。半導体基板1の表面側には、p型半導体領域P2とそれに内包されるn型半導体領域N2とが形成され、電極T1はp型半導体領域P2とn型半導体領域N2に接し、電極G1はp型半導体領域P2のみに接する。そして、平面視において、電極G1が接する部分のp型半導体領域P2と電極T1が接する部分のp型半導体領域P2の間に、n型半導体領域N2が延在している。

(もっと読む)

半導体装置

【課題】例えばSIThyに適用した場合に、ゲート電極とカソード電極との短絡を防止すると共に、ゲート電流の増大、チャネル領域の面積の拡大を図る。

【解決手段】半導体基板12の一主面に複数のランド20と複数のグルーブ22が形成されている。ランド20の表面部にカソード領域24が形成され、グルーブ22の底部にゲート領域26が形成されている。グルーブ22内にゲート電極16が形成され、ランド20の上面にカソード電極14が形成されている。ランド20の上面とグルーブ22の底面にわたって絶縁膜28が形成されている。カソード電極14の側面とゲート電極16と絶縁膜28とを覆うように層間絶縁膜30が形成され、カソード電極14上面と層間絶縁膜30とを覆うように接続電極32が形成されて各カソード電極14が電気的に接続されている。グルーブ22の側壁とゲート電極16の側壁との間に絶縁膜28のみが介在している。

(もっと読む)

圧接型GTOサイリスタ

【課題】均一なターンオフ動作をさせ、ターンオフ動作の失敗による素子の破壊を抑制可能な圧接型GTOサイリスタを提供することを目的とする。

【解決手段】本発明にかかる圧接型GTOサイリスタは、半導体基体12と半導体基体12上に平面視環状に配置されてカソード電極18を形成するエレメントパターンと、環状の中央近傍において、半導体基体12上に圧接されたゲート電極38と、ゲート電極38の所定方向の側面に接続されたゲートリード44とを備え、環状の中心位置である第1平面中心Aが、ゲート電極38の平面視における中心位置である第2平面中心Bに対し、所定方向にずれて位置する。

(もっと読む)

圧接型半導体装置

【課題】外部圧接電極体と半導体基体との間に形成された空間に異物が混入することを防止しつつ、コーティング体の剥がれを防止することができる圧接型半導体装置を提供する。

【解決手段】半導体基体1の主面の一面及び外部圧接電極体の互いの対向面を半導体基体1の外側から囲むように外部圧接電極体の外周面とコーティング体5との間にまたがって配置され、変形することによりコーティング体5にかかる荷重がコーティング体5を半導体基体1から剥がすのに要する荷重以下となる状態を維持した密閉体25を備えた。

(もっと読む)

圧接型半導体装置

【課題】主電極にめっきを施しつつ、主電極の端部を含む面に圧接電極を面接合させることができる圧接型半導体装置を提供する。

【解決手段】半導体基体12と、めっき処理され、該半導体基体12の主面に固着されためっき付き主電極22と、該めっき付き主電極22のめっき22aが形成された面に重なるように圧接された圧接電極と、を備える。そして、該めっき付き主電極22の側面には溝22bが形成され、該溝22bは、該半導体基体12と該めっき付き主電極22が重なる部分の直上領域より外側に形成されたことを特徴とする。

(もっと読む)

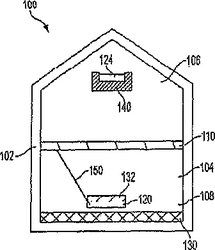

半導体装置の製造方法

【課題】製造工程中に半導体基板に発生する欠陥を低減し、逆方向リーク電流を小さくすることが容易な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板110を準備する半導体基板準備工程と、半導体基板110の第2主面にn型不純物を導入する不純物導入工程と、半導体基板110の第1主面にバリアメタル113を形成する金属薄膜形成工程と、半導体基板110の第2主面側から光エネルギーを照射して半導体基板110をバリアメタルの全部又は一部がシリサイド化される温度に加熱することで、不純物を活性化するとともに、バリアメタルの全部又は一部をシリサイド化するランプアニール工程とをこの順序で含む。

(もっと読む)

圧接型大電力用サイリスタモジュール

【課題】圧接型大電力用サイリスタモジュールの上下方向寸法を小型化する。

【解決手段】放熱板1、絶縁板11、コモンバー12、スペーサ181、サイリスタチップ113、スペーサ183,24及びカソード端子バー18を圧接手段19により上下方向に圧接する。四角形のサイリスタチップ113を用い、四角形のスペーサ181,183をサイリスタチップ113よりも小さくする。絶縁性ホルダ182,184とによってスペーサ181,183とを包囲する。サイリスタチップ113のゲート電極113b上に配置されたコイルバネ型ゲート電極信号線15のコイル部分15aとスペーサ14とを絶縁性ゲートスペーサ316,317によって絶縁する。コイルバネ型ゲート電極信号線15の水平方向に延ばされた部分15bを絶縁被覆し、スペーサ14の収容溝14b内に収容する。水平方向に延ばされた部分15bの根元側部分15b2を絶縁性ゲートスペーサ316,317によって狭持する。

(もっと読む)

サイリスタ

【課題】 本発明の目的は良好なdV/dt−VCL特性を得る。

【解決手段】 第1導電型のエミッタ層2と、前記第1導電型と反対の第2導電型のベース層3と、前記第1導電型のバルク層5と、前記第2導電型の対面ベース層6とが順に平行的に配置され、前記ベース層および前記バルク層間に、該バルク層より高濃度の第1導電型の埋め込み層4が配置されたサイリスタ1において、前記埋め込み層は、前記ベース層と接する面を第1接合面および前記バルク層と接する面を第2接合面とするとき、該第2接合面の端が前記第1接合面に向かって傾斜を有して接し、かつ前記第1接合面の端が前記第2接合面の端に向かって所定の傾斜を有することを特徴とする。

(もっと読む)

電界効果トランジスタおよびサイリスタ

【課題】耐圧の低下を可及的に防止することを可能にする。

【解決手段】SiCからなるドレイン領域2と、ドレイン領域上に設けられたn型のSiCからなるドリフト層4と、ドリフト層の表面に設けられたn型のSiCからなるソース領域18と、ソース領域の側部のドリフト層の表面に設けられたSiCからなるチャネル領域12aと、チャネル領域上に設けられた絶縁ゲート22と、ソース領域の底部とドリフト領域との間に設けられ2種類のp型不純物を含むp型のベース領域15と、を備えている。

(もっと読む)

高耐熱合成高分子化合物及びこれで被覆した高耐電圧半導体装置

【課題】150℃以上の高温で使用するSiCなどのワイドギャップ半導体装置において、ワイドギャップ半導体素子の絶縁性を改善し、高耐電圧のワイドギャップ半導体装置を得る。

【解決手段】ワイドギャップ半導体素子の外面を、合成高分子化合物で被覆する。この合成高分子化合物は、シロキサン(Si−O−Si結合体)による橋かけ構造を有する1種以上の有機珪素ポリマーAとシロキサンによる線状連結構造を有する1種以上の有機珪素ポリマーBとをシロキサン結合により連結させた有機珪素ポリマーC同士を、付加反応により生成される共有結合で連結させて三次元の立体構造に形成している。この合成高分子化合物に高い熱伝導性を有する絶縁性セラミックスの微粒子を混合し、熱伝導率を高くしている。

(もっと読む)

窒化ガリウム結晶、ホモエピタキシャル窒化ガリウムを基材とするデバイス、及びその製造方法

約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板上に配設された1以上のエピタキシャル半導体層を含むデバイス。かかる電子デバイスは、発光ダイオード(LED)及びレーザーダイオード(LD)用途のような照明用途、並びにGaNを基材とするトランジスター、整流器、サイリスター及びカスコードスイッチなどのデバイスの形態を有し得る。また、約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板を形成し、該基板上に1以上の半導体層をホモエピタキシャルに形成する方法及び電子デバイスも提供される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 水分の浸入や汚染物質の侵入を防止し、長期間の使用に対する電気的信頼性を向上することができ、更に外部応力に対する半導体素子の損傷を防止し、半導体素子の電気的特性の変化を防止することができる半導体装置を提供する。

【解決手段】 樹脂封止型半導体装置において、支持基板1上にベベル端面を有する半導体素子4、例えばダイオードが取り付けられ、この半導体素子4上に中間接続導体6が取り付けられている。中間接続導体6の幅寸法(直径寸法)L3は半導体素子4の第2の主電極44の幅寸法(直径寸法)L2以上に設定されている。中間接続導体6の周縁部分を第2の主電極44の周縁部分よりも突出させたことによって、半導体素子4のベベル端面45上には、中間接続導体6の表面上の一部に渡る広範囲で保護樹脂10を形成することができる。

(もっと読む)

1 - 14 / 14

[ Back to top ]