Fターム[5F032DA10]の内容

Fターム[5F032DA10]に分類される特許

1 - 20 / 151

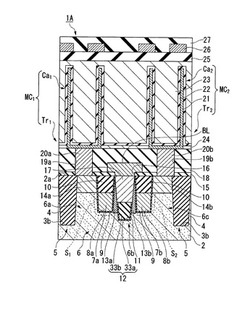

半導体装置及びその製造方法、並びにデータ処理システム

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、2つの埋め込みゲート用の溝部8a,8bによって分断された3つの活性領域6a,6b,6cのうち、中央部に位置する活性領域6bを分断するビットコンタクト用の溝部11の両側面に、埋め込みゲート用の溝部8a,8bの底面と同程度の深さで不純物を拡散させることによって形成された第1の不純物拡散層13a,13bと、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

トレンチ埋め込み用樹脂組成物

【課題】基体に形成されたトレンチ内に酸化シリコンを埋め込むために使用するのに好適なトレンチ埋め込み用樹脂組成物を提供すること。

【解決手段】本発明に係るトレンチ埋め込み用樹脂組成物は、酸化シリコン粒子をトレンチ埋め込み用樹脂組成物全体に対して0.35重量%以上2.20重量%以下で、並びに、一般式(1)〜(3)で表される化合物の合計に対して、一般式(1):Si(OR1)4で表されるテトラアルキシキシラン化合物を45mol%以上87mol%以下で、一般式(2):R2Si(OR1)3で表されるトリアルコキシシラン化合物を10mol%以上50mol%以下で、そして一般式(3):R22Si(OR1)2で表されるジアルコキシシラン化合物を1.5mol%以上3.6mol%以下で含有する。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

硬化性組成物、トレンチ埋め込み方法、硬化膜および半導体発光素子

【課題】塗布法により幅の広いトレンチに埋め込みを行った場合にも、ディンプルが生じず、はがれやにごりなどなく、均質で、平坦な表面を有する硬化膜を形成することができる硬化性組成物を提供する。

【解決手段】以下の(A)成分〜(C)成分を含有することを特徴とする硬化性組成物。(A)成分:脱離基を有するエポキシ基含有ポリシロキサンであり、該ポリシロキサン中に含まれる全Si原子の数を100mol%とするとき、前記脱離基の含有割合が35mol%以下であるエポキシ基含有ポリシロキサン。(B)成分:シリコーン系界面活性剤。(C)成分:溶剤。

(もっと読む)

絶縁膜の形成方法

【課題】均一で高い充填密度を有し、かつ欠陥が少ない絶縁膜を形成することができる方法の提供。

【解決手段】基板表面に、二酸化ケイ素微粒子と、ポリマーと、界面活性剤と、分散媒とを含む二酸化ケイ素分散液を塗布し、次いでポリシラザン組成物を塗布した後、加熱して絶縁膜を形成させる、絶縁膜の形成方法。

(もっと読む)

半導体装置の製造方法

【課題】塗布法を用いて形成される酸化膜を溝の内部に充填した溝型の素子分離部を有する半導体装置において、溝の内部におけるボイドの発生を抑制して、埋め込み不良を低減することのできる技術を提供する。

【解決手段】0.2μm以下の溝幅を有する溝4Sの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも高く、かつ1.0μm以上の溝幅を有する溝4Lの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも低くなるように、半導体基板1の主面上にポリシラザン膜を形成し、続いて、300℃以上の熱処理を行うことにより、ポリシラザン膜を酸化シリコン(SiO2)からなる第1埋め込み膜8へ転化すると同時に、溝4Sの上部に局所的に生じたボイドを消滅させる。

(もっと読む)

半導体装置およびその製造方法

【課題】デバイス特性に優れた半導体装置およびその製造方法を提供する。

【解決手段】実施の一形態の半導体装置は、第1および第2の領域を有する機能膜と、前記基板の前記第1の領域に設けられ、第1の幅を有する第1の溝と、前記基板の前記第2の領域に設けられ、第1の幅よりも広い第2の幅を有する第2の溝と、前記第1の溝を埋めるように高分子材料を前駆体として形成された第1の絶縁膜と、前記第1の幅を上回る直径を有し、前記第2の溝を埋める微粒子と、前記第2の溝内で前記微粒子間および前記微粒子と前記第2の溝との間隙を埋める前記高分子材料とを前駆体として形成された第2の絶縁膜とを持つ。

(もっと読む)

シリカ系絶縁膜形成用塗布液

【課題】ポットライフが長く、焼成してシリコン酸化物としたときの硬化収縮率が小さく、更にクラック耐性に優れかつ耐電圧のばらつきが小さい絶縁膜を形成できる縮合反応物溶液の提供。

【解決手段】(I)(i)下記一般式(1):R1nSiX14-n (1){式中、nは0〜3の整数であり、R1は水素原子又は炭素数1〜10の炭化水素基であり、X1はハロゲン原子、炭素数1〜6のアルコキシ基又はアセトキシ基である}で表されるシラン化合物に由来するポリシロキサン化合物と、(ii)シリカ粒子と、を少なくとも含有する縮合成分を縮合反応させて得られる縮合反応物、及び(II)溶媒を含み、該一般式(1)で表されるシラン化合物が4官能シラン化合物及び3官能シラン化合物を少なくとも含有し、該シリカ粒子中の炭素量が0.05質量%以上0.65質量%未満である、縮合反応物溶液。

(もっと読む)

トレンチ埋め込み方法、及びトレンチ埋め込み用組成物

【課題】高アスペクト比のトレンチ内に埋め込んだ際に、クラック、及びボイドが生じにくく、かつ高密度に埋め込むことができるトレンチ埋め込み方法。

【解決手段】(1)トレンチ2を有する基体1上に、シロキサン系重合体、空孔形成剤、及び有機溶媒を含むトレンチ埋め込み用組成物を、少なくとも該組成物が前記トレンチ内に充填されるように塗布し、塗膜3を形成する工程、及び、(2)工程(1)で得られた塗膜3に加熱処理および光処理の少なくともいずれか一方を行う工程、を含むトレンチ埋め込み方法。

(もっと読む)

シャロートレンチアイソレーション膜のためのアミノシラン

【課題】記憶及び論理回路を含む半導体基材、例えば、1つ又は複数の集積回路構造をその上に有するシリコンウェハにおいて用いられるシャロートレンチアイソレーションのための高アスペクト比の特徴のギャップを充填するための酸化条件下で二酸化ケイ素含有膜をスピンオン堆積させる方法を提供する。

【解決手段】高アスペクト比の特徴を有する半導体基材を用意する工程、該半導体基材を低分子量のアミノシランを含む液体配合物と接触させる工程、該半導体基材上に該液体配合物を塗布することにより膜を形成する工程、及び該膜を酸化条件下において高温で加熱する工程を含む方法が提供される。この方法のための組成物もまた記載される。

(もっと読む)

アイソレーション構造の形成方法

【課題】収縮率および引っ張り応力の低いアイソレーション構造の形成方法の提供。

【解決手段】基板表面に多孔質化剤を含む第1のポリシラザン組成物を塗布および焼成して、屈折率が1.3以下の多孔質シリカ質膜を形成させ、次いでその膜の表面に第2のポリシラザン組成物を含浸させ、焼成することにより、屈折率1.4以上のシリカ質膜からなるアイソレーション構造を形成させる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域となるSOI構造を有する半導体線条突出部の形状のばらつきを抑制し、トランジスタ特性のばらつきを減少することができる半導体装置を提供する。

【解決手段】半導体基板1の素子分離用の溝に埋込み絶縁膜が埋め込まれてなる素子分離領域2と、素子分離領域2によって区画されてなり、素子分離用の溝を区画する側壁面と半導体基板の1一面とを有し、かつ側壁面には埋込み絶縁膜に向けて突出した半導体線条突出部1aが素子分離用の溝に沿って設けられてなる活性領域Tと、半導体線条突出部1aを残して活性領域Tを分断するように設けられたゲート電極用のゲート溝3と、ゲート溝3の内面に形成されたゲート絶縁膜4と、ゲート溝3に埋め込まれたゲート電極5と、ゲート電極5のゲート長方向両側の活性領域Tにそれぞれ形成され、半導体線条突出部1aによって連結される不純物拡散領域7と、を具備してなることを特徴とする。

(もっと読む)

素子分離材料用塗布液、素子分離材料用塗布液の作製方法、素子分離層用薄膜、及び、素子分離層用薄膜の形成方法

【課題】絶縁破壊電圧の高い素子分離層を形成することができる素子分離材料用塗布液等を提供する。

【解決手段】素子分離材料用塗布液は、一般式(I)で表される構造単位からなる骨格を有するポリシラザン等と、酸化物を形成できる金属元素を含む化合物と、溶媒とを備えている。金属元素は、チタン、ジルコニウム、ハフニウム、又は、タンタルであり、ポリシラザン等のSiのモル数に対し、0.5mol%〜19mol%となるように添加されている。 (もっと読む)

(もっと読む)

有機トランジスタ及び有機トランジスタの製造方法

【課題】導体層におけるソース電極とドレイン電極との電極間のチャネル領域が結晶相であり、且つ該半導体層における該チャネル領域以外の第2の領域が非結晶相である構成ではない場合に比べて、半導体素子間の電気的な分離が実現された有機トランジスタを提供する。

【解決手段】有機トランジスタ10は、基板12上に、ゲート電極14G、ゲート絶縁膜16、ソース電極18S及びドレイン電極18D、及び半導体層20が設けられている。半導体層20における、ソース電極18S及びドレイン電極18Dとの電極間の領域であるチャネル領域20Aは、結晶相とされている。また、半導体層20における、このチャネル領域20A以外の第2の領域20Bは、非結晶相とされている。

(もっと読む)

シングルゲートフィンFET及びその製造方法

【課題】新規なFinFET構造及びその製造方法を提供する。

【解決手段】シングルゲートフィンFET構造100は、2つの拡大された頭部、及び当該拡大された頭部と下層の超薄型ボディとを連結する2つの徐々に細くなる首部を有するアクティブフィン構造を含む。2つのソース/ドレイン領域102,104が、2つの拡大された頭部にそれぞれドープされる。絶縁領域26が、2つのソース/ドレイン領域の間に挿入される。溝分離構造24が、音叉形状のフィン構造の一方の側に配置される。片面サイドウォールゲート電極12bが、アクティブフィン構造における、溝分離構造とは反対側の垂直なサイドウォールに配置される。

(もっと読む)

トレンチ埋め込み用組成物

【課題】基板表面上のナノメートルレベルの開口幅を有し、アスペクト比が大きいトレンチ(溝)への埋め込み性に優れ、ボイドなどの欠陥の発生が抑制され、電気的絶縁性に優れたアイソレーション構造を製造するのに好適なトレンチ埋め込み用組成物、および該組成物を用いたトレンチ・アイソレーション構造の製造方法の提供。

【解決手段】アルキルトリアルコキシシランを50モル%以上含むアルコキシシラン原料を加水分解、縮合して得られる加水分解縮合物を含有し、該加水分解縮合物の重量平均分子量が1000〜50000であり、該加水分解縮合物の含有量が組成物全量に対して14質量%超30質量%以下であるトレンチ埋め込み用組成物の塗膜14により、基板10表面上に形成されたトレンチ12を埋め込む。

(もっと読む)

ポリシロキサン縮合反応物を用いたトレンチ埋め込み用絶縁膜の形成方法

【課題】基板に形成された開口幅が狭く高アスペクトなトレンチ内に埋め込むために好適な縮合反応物溶液であって、ポットライフが長く、トレンチ埋め込み用として使用した場合のトレンチ内への埋め込み性が良好で、焼成して酸化シリコンとしたときの硬化収縮率が小さく、クラック耐性及びHF耐性に優れる縮合反応物溶液を用いる絶縁膜の形成方法を提供する。

【解決手段】半導体素子に形成されたトレンチ埋め込み用絶縁膜の形成方法であって、特定構造のシラン化合物に由来するポリシロキサン化合物と、シリカ粒子とを含有する縮合成分から得られる縮合反応物、及び溶媒を含み、該シラン化合物が4官能シラン化合物及び3官能シラン化合物を含有する縮合反応物溶液を、基板上に塗布して塗布基板を得る塗布工程と、該塗布工程で得た塗布基板を加熱する焼成工程とを含むトレンチ埋め込み用絶縁膜の形成方法。

(もっと読む)

半導体装置及びその製造方法

【課題】工程マークやアライメントマーク等を形成するトレンチ内のSOG膜にクラックが発生した場合に、そのクラックが素子形成領域に到達するのを防止する。

【解決手段】半導体基板10の素子形成領域10Tの外側において、工程マーク30Cは、トレンチ31のパターンで形成されている。素子形成領域10Tと、その外側のトレンチ31は層間絶縁膜21に覆われており、層間絶縁膜21は、トレンチ31内を埋めるSOG膜22に覆われている。さらに、半導体基板10の表面上には、トレンチ31及びトレンチ31上のSOG膜22を囲む環状ポリシリコン膜18が形成されている。

(もっと読む)

素子分離材料用塗布液の作製方法、素子分離材料用塗布液、素子分離層用薄膜、素子分離層用薄膜の形成方法、基板、及び、基板の形成方法

【課題】基板と素子分離層との剥離やクラックが発生し難く、凹状の溝を有する基板上に平坦な素子分離層を形成することができる素子分離材料用塗布液の作製方法等を提供する。

【解決手段】半導体装置のシャロートレンチアイソレーション構造の素子分離層の形成に用いられる素子分離材料用塗布液の作製方法は、混合液作製工程と絶縁膜形成前駆体作製工程と塗布液作製工程とを備えている。混合液作製工程では、炭素数2〜6個のアルコキシル基を有するアルコキシシラン化合物と第1の溶媒との混合液を作製する。絶縁膜形成前駆体作製工程では、この混合液に加水分解触媒及び水を添加し、加水分解、縮合して絶縁膜形成前駆体を作製する。水の添加量は、アルコキシシラン化合物中の全アルコキシル基1モルに対して0.3〜0.8倍モルの範囲とする。塗布液作製工程では、作製された絶縁膜形成前駆体に第2の溶媒を加え、素子分離材料用塗布液を作製する。

(もっと読む)

1 - 20 / 151

[ Back to top ]