Fターム[5F033GG02]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930) | 化合物半導体 (913) | III−V族 (485)

Fターム[5F033GG02]に分類される特許

161 - 180 / 485

半導体装置

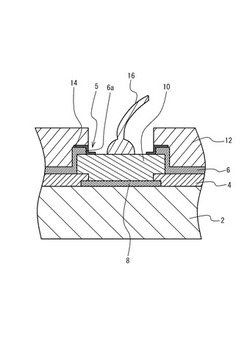

【課題】窒化シリコン膜と電極パッドとの界面から水分が浸入することを抑制し、半導体装置の信頼性を向上させること。

【解決手段】半導体層2と、半導体層2上に設けられたAuからなる電極パッド10と、電極パッド10上にその端部が位置するように、半導体層2上及び電極パッド10上に設けられた窒化シリコン膜6と、電極パッド10の上面の一部及び窒化シリコン膜6の端部に接し、かつ電極パッド10の上面の他部が露出するように設けられたTi、Ta及びPtのいずれかからなる金属層14と、を具備する半導体装置。

(もっと読む)

冷却機構を含む接合型半導体構造体とその形成方法

【課題】 冷却機構を有する接合型半導体基板を形成するための構造体、設計構造体、及びその形成方法を提供すること。

【解決手段】 2つの半導体基板を備える接合型基板が提供される。各々の半導体基板は、半導体デバイスを含む。少なくとも1つの基板貫通ビアが2つの半導体基板の間に設けられ、それらの間に単一の経路を提供する。2つの半導体基板の底側は、冷却機構を含む少なくとも1つの接合材料層によって接合される。1つの実施形態において、冷却機構は冷却チャネルであり、その中を通って冷却流体が流動し、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。別の実施形態において、冷却機構は、2つの端部とそれらの間の連続した経路を備えた導電性冷却フィンである。冷却フィンはヒートシンクに接続され、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。

(もっと読む)

半導体装置

【課題】水分の浸入による半導体装置の信頼性低下を抑制した装置の提供。

【解決手段】GaAs系半導体、InP系半導体、及びGaN系半導体のいずれかからなる半導体層2と、半導体層2上に設けられ、端部4aが半導体層2上に位置する第1窒化シリコン膜4と、第1窒化シリコン膜4の端部4aを覆うように、半導体層2上及び第1窒化シリコン膜4上に設けられたポリイミドまたはベンゾシクロブテンのいずれかからなる保護膜12と、半導体層2の上面及び第1窒化シリコン膜4の端部4aに接するように、半導体層2と保護膜12との間から第1窒化シリコン膜4の端部4aと保護膜12との間にかけて連続的に設けられた第1Ti層14と、を具備することを特徴とする半導体装置。

(もっと読む)

誘電ライン・バイアのエレクトロマイグレーション耐性が向上した界面層を有する相互接続構造およびその製造方法

【課題】 相互接続構造内にガウジング・フィーチャを導入することなくエレクトロマイグレーション耐性を向上させる相互接続構造を提供する。

【解決手段】 この構造は、バイア開口の底部に存在する金属界面層(または金属合金層)を含む。バイア開口は、第1の導電材料が埋め込まれた第1の誘電材料の上に位置する第2の誘電材料内に位置する。バイア開口の底部に存在する金属界面層(または金属合金層)は、第1の誘電体内に埋め込まれた下にある第1の導電材料と第2の誘電材料内に埋め込まれた第2の導電材料との間に位置する。また、エレクトロマイグレーション耐性が向上した相互接続構造を製造する方法も提供する。

(もっと読む)

半導体装置、半導体装置の製造方法およびスイッチ回路

【課題】トランジスタのリーク電流の低減。

【解決手段】半導体材料の表面に沿って互いに隣接する、シリサイド化される金属を含有する複数の電気素子要素と、複数の電気素子要素を覆い、電気素子要素に含まれる金属が実質的にシリサイド化しない温度で薄膜形成したシリコンを含む保護絶縁膜と、を備える半導体装置が提供される。上記半導体装置において、保護絶縁膜は、シリコンおよび窒素を含有できる。保護絶縁膜は、260℃以下の温度で薄膜形成した窒化シリコン膜であってよく、好ましくは100℃以下の温度で薄膜形成した窒化シリコン膜である。

(もっと読む)

半導体装置、半導体装置の製造方法およびスイッチ回路

【課題】トランジスタのリーク電流の低減。

【解決手段】半導体材料の表面に沿って互いに隣接する複数の電気素子要素と、複数の電気素子要素を覆う、シリコンを含まない下層保護絶縁膜と、下層保護絶縁膜の上に配置され、シリコンを含む上層保護絶縁膜と、を備える半導体装置が提供される。上記半導体装置において、複数の電気素子要素の少なくとも一つは、シリサイド化される金属を含有でき、下層保護絶縁膜は、電気素子要素に含有される金属と上層保護絶縁膜に含有されるシリコンとの接触を阻害できる。下層保護絶縁膜は、比誘電率が10以上の高誘電体層を有してよい。上層保護絶縁膜は、シリコンおよび窒素を含有することができる。

(もっと読む)

エッチング方法およびエッチング方法を用いた半導体装置の製造方法

【課題】本発明は、メタルマスクを用いて、簡易な方法により半導体基板に先細状ビア孔を形成するエッチング方法を提供することを目的とする。

【解決手段】半導体基板上に金属導電層を形成する工程と、該金属導電層上に第1の開口を有する第1メッキ層を形成する工程と、該第1メッキ層の側壁に該第1の開口より幅の狭い第2の開口を有する第2メッキ層を形成する工程と、該第2メッキ層をマスクとして第1のドライエッチングを行い該半導体基板をエッチングする工程と、該第1のドライエッチングの後に該第1メッキ層を残す選択的ウェットエッチングを行い該第2メッキ層をエッチングする工程と、該第2メッキ層をエッチングした後に該第1メッキ層をマスクとして第2のドライエッチングを行い該半導体基板をさらにエッチングする工程とを備えることを特徴とする。

(もっと読む)

GaN系LED素子およびその製造方法

【課題】p電極にTCO膜を用いたGaN系LED素子に関して、その高出力化および信頼性向上の少なくともいずれかを実現すること。

【解決手段】n型GaN系半導体層の上にGaN系半導体からなる活性層とp型GaN系半導体層とを順次積層してなり、前記p型GaN系半導体層の前記活性層側の主面とは反対側の主面上に形成されたTCO膜と該TCO膜に接続されたp側ボンディングパッドとを含むp電極と、前記TCO膜の前記p型GaN系半導体層側とは反対側の主面上の一部に形成された抵抗制御膜と、前記p型GaN系半導体層と前記TCO膜との界面に形成されて前記抵抗制御膜の下方の領域において前記活性層を流れる電流を減少させる抵抗増加領域と、前記n型層に接続されたn側ボンディングパッドと、を有するGaN系LED素子。

(もっと読む)

ギャップ充填信頼性を改良し及び容量を減少させるためのデュアル金属インターコネクト

【課題】 ギャップ充填信頼性を改良し及び容量を減少させるためのデュアル金属インターコネクトを提供する。

【解決手段】 本発明のインターコネクト形成方法は;パターン化された金属層の上に誘電層を堆積し、前記誘電層をエッチングしてトレンチ及び下置金属表面を露出するために開口部を形成し、前記前処理された開口部に、及び前記下置金属表面に直接隣接した高融点インターコネクトを形成し、前記トレンチと前記高融点インターコネクト上にバリア層とシード層を堆積し、及び前記シード層上に低抵抗金属を形成することを含む、方法である。  (もっと読む)

(もっと読む)

貫通電極形成方法

【課題】電極パッドのダメージを低減し、高信頼性の貫通電極を提供することを目的とする。

【解決手段】工程(a)〜(c)では、基板(1)の他方の面から電極パッド(5)に達する孔(1ab)を形成し、工程(d)では、孔(1ab)の内側に一端が電極パッド(5)に接触し他端が基板(1)の他方の面に達する導電経路(2)を形成し、工程(e)では、基板(1)をエッチングして導電経路(2)の周囲に凹部(1c)を形成し、更に凹部(1c)の内側で導電経路(2)の周面に絶縁膜を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

電子デバイスの製造方法

【課題】成膜時に生じる反りを緩和しうる電子デバイスの製造方法を提供する。

【解決手段】まず、4H−SiC基板10の第1面10aの上に、第1タングステン膜11を堆積する。堆積は、基板温度を400℃〜600℃に保持した状態で、スパッタによって行われる。スパッタ後に室温まで冷却すると、基板全体が上方に凹になるように反る。その後、4H−SiC基板10の第2面10bの上に、同じ材質、厚さの第2タングステン膜12を堆積する。4H−SiC基板10に対する,第1,第2タングステン膜11,12の収縮による応力が互いに釣り合い、反りがなくなる。その後、平坦な基板上にレジスト膜Reを形成して、第1タングステン膜11から注入マスク11aを形成する。正確な注入マスク11aを用いて、高い精度で不純物拡散領域15を形成する。

(もっと読む)

半導体装置の製造方法

【課題】孔のないキャリア(支持基板)を用いても、キャリアの取り外し時の半導体チップの散乱を防止することができる半導体装置の製造方法を提供する。

【解決手段】半導体素子が形成された素子形成基板の表面に、接着剤11を用いてキャリア(支持基板)12を貼り付ける。その後、素子形成基板の裏面から、素子形成基板の途中まで延びる複数のスルーホール1bを互いに離間して形成する。次に、裏面の処理として、裏面の研磨及びAu層23の形成等を行う。次に、複数のスルーホール1bを接着剤11まで到達させる。そして、複数のスルーホール1bから接着剤11の溶解液を接着剤11まで浸透させて、接着剤11を溶解させる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極のショート不良を引き起こすことなく、貫通電極とパッド電極との密着性を向上させる。

【解決手段】開口部22が設けられたパッド電極21b上にエッチストッパ膜23を積層し、半導体基板11に形成された貫通孔41に貫通電極45を埋め込む際に、貫通電極45の先端が、開口部22を介してパッド電極21bの一部を突き抜け、エッチストッパ膜23で止められるように構成する。

(もっと読む)

マイクロ電子構造体、マルチチップモジュール及びそれを含むメモリカードとシステム並びに集積回路素子の製造方法

【課題】ビア電極を効果的に配しうるマイクロ電子構造体、マルチチップモジュール、メモリカード及び集積回路素子の製造方法を提供する。

【解決手段】基板110と、前記基板上に提供され、貫通して延長される第1及び第2開口を含む導電性パッド130と、前記導電性パッド上に提供され、前記導電性パッド内の前記第1開口を貫通して前記基板内に延長される第1導電性ビア電極150と、前記導電性パッド上に前記第1導電性ビア電極に隣接するように提供され、前記導電性パッド内の前記第2開口を貫通して前記基板内に延長される第2導電性ビア電極160とを有する。

(もっと読む)

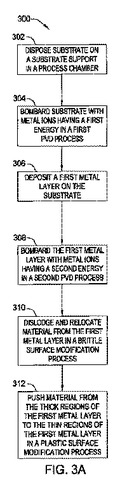

強化された銅のイオン化を伴うPVD銅シードオーバーハング再スパッタ

パターンが形成された基板上に金属を堆積させる方法および装置を提供する。金属層が,第1のエネルギーを有する物理蒸着工程で形成される。第2のエネルギーを用いて金属層上に第2の物理蒸着工程が行われ、ここで、堆積層は、脆性および塑性表面修正工程の相互作用を受け、基板上にほぼ同形の金属層が形成される。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】ガラス基板を使用したSOI基板上に形成しても、ゲート電極を形成する導電膜を成膜する際に該導電膜の加える応力により、ガラス基板上の絶縁膜及び半導体膜がはがれないような半導体装置の作製方法の提供を課題の一つとする。

【解決手段】ボンド基板上に第1の絶縁膜を形成し、ボンド基板の表面からイオンを添加することによって脆化層を形成し、ボンド基板を、第1の絶縁膜を介してガラス基板と貼り合わせ、ボンド基板を脆化層において分離してガラス基板上に第1の絶縁膜を介して半導体膜を形成し、第1の絶縁膜及び半導体膜の周辺領域を除去してガラス基板の一部を露出させ、半導体膜、第1の絶縁膜及びガラス基板上に接してゲート絶縁膜を形成し、ゲート絶縁膜上に接して2層構造の積層導電膜を形成し、2層構造の積層導電膜として、上層に引っ張り応力を有する導電膜、下層に圧縮応力を有する導電膜を用いて半導体装置を作製する。

(もっと読む)

半導体装置、パターン形成方法および半導体装置の製造方法

【課題】開口部の間口部分の拡大を抑制しつつ、開口部内に埋め込み導体を埋め込みやすくする。

【解決手段】半導体ウェハW1の中心から左側に離れたチップ領域C1a、C1bでは、開口部13a、13b内の左右の壁面のうち右側の壁面にのみ深さ方向に沿って傾斜面を設け、半導体ウェハW1の中心から右側に離れたチップ領域C1d、C1eでは、開口部13d、13e内の左右の壁面のうち左側の壁面にのみ深さ方向に沿って傾斜面を設け、半導体ウェハW1の中心の近傍のチップ領域C1cでは、開口部13c内の左右の壁面には傾斜面を設けないようにする。

(もっと読む)

半導体装置の製造方法

【課題】加工精度を改善し、かつ厚い配線を得るための半導体装置の製造方法を提供することを課題とする。

【解決手段】絶縁性基板上に形成された導電性膜上に配線形成領域を覆う第1のフォトレジストパターンを形成する工程と、前記第1のフォトレジストパターンをマスクとする異方性エッチングにより前記導電性膜の上部を除去することで第1溝を形成する工程と、前記第1のフォトレジストパターンを除去した後、前記第1溝の底部の少なくとも一部が露出した開口を有する第2のフォトレジストパターンを形成する工程と、前記第2のフォトレジストパターンをマスクとする異方性エッチングにより前記第1溝の底部に露出する前記導電性膜の下部を少なくとも除去することで第2溝を形成する工程を備えることで、前記第1溝と第2溝に由来する配線分離溝と、前記配線分離溝により分離された配線とを形成することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体装置

【課題】耐熱性に優れ、不均一動作が抑制される高周波高出力半導体装置を提供する。

【解決手段】半導体基板上に形成される複数の電界効果トランジスタが並列接続される単位セルを、さらに複数並列接続する半導体装置において、この単位セルを構成する電界効果トランジスタの複数のゲート電極同士を接続するゲートバス配線に接続され、複数の導電層が積層した構造を有するゲートパッド電極と、隣接するゲートパッド電極間同士を接続し、ゲートパッド電極外周部の少なくとも一辺に沿って形成され、ゲートパッド電極を構成する複数の導電層の少なくとも一つの導電層で形成される抵抗体とを有することを特徴とする半導体装置。

(もっと読む)

161 - 180 / 485

[ Back to top ]