Fターム[5F033GG02]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930) | 化合物半導体 (913) | III−V族 (485)

Fターム[5F033GG02]に分類される特許

101 - 120 / 485

クラックストップを備えたデバイス

基板上のデバイスと基板内のクラックストップとを備える装置である。デバイスを形成する方法も開示される。これらの方法は、半導体デバイスのようなデバイスを第1の厚さを有する基板上に設けることと、基板の厚さを第2の厚さまで低減することと、クラックストップを基板内に設けることとを含み得る。基板の厚さを低減することは、この基板を支持用の担体基板に取り付けることと、その後、この担体基板を取り外すこととを含み得る。クラックストップは、クラックがデバイスに到達することを妨げ得る。  (もっと読む)

(もっと読む)

集積回路および集積回路の製造方法

【課題】トランジスタのゲート電極上に第1の誘電体層を形成し、かつ金属層と接合したダマシン構造を形成する方法を提供する。

【解決手段】トランジスタのゲート電極上に第1の誘電体層を形成し、第1の誘電体層上にエッチストップ層を形成し、第1の誘電体層およびエッチストップ層を貫通する開口を形成し、トランジスタのソース/ドレイン(S/D)領域を露出し、開口内に、エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成して、トランジスタのS/D領域に接触させ、さらに金属層と接合したダマシン構造を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置のビアホールにおける残渣物の残留を抑制することができ、かつ、半導体装置のデバイス特性不良、信頼性不良等を抑制することができる、半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、GaN系半導体層(11)が設けられたSiC基板(10)の第1主面の反対側の第2主面上にCuあるいはCu合金からなり部分的に開口を有するエッチングマスク(50)を形成する工程と、エッチングマスク(50)を利用したドライエッチングを実施し、底部の厚さ方向にGaN系半導体層(11)が残存したビアホールを形成する第1エッチング工程と、第1エッチング工程の後にエッチングマスク(50)を除去する除去工程と、除去工程の後に残存したGaN系半導体層(11)に対してドライエッチングを実施する第2エッチング工程と、を含む。

(もっと読む)

銅プラグを有する半導体デバイスおよびデバイスを形成するための方法

【課題】絶縁層がデバイスの最終配線層と接触する銅プラグを有する、半導体デバイスを提供する。

【解決手段】銅プラグと絶縁層とを分離する障壁層も存在可能である。他の実施形態では、絶縁層と銅プラグとの間にアルミニウム層も存在可能である。半導体デバイスを生成するためのプロセスも開示される。

(もっと読む)

段階化キャップ層を有するパターニング可能low−k誘電体配線構造、エアギャップ包含配線構造、および製作方法

【課題】パターニングされた段階化キャップ層の表面上に配される少なくとも1つのパターニングされ且つ硬化されたlow−k物質を含む配線構造を提供する。

【解決手段】少なくとも1つの硬化され且つパターニングされたlow−k物質およびパターニングされた段階化キャップ層は、その中に組み込まれる導電的充填領域を各々有する。パターニングされ且つ硬化されたlow−k物質は、1つ以上の酸感受性イメージング可能基を有する機能性ポリマー、コポリマー、あるいは少なくとも2種の任意の組み合わせのポリマー類もしくはコポリマー類またはその両方を含むブレンドの硬化生成物であり、段階化キャップ層はバリア領域として機能する下部領域および恒久的な反射防止膜の反射防止特性を有する上部領域を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】放熱性に優れ、高周波高出力で使用可能な、化合物半導体高電子移動度トランジスタを提供する。

【解決手段】支持基板20の第1の主表面20a上に、チャネル層40及びバリア層50が積層されて構成される、化合物半導体高電子移動度トランジスタであって、ソース電極62が形成された領域を含む、支持基板の領域部分が金属部22であり、ドレイン電極64が形成された領域を含む、支持基板の他の領域部分がシリコン部24で構成される。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】ダイシング時で半導体チップに発生するチッピング、割れ、或いは欠けを低減する。

【解決手段】半導体装置80は、半導体チップ50がガラス基板60にFace Downして載置され、接着層10で半導体チップ50とガラス基板60が接着される。半導体チップ50には、シリコン基板1、集積回路部2、受光部3、層間絶縁膜4、樹脂層5、表面電極6、貫通電極8、裏面電極9、裏面保護膜12、ボール端子13が設けられる。樹脂層5は、シリコン基板1上に層間絶縁膜4と接するように半導体チップ50の端部に設けられる。樹脂層5は、層間絶縁膜4をエッチングした開口領域に設けられる。半導体装置80は、接着層10により固着されたシリコンウェハ100とガラス基板60をブレードダイシングにより個片化されたものである。

(もっと読む)

電極コンタクト構造、自己走査型発光素子アレイ

【課題】オーミック接触を実現する電極コンタクト構造を提供する。

【解決手段】電極コンタクト構造は、エピタキシャル層100と、エピタキシャル層100上に形成されたコンタクトメタル電極120と、コンタクトホールを有する層間絶縁膜140と、コンタクトメタル電極120上に形成された第1のAl配線160と、第1のAl配線160上に形成された拡散障壁層180と、拡散障壁層180上に形成された第2のAl配線200を有する。電極コンタクト構造は、自己走査型発光素子アレイのカソード電極やゲート電極の構造として用いられる。

(もっと読む)

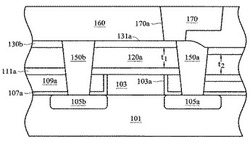

半導体基板の製造方法

【課題】半導体基板が厚い場合においても貫通電極を高生産性、高品質で低コストで実現できる半導体基板の製造方法を提供することを目的とする。

【解決手段】半導体基板(101)にアクティブ面が露出する開口部(104)を有する電極パッド(102)を形成し、開口部(104)からアクティブ面の反対側の面に向かって凹部(105a)を形成し、凹部(105a)の内側に絶縁膜(106)を形成し、絶縁膜(106)と電極パッド(102)の表面に導電経路(107)を形成し、アクティブ面の反対側の面から半導体基板(101)を薄型化して凹部(105a)の底部を貫通させる。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】めっき動作を動的に制御することの可能な電気めっき方法を提供すること。

【解決手段】ウェハ20上に銅層を形成する方法は、ウェハ20を電気めっきチャンバ10内に配置する段階であって、電気めっきチャンバ10が少なくとも一つの電気コンタクト18を通じてウェハ20に電気的に接続される制御システム34を有し、制御システム34がウェハ20に電力を提供する、段階と、ウェハ20に給電して、ウェハ20上に銅を電気めっきする段階と、電気めっき中にウェハ20の電気特性を監視して、電気めっきチャンバ10内の条件を変更すべきときを判断する段階とを備える。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】アスペクト比の高い開口部内に空隙を形成することなく銅層を埋め込むことの可能な電気めっき方法を提供すること。

【解決手段】ウェハ上に銅層を形成する方法は、制御システムを有する電気めっきチャンバ内にウェハを配置する段階と、第1期間302の間にウェハに対する第1電力を正にパルス化する段階と、第1期間302に続く第2期間304の間にウェハに対する第2電力を負にパルス化する段階と、第2期間304に続く第3期間306の間にウェハに対する第3電力を正にパルス化する段階とを備える。

(もっと読む)

電極コンタクト構造、自己走査型発光素子アレイ

【課題】不均一な結晶相の形成を抑制してオーミック接触を実現する電極コンタクト構造を提供する。

【解決手段】電極コンタクト構造は、エピタキシャル層100と、エピタキシャル層100上に形成されたコンタクトメタル電極120と、コンタクトホールを有する層間絶縁膜140と、コンタクトメタル電極120上に形成され、コンタクトメタル電極の結晶配向性と整合する結晶配向性を有する拡散障壁層200と、拡散障壁層200上に形成されたAl配線160を有する。電極コンタクト構造は、自己走査型発光素子アレイのカソード電極やゲート電極の構造として用いられる。

(もっと読む)

光学装置および光学装置の製造方法

【課題】より効率良く光学装置を製造できる光学装置の製造方法を提供すること。

【解決手段】 複数の光学素子1を備える光学素子シート6を、配線パターン3が形成された基板シート7に接合する工程と、上記接合する工程の後に、光学素子シート6を切断することにより、複数の光学素子1どうしを分離する工程と、上記接合する工程の後に、基板シート7を切断することにより、光学素子1と接合している配線基板を形成する工程と、を備える。

(もっと読む)

相互接続構造およびこれを形成する方法(細い相互接続開口のための導電性構造)

【課題】電気的抵抗が低い相互接続構造、および、かかる相互接続構造を形成する方法を提供する。

【解決手段】相互接続構造は、少なくとも1つの開口を含む誘電物質を含む。少なくとも1つの開口内には、任意のバリア拡散層、結晶粒成長促進層、凝集めっきシード層、任意の第2のめっきシード層、および導電性構造が配置される。典型的にはCuである金属含有導電性物質を含む導電性構造は、バンブー微細構造を有し、平均グレイン・サイズが0.05ミクロンよりも大きい。いくつかの実施形態では、導電性構造は、(111)結晶方位を有する導電性結晶粒を含む。

(もっと読む)

半導体素子およびその製造方法

【課題】ウェットエッチングにより形成される配線の線幅のばらつきが抑えられた半導体素子を提供する。

【解決手段】半導体素子の製造方法は、半導体層14上に電極11を形成する工程と、半導体層14上に、電極11に達する配線接続孔12aを有し、配線接続孔12aの周りに凹部12bが形成された層間絶縁膜12を形成する工程と、層間絶縁膜12上から配線材料18を堆積する工程であって、層間絶縁膜12の凹部12bに対応して配線材料18に凹部18aが形成される工程と、配線材料18上に、電極11に配線接続孔12aを介して接続される配線13を形成するためのレジスト膜19を、配線材料18に形成された凹部18aを覆うように形成する工程と、レジスト膜19をマスクとしてウェットエッチングを行い、配線材料18を選択的に除去して配線13を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】 研削屑の付着が抑制されたメッキ下地層上にメッキ層を安定して形成可能な半導体装置の製造方法を提供する。

【解決手段】 表面領域の拡散領域13に接続された下地メタル15を有する半導体基板11に、下地メタル15を被う絶縁膜17を形成する工程、少なくとも下地メタル15の表面露出予定部分に開口を有するように、絶縁膜17上にパターニングされたポリイミド膜19を形成する工程、絶縁膜17及びポリイミド膜19を被い表面保護テープ21を貼付する工程、半導体基板11の裏面を研削する工程、半導体基板11の表面保護テープ21を除去し、下地メタル15と反対側より、半導体基板11の中にキャリアライフタイム制御用のヘリウム照射23を行い、アニールを行う工程、ポリイミド膜19をマスクとして絶縁膜17をエッチングし、下地メタル15を露出する工程、及び下地メタル15上に、Ni/Auのメッキ膜25を形成する工程を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ウエハが反るのを防止できる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、互いに対向する第1及び第2の主面を有するGaAs基板と、前記GaAs基板の前記第1の主面上に形成され、Pd、Ta、Moの少なくとも1つから構成された第1の金属層と、前記第1の金属層上に形成され、Ni系合金又はNiから構成された第2の金属層と、を備えることを特徴とする。

(もっと読む)

半導体基板上のスルーインターコネクトを製造する方法

半導体基板のスルーインターコネクトを製造する方法は、基板の第1側部上に基板を部分的に通るビアを形成するステップと、第1側部上及びビア内に電気絶縁層を形成するステップと、絶縁層上にビアを少なくとも部分的にライニングする導電層を形成するステップと、ビア内の導電層上に第1コンタクトを形成するステップと、ビア内の、少なくとも絶縁層まで基板の第2側部から基板を薄層化するステップとを含む。また、本方法は、第1コンタクトと電気接続状態にある第2コンタクトを基板の第2側部に形成するステップをも含み得る。本方法は、ウエハスケールのインターコネクト要素を形成するように半導体ウエハ上で実行可能である。さらに、インターコネクト要素を、発光ダイオード(LED)システムのような半導体システムを構築するのに使用可能である。 (もっと読む)

半導体素子の配線構造、発光素子、発光素子アレイ、および画像形成装置

【課題】電極層と配線層との合金化による接合安定性が得られつつ、合金化の進みすぎによる空孔の発生が抑制された半導体素子の配線構造を提供する。

【解決手段】半導体素子10の配線構造は、半導体素子10を構成する半導体層14上に設けられ、金属により形成された電極層11と、電極層11上に設けられ、電極層11の金属と合金化し得る金属により形成された配線層12と、電極層11と配線層12との間に設けられ、配線層12と同じ種類の金属を主成分とする、電極層11の膜厚以下の膜厚を有する中間層13であって、電極層11の金属の配線層12への拡散を防止する、中間層13の金属の金属化合物膜13bが、配線層12側の表面に形成されている中間層13と、を含む。

(もっと読む)

半導体装置の作製方法

【課題】電界メッキ法やCMP法を使わないことで製造コストを落として配線を形成する半導体装置の作製方法を提供する。

【解決手段】絶縁膜を形成する工程と、絶縁膜上にマスクを形成する工程と、選択的にエッチングして絶縁膜に開口部を形成する工程と、マスク上および開口部に第1導電膜を形成する工程と、液滴吐出法により開口部の第1導電膜上に導電材料を含む液滴を滴下する工程と、レーザー光を選択的に照射して導電材料を加熱して第2導電層を形成する工程と、マスク上および第2導電層上に第3導電膜を形成する工程と、マスクを除去すると同時にマスク上に形成された第1導電膜および第3導電膜を除去し、第1導電層および第3導電層を形成する工程とを有する半導体装置の作製方法を提供する。

(もっと読む)

101 - 120 / 485

[ Back to top ]