Fターム[5F033GG02]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930) | 化合物半導体 (913) | III−V族 (485)

Fターム[5F033GG02]に分類される特許

41 - 60 / 485

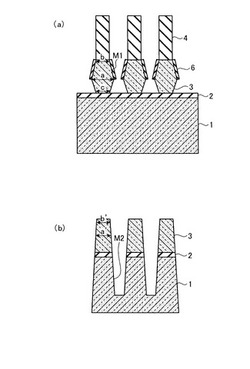

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】ヒートシンクに生じる不具合を低減すること。

【解決手段】半導体装置は、第1面及び第2面を有し、第1面と第2面とを貫通するバイアホールを有する半導体基板と、第1面上に、バイアホールの開口と少なくとも部分的に重複するように形成された配線又は電極と、第2面上に形成され、バイアホールの開口と少なくとも部分的に重複する開口を有する応力緩衝層と、応力緩衝層上からバイアホールの内壁面に沿って延在し、配線又は電極と電気的に接続されたヒートシンクと、を備える。バイアホールの第2面における開口の大きさは、第1面における開口の大きさよりも大きい。応力緩衝層の熱膨張係数は、ヒートシンクの熱膨張係数未満である。

(もっと読む)

ヴィア構造およびその作製方法

【課題】より小さな径の基板貫通ヴィアが形成できるようにする。

【解決手段】基板101の回路が形成されている主表面101a側から所望の孔径の範囲で形成可能な深さに形成された第1孔部102と、基板101の裏面側から形成されて第1孔部102に接続する第2孔部103と、第1孔部102の内部に形成された第1孔部配線104と、第1孔部配線104に接続して基板101の主表面101a側に形成された表面配線層105と、第2孔部103の内部に第1孔部配線104に接続して形成された第2孔部配線106と、第2孔部配線106に接続して基板101の裏面側に形成された裏面配線層107とを備える。

(もっと読む)

半導体記憶装置

【課題】さらなるDRAMの大記憶容量化を図る。

【解決手段】半導体記憶装置が、単結晶半導体材料を含む基板の一部を有する駆動回路と、当該駆動回路上に設けられる多層配線層と、当該多層配線層上に設けられるメモリセルアレイ層とを有する。すなわち、当該半導体記憶装置においては、駆動回路と、メモリセルアレイとが重畳して設けられる。したがって、単結晶半導体材料を含む基板に駆動回路及びメモリセルアレイを同一平面に設ける場合と比較して、当該半導体記憶装置の集積度を高めることが可能となる。

(もっと読む)

異方性エッチング方法、三次元構造体、及び、デバイス

【課題】被対象物を効率よく所望する形状となるようにエッチングすることが可能な異方性エッチング方法、該異方性エッチング方法を用いて形成可能な三次元構造体、及び、該三次元構造体を備えたデバイスを得る。

【解決手段】異方性エッチング方法は、表面に所定形状のマスクを有した基板に対して、SF6とC4F8とを含む混合ガス、又は、SF6とC4F8とO2とを含む混合ガスを用いた反応性イオンエッチングによって、所定条件下で結晶異方性エッチングを行う結晶異方性エッチング工程を有している。本方法と、Bosch法による垂直異方性エッチングを行う垂直異方性エッチング工程とを用いて三次元構造体を製造し、該三次元構造体をデバイスに利用する。

(もっと読む)

金属充填方法及び金属充填装置

【課題】基板の貫通孔への金属の充填不良を抑制する。

【解決手段】基板100の上面101と下面102との間を貫通する貫通孔110に金属120を充填する方法は、上面101に溶融金属31を供給する工程S40と、下面102における貫通孔110の開口の周囲の圧力を、上面101上に供給された溶融金属31の周囲の圧力よりも相対的に低くすることで、貫通孔110内に溶融金属31を充填する工程S30及びS50と、を備えている。

(もっと読む)

配線パターン

【課題】コンタクトホールを起点とした絶縁膜の剥がれの伸展を防ぐことができる配線パターンを得る。

【解決手段】半絶縁性GaAs基板1上に、配線メタル2が設けられている。配線メタル2上に金メッキ4が設けられている。金メッキ4は、ボンディングパッド部5と配線部6を有する。ボンディングパッド部5及び配線部6を覆うように金メッキ4上に連続してSiN膜7が設けられている。ボンディングパッド部5上においてSiN膜7にコンタクトホール8が設けられている。ボンディングパッド部5と配線部6の間において金メッキ4に段差が設けられている。

(もっと読む)

半導体装置、その製造方法、および半導体装置を含む半導体パッケージ

【課題】装置特性の低下を防止するとともに、半導体基板と貫通電極の短絡を防止する半導体装置を提供する。

【解決手段】第1面と、第1面と対向してトレンチが形成された第2面とを有する基板と、基板内に形成されたビアホールを充填し、ビアホールの内壁から順にビアホール絶縁膜、障壁膜、および導電性接続部を有してなる貫通ビアと、第2面上に形成されて貫通ビアの一部領域を露出する開口部を有する絶縁膜と、トレンチ内に埋め込まれ、貫通ビアと電気的に接続される再配線と、を有し、絶縁膜は導電性接続部の一部領域と重複する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】トレンチ2内に埋め込まれた第2の埋め込み絶縁膜4の一部が除去されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、浮遊ゲート電極6間が完全に埋め込まれないようにして制御ゲート電極8間にカバー絶縁膜10が掛け渡されることで、ビット線方向にDBに隣接する浮遊ゲート電極6間に空隙AG2が形成されている。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】レンチ2内に埋め込まれた埋め込み絶縁膜3の一部を除去することで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1を形成し、空隙AG1は、制御ゲート電極8下に潜るようにしてトレンチ2に沿って連続して形成する。

(もっと読む)

ビアホールの製造方法およびビアホールを有する半導体素子の製造方法

【課題】内部への埋め込み材料を増量させて放熱性向上効果を得ることが可能なビアホール構造を、ビアホール形成のための半導体基板へのエッチングの回数を少なくしつつ製造することのできるビアホールの製造方法およびビアホールを有する半導体素子の製造方法を提供する。

【解決手段】メタルマスク8は、メタルマスク10の開口23により露出させられた部分8aを有する。メタルマスク10は、メタルマスク8よりも厚く形成する。メタルマスク10の厚さは、開口23内のエッチングが半導体デバイス形成層4にほぼ到達すると同時に、開口22のエッチングがソース電極1に到達する厚さに設定する。

(もっと読む)

半導体装置

【課題】電極パッド直下の領域を有効領域とする半導体装置の提供を目的とする。

【解決手段】本発明の半導体装置は、半導体層上に設けられた、シリサイド膜からなるエミッタ電極7と、エミッタ電極7上に形成された絶縁膜10と、絶縁膜10上に形成されたAlからなる電極パッド8とを備える。

(もっと読む)

半導体装置及び電源装置

【課題】半導体装置において、抵抗が増大して変換効率が低下してしまうのを防止する。

【解決手段】半導体装置を、基板2上に形成されたGaN系半導体積層構造3を有する第1トランジスタQ1と、GaN系半導体積層構造を有する第2トランジスタQ2とを備え、第1トランジスタが、複数の第1フィンガ8AXを有する第1ゲート電極8Aと、複数の第1ドレイン電極9Aと、複数の第1ソース電極10Aとを備え、第2トランジスタが、複数の第2フィンガ8BXを有する第2ゲート電極8Bと、複数の第2ドレイン電極9Bと、複数の第2ソース電極10Bとを備え、複数の第1ドレイン電極の上方又は下方に接続されたドレインパッド15と、複数の第2ソース電極の上方又は下方に接続されたソースパッド25と、複数の第1ソース電極及び複数の第2ドレイン電極に接続された共通パッド35とを備えるものとする。

(もっと読む)

パターン形成方法及び回路基板の製造方法

【課題】印刷法にて、容易にヴィアホール等のパターンを形成する方法を提供する事。

【解決手段】基板上に設けられた第一高分子材料からなる第一薄膜をパターニングする際に、第一高分子材料を溶解する第一溶媒に第二高分子材料を溶解させた高分子溶液を準備し、これを第一薄膜に滴下する高分子溶液滴下工程と、第一溶媒が乾燥した後に第一薄膜を第二溶媒に触れさせる第二溶媒接触工程と、を含み、第二溶媒は第一高分子材料を溶解せず、第二高分子材料を溶解する溶媒とする。

(もっと読む)

エッチング剤、エッチング方法及びエッチング剤調製液

【課題】半導体基板上のタングステン(W)系金属膜をエッチングし得る半導体基板用エッチング剤、当該エッチング剤を用いるエッチング方法、並びにエッチング剤調製液を提供する。

【解決手段】(A)過酸化水素、(B)ヒドロキシル基を有するホスホン酸系キレート剤、(C)塩基性化合物及び(D−2)無機酸由来のアニオン種並びに炭酸イオン、モノカルボン酸イオン、ヒドロキシトリカルボン酸イオン及びヒドロキシカルボン酸イオンから選ばれる有機酸由来のアニオン種から選ばれる2種以上のアニオン種0.01重量%〜3重量%を含む溶液からなる、タングステン(W)系金属膜上部にタングステンよりもイオン化傾向の低い金属バンプ又は金属配線が形成された半導体基板用エッチング剤、該エッチング剤を用いるW系金属膜のエッチング方法、並びに上記(B)、(C)及び(D−2)を含む溶液からなる、半導体基板用エッチング剤調製液。

(もっと読む)

成膜方法及び成膜装置

【課題】 ボイド等の発生を防止できるように凹部内に金属膜の成膜を施すことができる成膜方法である。

【解決手段】 処理容器22内でプラズマにより金属のターゲット76から金属イオンを発生させてバイアスにより引き込んで凹部4が形成されている被処理体に金属の薄膜を堆積させる成膜方法において、ターゲットから金属イオンを生成し、その金属イオンをバイアスにより引き込んで凹部内に下地膜90を形成する下地膜形成工程と、金属イオンを発生させない状態でバイアスにより希ガスをイオン化させると共に発生したイオンを引き込んで下地膜をエッチングするエッチング工程と、ターゲットをプラズマスパッタリングして金属イオンを生成し、その金属イオンをバイアス電力により引き込んで金属膜よりなる本膜92を堆積しつつ、その本膜を加熱リフローさせる成膜リフロー工程とを有する。

(もっと読む)

配線形成方法

【課題】下層配線層と配線シード層との密着性を低下させないで高く維持することが可能な配線形成方法を提供する。

【解決手段】下層配線層4と絶縁性バリヤ層6と層間絶縁膜8と上層配線層が順次積層された被処理体に対して上層配線層と、連通配線層16とを形成する配線形成方法において、絶縁性バリヤ層を残した状態で連通ホール9Bを形成し、連通ホール内に犠牲膜を埋め込み、トレンチ9Aを形成するパターンマスク62を形成する前処理工程と、トレンチを形成するトレンチ形成工程と、犠牲膜60とパターンマスクとをアッシングするアッシング工程と、トレンチ内と連通ホール内に熱処理によりバリヤ層10を形成するバリヤ層形成工程と、異方性エッチングにより連通ホールの底部のバリヤ層と絶縁性バリヤ層とを除去する異方性エッチング工程と、配線シード層12を形成する配線シード層形成工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】高周波領域において優れた電気的特性が得られるように、寄生容量を低減し得る半導体装置の製造方法を得る。

【解決手段】第1のソース電極、ゲート電極、ドレイン電極、及び第2のソース電極が、所定方向に沿ってこの順に並んで半導体基板の上面上に形成された構造を有するトランジスタを形成する。犠牲層を、トランジスタを覆って半導体基板の上面上に形成する。犠牲層を部分的に除去することにより、第1のソース電極及び前記第2のソース電極を露出する。第1のソース電極及び第2のソース電極に接続され、所定方向に沿って延在する配線を、犠牲層の上面上に形成する。犠牲層を除去する。トランジスタ及び配線を覆う形状に加工されたシート、テープ、又は基板を、トランジスタ及び配線を覆って半導体基板の上面上に貼り付ける。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、半導体集積回路上及びスクライブ領域上を覆うパッシベーション膜を備えた半導体装置の製造装置に関し、パッシベーション膜に起因する半導体基板の反りを低減することを課題とする。

【解決手段】スクライブ領域B上に設けられたパッシベーション膜13に、複数の回路形成領域Aを囲むように格子状の溝47を形成した。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】容量増加による高周波特性の劣化及び裏面電極に起因する絶縁破壊を抑止し、チップ面積を増加させることなく、インパクトイオン化により生成したホールを容易且つ確実に引き抜いて排出することを可能として、高耐圧性及び高信頼性を実現する化合物半導体装置及びその製造方法を提供する。

【解決手段】絶縁性又は半絶縁性の基板1の表面に電子走行層3、電子供給層4が形成され、電子供給層4内には局所的なp型領域7が形成されており、基板1の裏面にp型領域7の一部を露出させる開口1aが形成され、開口1aを導電材料で埋め込みp型領域7とオーミック接続された裏面電極8を備え、AlGaN/GaN・HEMTが構成される。

(もっと読む)

41 - 60 / 485

[ Back to top ]