Fターム[5F033GG02]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930) | 化合物半導体 (913) | III−V族 (485)

Fターム[5F033GG02]に分類される特許

21 - 40 / 485

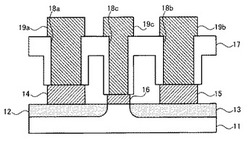

半導体装置及びその製造方法

【課題】精密なエッチング制御を必要とすることなく、ビアホール構造を形成することを可能とするとともに、エッチング後の洗浄を容易にする。

【解決手段】半導体装置において、第1の基板11と、第1の基板表面に形成された素子領域12,13と、素子領域と接続され、第1の基板11上に形成された電極14,15,16と、第1の基板11と積層される第2の基板17と、第2の基板17を貫通し、電極上に配置されるビアホール18a,18b,18cと、ビアホール内に形成される金属層19a,19b,19cと、を備える。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

パワーデバイス

【課題】膜剥がれの要因となる有機材料を用いることなく、エレクトロマイグレーションの耐性と長期信頼性を向上できるパワーデバイスを提供する。

【解決手段】バリア層4(AlGaN)4上に形成された酸化シリコン(SiO2)からなる層間絶縁膜10と、層間絶縁膜10のソース電極5上に形成され、基板平面に対して略垂直な第1の側壁W1を有する第1コンタクトホール部10aと、第1コンタクトホール部10aの第1の側壁W1の上縁から上側に向かって徐々に広がるように層間絶縁膜10に形成され、基板平面に対して傾斜した第2の側壁W2を有する第2コンタクトホール部10bと、第1,第2コンタクトホール部10a,10b内および層間絶縁膜10上に形成された配線層12とを備える。上記配線層12は、第1コンタクトホール部10aにおいて第1の側壁W1の基板厚さ方向の寸法よりも膜厚が厚い。

(もっと読む)

半導体基板内の埋込ボイドを検出するための方法

【課題】半導体基板内又は基板上に形成された構造内の埋込ボイドを検出するための方法を提供する。

【解決手段】構造を形成するための少なくとも1つの処理ステップを実施する工程と、基板の質量M1を測定する工程と、熱処理を実施する工程と、基板の質量M2を測定する工程と、前記実施した熱処理の前後で測定した基板の質量の差を計算する工程と、前記質量の差を所定値と比較することにより、前記構造内の埋込ボイドの存在を推測する工程とを含む。

(もっと読む)

集積電力段

【課題】集積電力段において、入力電圧を集積電力段の一側面(例えば上面)で受け取り、出力電圧を集積電力段の反対側面(例えば底面)から出力する。

【解決手段】集積電力段は負荷段の上に位置する共通ダイを備え、共通ダイはドライバ段102及び電力スイッチ104を備える。電力スイッチは制御トランジスタ110及び同期トランジスタ112を含む。制御トランジスタのドレインD1が共通ダイの入力電圧を共通ダイの一側面(例えば上面)で受ける。制御トランジスタのソースS1が同期トランジスタのドレインD2に結合され、前記共通ダイの出力電圧を共通ダイの反対側面(例えば底面)で出力する。電力段の下にインターポーザ106を含めることができる。インターポーザは共通ダイの反対側面で共通ダイの出力電圧に結合される出力インダクタ118及び必要に応じ出力キャパシタ120を含む。

(もっと読む)

半導体素子の製造方法

【課題】 製造コストの低減が可能な半導体素子の製造方法を提供する。

【解決手段】 第1再配線層400は、金属バンプ層320の一部分を露出するように形成される。第1再配線層400は、第1拡張パッド部410、第1延長部420及び第1連結部430を備える。第1拡張パッド部410は、金属パッド120と電気的に接続し、外部装置と接続する。第1延長部420は、金属バンプ層320上から第1拡張パッド部410上に延びるように形成される。第1連結部430は、スクライブレーン領域SRに形成され、複数の第1再配線層400を電気的に連結する。第1再配線層400は、銀、ニッケルまたは銅を含むペーストまたはインクを利用したプリンティング方法、または、ロールオフセットプリンティング方法によって形成される。これにより、金属パッドと再配線層との接触抵抗を小さくするとともに、製造コストを低減することができる。

(もっと読む)

半導体電極構造

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられたAl合金膜を有する半導体電極構造を提供する。

【解決手段】基板上に少なくとも、基板側から順に、高融点金属の窒化物薄膜と、Al合金膜とを備えた半導体電極構造であって、前記Al合金膜は、500℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が300nm〜5μmであることを特徴とする半導体電極構造。(a)Alマトリックスの最大粒径が1μm以下(b)ヒロック密度が1×109個/m2未満(c)電気抵抗率が10μΩcm以下

(もっと読む)

半導体装置用Al合金膜

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられた半導体装置用Al合金膜を提供する。

【解決手段】500℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が500nm〜5μmであることを特徴とする半導体装置用Al合金膜。(a)Alマトリックスの最大粒径が800nm以下(b)ヒロック密度が1×109個/m2未満(c)電気抵抗率が10μΩcm以下

(もっと読む)

導電性ビアの製造と充填のための方法、およびそのように形成された導電性ビア

【課題】ビアホール表面上の絶縁コーティングとビアホール内に挿入される導電材料との付着性を向上する。

【解決手段】導電性ビアを形成する方法は、一つ以上のビアホールを基板内に形成するステップを含む。ビアホールは、単一マスク、保護層、ボンドパッド、もしくは、エッチングプロセスの間にフォトマスクが除去される場合にハードマスクとして機能する、基板のその他のフィーチャで形成され得る。ビアホールは、その表面に低誘電率(低K)誘電材料を含む誘電体コーティングの付着を促進するように構成されてもよい。障壁層が各ビアホールの表面の上に形成されてもよい。種材料(seed material)を含み得るベース層は、その後のビアホールの表面上の導電材料の選択的堆積を促進するように形成されてもよい。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】電極パッドの表面の突出部に起因する不具合が発生し難い半導体装置の製造方法及び半導体装置を提供する。

【解決手段】半導体装置の製造方法は、表面の突出部に突出部、例えば、プロービング痕21が存在する電極パッド2を備える基板1上に、電極パッド2の少なくとも一部を覆う第1の絶縁膜4を形成する第1の絶縁膜形成工程と、第1の絶縁膜4の表面から突起した部分22を除去することができる処理を行う除去処理工程と、除去処理工程後に、第1の絶縁膜4上及び電極パッド2上に第2の絶縁膜5を形成する第2の絶縁膜形成工程とを有する。

(もっと読む)

電子部品、電子部品の製造方法、基板

【課題】チッピング検出用配線が他の部材で覆われている状態であっても、ダイシングによって電子部品を形成した後に、チッピング検出用配線の導通状態を検出するための電圧を印加できる基板を提供する。

【解決手段】電子部品40は、互いに平行を成す一方の主面41aと他方の主面41bが矩形状の基体41を有する。基体41の一方の主面41aには、第一チッピング検出用配線42が配されている。また、基体41の他方の主面41bには、第二チッピング検出用配線44が配されている。第一チッピング検出用配線42は貫通配線43aを介して第二チッピング検出用配線44に電気的に接続される。

(もっと読む)

半導体チップとその製造方法、半導体装置

【課題】立体的な集積に適した、電磁妨害耐性に優れる半導体チップを提供する。また、その半導体チップを用いた、高い電磁妨害耐性と高い処理能力を両立する半導体装置を提供する。

【解決手段】能動素子もしくは受動素子と、それらの素子を電気的に接続する配線部を備えた半導体チップについて、配線部を被覆するように導電性薄膜を設ける。この導電性薄膜は配線部に対して、不要電磁波を遮蔽するシールドとして働くので、半導体チップの電磁妨害耐性が向上する。また、この半導体チップを三次元集積半導体装置に組み込むことで、隣接するチップをフェイス・トゥ・フェイス接続した場合でも、チップ間のクロストークを遮断できる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】良好な側壁形状の開口を有する半導体装置の製造方法および半導体装置を提供する。

【解決手段】GaAs基板101上に形成された誘電体膜102の一部を誘電体膜102の表面から所定の深さまでエッチングする第1のエッチング工程と、第1のエッチング工程により誘電体膜102がエッチングされた第1のエッチング領域11において誘電体膜102をエッチングしてGaAs基板101の表面を露出し、かつ、第1のエッチング領域11を包含する第2のエッチング領域12において第1のエッチング領域11以外の領域に配置された誘電体膜102を所定の膜厚までエッチングする第2のエッチング工程とを含む。

(もっと読む)

電極構造及びその製造方法

【課題】ウェハハンドリングが容易であり、高精度の位置合わせを必要とせず、ビアホールとして機能する開口部を浅く形成でき、さらに開口部を埋め込む第1電極と基板との界面の割れを防止できる電極構造、及びその製造方法を提供することにある。

【解決手段】基板に、第1主表面側から、深さが基板の厚さよりも小さい開口部33を形成する。次に、開口部を埋め込む第1電極35を形成する。次に、第1主表面と対向する基板を第2主表面側から薄層化して、開口部の深さよりも大きい厚さとする。次に、第2主表面側111bから開口部の底面33bへ向けて、基板111に切り込みを入れる39ことによって、第2主表面側から第1電極を露出させる。次に、切り込みを埋め込む第2電極44を形成する。

(もっと読む)

半導体装置の製造方法

【課題】膜の形成によって生じる半導体基板の反りを緩和できる、半導体装置の製造方法を提供する。

【解決手段】SiC半導体基板10の主面上にイオン注入用マスク材18を形成する。マスク材は半導体基板とは異なる熱膨張係数を有する。レジスト膜20をマスクとしてドライエッチングにより複数の装置形成領域の間の領域上(ダイシングライン)14に切欠き部16aを有するマスク用膜16を形成する。イオン注入などの工程を経て半導体装置を形成後、ダイシングラインに沿って各装置形成領域に分離する。

(もっと読む)

薄膜の成膜方法

【課題】基板上への薄膜の成膜速度を上げ、かつトレンチやビアホールの底面に効率よく薄膜を成膜できる薄膜の形成方法を提供すること。

【解決手段】本発明の成膜方法は、開口幅又は開口径が3μm以下で、かつ、アスペクト比が1以上の段差であるトレンチ又はビアホールを有する基板上に薄膜を成膜する成膜方法であり、真空排気可能な処理室に、基板を支持する第1の電極と、前記基板に対向するように配置されターゲットを支持する第2の電極と、前記第2の電極の外側に配置されて当該第2の電極の内側にカスプ磁界を形成する複数のマグネットと、を備え、

前記処理室にNeを含む処理ガスを導入し、前記第1の電極と前記第2の電極の少なくとも一方にプラズマ形成用の高周波電力を供給すると共に、前記第2の電極上にカスプ磁場を生成してプラズマを発生させ、ターゲット物質をトレンチ又はビアホールを有する基板上に成膜する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホール内にめっき層から成るコンタクト層を埋め込んで上下層の電気的接続を行うときの、コンタクト層の埋め込み性を良好にする構造の半導体装置を提供する。

【解決手段】配線層12,16と、少なくとも底部において、三角形の平面形状であるコンタクトホール14と、めっき層から成り、コンタクトホール14の内部を埋めて形成され、配線層12,16に接続されたコンタクト層15とを含む、半導体装置を構成する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程の効率化とパッシベーション膜の剥離の抑制とが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、金を含む配線30a及び配線30bを形成する工程と、配線30a及び配線30bに接して、窒化シリコン膜32をプラズマ気相成長する工程と、窒化シリコン膜32の製膜レートよりも大きな製膜レートのもと、窒化シリコン膜32に接し、窒化シリコン膜32よりもシリコン組成比が小さい窒化シリコン膜22をプラズマ気相成長する工程と、を有する半導体装置の製造方法である。

(もっと読む)

固定された導電性ビアおよびその製造方法

【課題】導電性ビアおよびそれを形成する方法に関する。

【解決手段】導電性ビアが、導電性接触構造と該導電性接触構造上に配置された誘電体層の突出部との間に配置された部分を含む。1つの実施形態において、突出部は、導電性接触構造上にアンダーカット層を形成し、次に、該導電性接触構造およびアンダーカット層上に誘電体層を形成することによって形成される。誘電体層に空洞を形成し、誘電体層の突出部を形成するようにアンダーカット層の材料が該空洞を通して除去される。導電性ビアの導電性材料は次に、突出部の下および空洞に形成される。

(もっと読む)

銅の光子誘起除去

【課題】基板から銅含有層の少なくとも一部を除去する方法を提供する。

【解決手段】第1反応チャンバ中で、銅含有表面層4の少なくとも一部を、ハロゲン化銅表面層5に変える工程と、第2反応チャンバ中で、光子含有雰囲気6に晒して、ハロゲン化銅表面層5の少なくとも一部を除去して、揮発性のハロゲン化銅生成物8の形成を始める工程とを含む。光子含有雰囲気6に晒す間に、この方法は、更に、第2反応チャンバから揮発性のハロゲン化銅生成物8を除去し、第2反応チャンバ中で揮発性のハロゲン化銅生成物8の飽和を避ける工程を含む。本発明の具体例にかかる方法は、銅含有層のパターニングに用いられる。例えば、本発明の具体例にかかる方法は、半導体デバイス中に銅含有相互接続構造を形成するのに使用される。

(もっと読む)

21 - 40 / 485

[ Back to top ]