Fターム[5F033GG02]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930) | 化合物半導体 (913) | III−V族 (485)

Fターム[5F033GG02]に分類される特許

141 - 160 / 485

金属配線評価用パターン、半導体装置及び評価方法

【課題】金属配線断線の際の活性化エネルギーを短時間で直接求めることができる、金属配線評価用パターン、半導体装置及び評価方法を提供する。

【解決手段】半導体基板10に配設した絶縁膜12上の金属配線評価用パターン1であって、狭窄部2と、狭窄部2の一端に接続した第1配線部3と、狭窄部2の他端に接続した第2配線部4とからなる。金属配線評価用パターン1へランプ電圧を繰り返し印加し、流れる電流から狭窄部2のコンダクタンスを計算し、コンダクタンスが100G0から数百G0の相1の状態からコンダクタンスが10〜60G0の相2の状態を経て、狭窄部2を破壊しナノ接合を形成し、相2の臨界接合電圧(Vc)のヒストグラムを作成し、ヒストグラムの最頻値の電圧からエレクトロマイグレーションの活性化エネルギーを求めることができる。

(もっと読む)

ビア構造とそれを形成するビアエッチングプロセス

【課題】ビア構造とそれを形成するビアエッチングプロセスを提供する。

【解決手段】ビアエッチングプロセスは、丸角とテーパ型側壁プロファイルを有するスルーサブストレートビアを形成する。その方法は、半導体基板を提供するステップと、半導体基板上に、ハードマスク層とパターン化フォトレジスト層を形成するステップと、ハードマスク中に開口を形成して、半導体基板の一部を露出するステップと、パターン化されたフォトレジスト層とハードマスク層をマスキング要素として、半導体基板の少なくとも一部を通過するビアを形成するステップと、トリミングプロセスを実行して、ビアの頂角を丸くするステップと、フォトレジスト層を除去するステップと、からなる。

(もっと読む)

半導体基板と半導体基板の製造方法および半導体パッケージ

【課題】高信頼性の貫通電極を有する半導体基板と半導体基板の製造方法を提供することを目的とする。

【解決手段】第1絶縁層(2)を介して第1配線層(3)が形成され、貫通孔(4)の内周に第2配線層(5)を形成し、貫通孔(4)は、第1の開口部(4a)と、第1の開口部(4a)よりも開口面積が小さい第2の開口部(4b)で形成され、第2の開口部(4b)に第3配線層(103a)を形成するとともに、第3配線層(103a)を第1の開口部(4a)よりも先に形成することを特徴とする。

(もっと読む)

信頼性向上のためのケイ化銅パッシベーション

【課題】その表面をケイ化銅に転化することにより、銅相互接続構造の露出銅表面を直接不動態化するための方法を提供すること。

【解決手段】その後の誘電体フィルムの形成とともに原位置に実行されるシラン・パッシベーション・プロセスは、Cu相互接続構造の露出したCu表面をケイ化銅に転化する。ケイ化銅は、Cu拡散およびエレクトロマイグレーションを抑制し、後続導体材料との接触が行われる領域内でバリア材として機能する。銅相互接続構造の銅表面全体をケイ化する場合もあれば、銅表面の一部分を露出するように上に重なる誘電体に開口部を形成した後で表面の局部部分をケイ化する場合もある。

(もっと読む)

半導体装置

【課題】開口率の高い半導体装置又はその作製方法を提供することを目的の一とする。また、消費電力の低い半導体装置又はその作製方法を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に設けられた半導体層と、半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の導電層と第2の導電層とで積層されたゲート電極を含むゲート配線と、半導体層と前記ゲート電極を含む前記ゲート配線を覆う絶縁膜と、絶縁膜上に設けられ、半導体層と電気的に接続され、第3の導電層と第4の導電層とで積層されたソース電極を含むソース配線と、を有し、ゲート電極は、第1の導電層で形成され、ゲート配線は、第1の導電層と第2の導電層で形成され、ソース電極は、第3の導電層で形成され、ソース配線は、第3の導電層と第4の導電層で形成されている。

(もっと読む)

デバイス及びその製造方法

【課題】微細孔の内壁と微細孔に充填した導電性物質からなる貫通電極との間で発生する隙間や拡散、酸化を抑制し、パッドと貫通電極との電気的接続の安定性を向上させることが可能なデバイスの製造方法を提供する。

【解決手段】第一基板と、該第一基板の一方の面側に配された、機能素子及び該機能素子に第一配線を介して電気的に接続されたパッドと、該パッドと電気的に接続され、前記第一基板の一方の面から他方の面に至る微細孔内に第一導電体を充填してなる貫通電極とを、少なくとも具備してなるデバイスの製造方法であって、前記第一基板の他方の面から、Deep-Reactive Ion Etching 法を用いて、前記パッドが露出するまで前記微細孔を形成する工程Aと、前記微細孔の内面の少なくとも一部に、前記第一導電体とは異なる第二導電体からなる導電部を形成する工程Bと、前記微細孔の内部に前記第一導電体を充填する工程Cと、を備える。

(もっと読む)

半導体装置

【課題】小型化及び利得等の高周波性能の向上を図ることができる半導体装置として、実用的な高周波増幅器を実現する。

【解決手段】トランジスタ101の入力端に配線層103がコプレーナ線路で接続されており、配線層103には、開放端を有する配線層104が二つの方向に分岐されて終端され、配線層103上の位置から、高周波信号が入出力される。

(もっと読む)

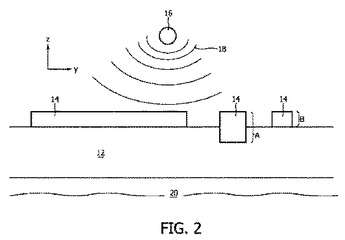

集積回路を製造する装置及び方法

本発明は、厚膜金属層14を有する集積回路10を製造する装置に関する。金属ペースト14の層は、熱伝導基板12上に適用手段24によって適用される。金属ペースト14は、予め決められたサイズの金属粒子を含む。RF生成器16は、金属ペースト14にRFエネルギー18を選択的に誘導結合させる。金属粒子を加熱するために、金属ペースト14の金属粒子の予め決められたサイズは、RFエネルギー18の結合周波数に対応する。このようにして、金属ペースト14の金属粒子は、従来のプロセスのパワーの何分の一かのパワーで、金属ペースト14を予備焼結する必要なく、加熱される。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電極パッドよりも径の小さな貫通孔を半導体基板自体に設けることなく、上下に積層された半導体チップ間の電気的な接続を行う。

【解決手段】半導体基板S1の横にはみ出すように電極パッドP1を配置し、半導体基板S1の周囲を取り囲むように配置された樹脂層J1上にて支持し、電極パッドP1が上下に重なるように半導体チップC1を積層し、貫通孔T1内に導電体D1を埋め込むことで、上下の電極パッドP1を電気的に接続し、上下に積層された半導体チップC1間の電気的な接続を行う。

(もっと読む)

垂直接触電子部品及びその製造方法

本発明は、電子部品に関するもので、接触平面に位置する少なくとも一つの接触表面と、前記接触平面の上方にある少なくとも一つの絶縁層と、該部品の機械的安定性を高めるために、前記絶縁層に接して配置される少なくとも一つの安定化層と、少なくとも一つのボンディング及び/または半田接点とを有し、前記絶縁層及び前記安定化層が少なくとも一つの開口を有し、その開口が、前記接触表面から離れて対向する前記安定化層の一表面に向かって開口するとともに、前記安定化層及び前記絶縁層を通じて前記接触表面まで達し、前記ボンディング及び/または半田接点が、前記安定化層を横切って延び、前記開口を通じて前記接触表面に接する。 (もっと読む)

半導体基板と半導体パッケージおよび半導体基板の製造方法

【課題】高信頼性の貫通電極を有する半導体基板を提供することを目的とする。

【解決手段】第1の開口部(4a)の内周と第2の開口部(4b)の間に位置する前記第1絶縁層(2)の面に凹部(6)が形成され、第2配線層(5)が、第1の開口部(4a)の内周面と凹部(6)および第2の開口部(4b)を経て第1の配線層(3)に電気接続されていることを特徴とする。

(もっと読む)

半導体装置

【課題】オン抵抗の増大を抑制しつつ、ゲート抵抗を低減して高速スイッチング化が図れる半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体層10におけるソース領域14が設けられた表面上に設けられソース領域14と接続された第1の主電極40と、ベース領域13に対して絶縁膜17を介して対向し第1の方向Xに延在するゲート電極16と、ゲート電極16と接続され半導体層10の表面上で第1の方向Xに交差して設けられた第1のゲート配線31と、第1のゲート配線31上に設けられ第1のゲート配線31と接続されたゲートコンタクト部32と、第1のゲート配線31上に設けられ、ゲートコンタクト部32を介して第1のゲート配線31と接続され、第1のゲート配線31よりも幅が広く且つ低抵抗な材料からなる第2のゲート配線32とを備えている。

(もっと読む)

成膜方法及びプラズマ成膜装置

【課題】ステップカバレジを向上させることができ、これによりスループットも高く維持することが可能な成膜方法及びプラズマ成膜装置を提供する。

【解決手段】真空排気が可能になされた処理容器22内へ凹部6を有する絶縁層4が表面に形成された被処理体Wを収容すると共に前記処理容器内へ原料ガスを供給してプラズマCVD法により前記被処理体に対してチタンを含む薄膜を形成する成膜方法において、前記薄膜の形成時の前記処理容器内のプロセス圧力を230〜630Paの範囲内に設定する。これにより、ステップカバレジを向上させることができ、スループットも高く維持することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッドの剥がれを防止し、かつボンディングパッド間におけるリーク電流の発生を防止することができる半導体装置及びその製造方法を提供すること。

【解決手段】HBT(ヘテロ構造バイポーラトランジスタ)が構成要素の1つとして集積された半導体装置110は、半絶縁性InP基板11上に、順次、エッチングストップ層12、コレクタコンタクト層13、コレクタ層14、傾斜コレクタ層15、セットバック層16、ベース層17が形成された構成を有し、ベース層17はInGaAsで構成された薄膜であってPを含まず、このベース層17上にSiN23が形成され、SiN23上にボンディングパッド25が形成された構成を有する。

(もっと読む)

半導体装置

【課題】ガードリングを越えて半導体チップ内に水分が浸入した場合でも、半導体チップ上の1つの電極と他の1つの電極との短絡を抑制すること。

【解決手段】半導体チップ10と、半導体チップ10上に配置された電極パッド14、16と半導体チップ10の外周との間に配置された導電性のガードリング18と、ガードリング18の一部領域を排することで、ガードリング18を互いに絶縁された複数の単位領域に分割するための、複数のガードリング絶縁部60と、を有する半導体装置。

(もっと読む)

シリコン基板上に形成されるCMOSデバイスおよびIII−V族デバイスのための電気コンタクト

半導体構造体は、基板(12)と、基板を覆うシード層(13)と、シード層上に配置されるシリコン層(22)と、シリコン層中のトランジスタデバイス(27)と、シード層上に配置されるIII−V族デバイスと、複数の電気コンタクトと、を備え、それぞれの電気コンタクトは、TiNまたはTaNの層(32)と、TaNまたはTiNの層上の銅またはアルミニウムの層(34)と、を備え、電気コンタクトの1つは、トランジスタ(27)に電気的に接続され、電気コンタクトの別の1つは、III−V族デバイスに電気的に接続される。 (もっと読む)

半導体集積回路およびその製造方法

【課題】伝送線路の損失を低減することが可能な半導体集積回路を提供する。

【解決手段】本発明の半導体集積回路は、表面から裏面までを貫通するビアホール107が設けられたサファイア基板101と、サファイア基板101の表面に形成されたAlGaN/GaNエピタキシャル成長層102内の導電層をチャネルとするHFET106と、サファイア基板101の裏面に形成され、ビアホール107を介してHFET106と電気的に接続された入力側信号線109及び出力側信号線110と接地電極108とから構成されるコプレーナ型伝送線路とを備える。

(もっと読む)

金属層間誘電体による拡散防止バリヤ層を有する集積回路およびその製造方法。

【課題】ライン間キャパシタンスを減少できる構造を有する集積回路および不純物が多層集積回路構造の次の層に存在する導電性要素に対し破壊的反応を起こすのを防止できる集積回路の製造方法を提供する。

【解決手段】低誘電率材料中での不純物の移動を防止できるキャップ層あるいはバリヤ層により、不純物が多層集積回路構造の次の層に存在する導電性要素に対し破壊的反応を起こすのを防止する。集積回路は第一の誘電体層と集積回路のより上層の導電層間に拡散防止バリヤ層を堆積して製造される。拡散防止バリヤ層はその次の金属層で不純物を含む誘電体層へその場で形成され、さらに、研磨を含む処理が多層誘電体構造に対してなされる。キャップ層あるいはバリヤ層にその場堆積は不純物を含む層を雰囲気にさらすのを防止し、そしてキャップ層あるいはバリヤ層により、水分、水素あるいはそのたのものにより、層が汚染されるのを防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通孔(接続孔)内に形成された絶縁膜上に設けられる配線層と半導体基板との間の電気的絶縁性の不良の発生が低減された半導体装置の製造方法を提供する。

【解決手段】半導体基板11の一方の面上に第1の絶縁層12を介して位置する第1の配線層13と、半導体基板の他方の面から第1の配線層に至る接続孔19を形成する。接続孔の側面から他方の面に亘って半導体基板上に位置し、接続孔内で第1の配線層に接する第2の絶縁層14を形成する。接続孔の側面上から他方の面上に亘って第2の絶縁層上に位置し、接続孔内で第1の配線層に接する第2の配線層16を形成する。この形成において、第2の絶縁層を、膜質の異なる2種の絶縁膜14a、14b又はそれ以上の絶縁膜の積層体から構成する。

(もっと読む)

半導体構造、半導体構造を形成する方法、および半導体デバイスを操作する方法(信号忠実度および電気的分離が強化されたSOI無線周波スイッチ)

【課題】SOI(セミコンダクタ・オン・インシュレータ)基板内の底部半導体層からの半導体デバイスについて強化された信号分離を可能とする半導体構造、これを製造する方法、およびこれを操作する方法を提供する。

【解決手段】底部半導体層10と反対の導電性タイプを有するドープ接点領域18は底部半導体層10内の埋め込み絶縁体層20の下に設ける。少なくとも1つの導電ビア構造47,77は、相互接続レベル金属ライン94から、中間工程(MOL)誘電体層80、最上部半導体層30内の浅いトレンチ分離構造33、および埋め込み絶縁体層20を通り、ドープ接点領域18まで延びる構造とする。

(もっと読む)

141 - 160 / 485

[ Back to top ]