Fターム[5F033GG02]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930) | 化合物半導体 (913) | III−V族 (485)

Fターム[5F033GG02]に分類される特許

121 - 140 / 485

ダイシングされた集積回路における破壊の抑制

【課題】低誘電率誘電体を使用するICの歩留り損失及び初期故障を抑止する。

【解決手段】半導体デバイスは基板210及びダイ縁部を有する個片化されたダイ110を備える。相互接続誘電体層220a、220b、220c、220dが基板上に配置され、集積回路がその相互接続誘電体層内に配置された相互接続部230を有する。トレンチ250が、相互接続誘電体層内で、かつシール・リング270と相互接続誘電体層の残部との間に配置される。シール・リングは、相互接続誘電体層内で、かつトレンチと集積回路の間に配置され、相互接続誘電体層の残部はトレンチとダイの縁部との間に配置される。

(もっと読む)

ビアがガウジングされた相互接続構造体及びその製造方法

【課題】 ビア開口部の底部にガウジング構造部を含む相互接続構造体、及びその形成方法を提供する。

【解決手段】 本発明の方法は、ビア開口部の上に配置されるライン開口部内の堆積されたトレンチ拡散バリアの被覆率に影響を与えず、及び/又は、ビア開口部及びライン開口部を含む相互接続誘電体材料内にスパッタリングを行なうことによりビア開口部の底部にガウジング構造部を生成することに起因する損傷を生じさせない。こうした相互接続構造体は、最初に相互接続誘電体内にライン開口部を形成し、その後、ビア開口部、次いでガウジング構造部を形成することによって、ビア開口部の底部内にガウジング構造部を提供することにより達成される。

(もっと読む)

半導体デバイスおよびその構造体の製造方法

【課題】集積回路の配線間に空隙を形成することにより、容量成分が低減された半導体装置の製造方法を提供する。

【解決手段】基板202上に第1の絶縁材が堆積され、この上に、犠牲部分を有する第2の絶縁材232が堆積される。上記第1および第2の絶縁層内に、導電線210がダマシン法により形成される。犠牲部分となる第1の絶縁材を除去するために第2の絶縁材が処理され開口部238が形成される。そして第1の絶縁材が除去されて、導電線間に空隙242が形成される。第2の絶縁材は、堆積時には不透過性であるが、処理後により透過性とし、これを介して犠牲部分を除去する。第2の絶縁材の処理はエッチングによる開口、あるいは熱感受性成分のアニールによる除去である。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、導電性バッファ層を用いることなく、煩雑なプロセスも必要なく、非常に高い深さ精度のドライエッチングも必要なく、また、結晶性を劣化させずに、効率良くホールを引き抜くことができるようにする。

【解決手段】半導体装置を、同一基板1上に形成され、(0001)面及び(000−1)面を有する窒化物半導体層4と、基板1と窒化物半導体層4との間に部分的に設けられた(0001)面形成層2と、(0001)面を有する窒化物半導体層4上に設けられたソース電極5、ドレイン電極6及びゲート電極7と、(000−1)面を有する窒化物半導体層4上に設けられたホール引き抜き電極8とを備えるものとする。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプス現象およびゲートリーク電流を抑制することが可能な電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ1は、基板10と、チャネル層11と、キャリア供給層12と、ソース電極21と、ドレイン電極22と、ゲート電極23と、ソース電極21とドレイン電極22との間でキャリア供給層12に積層されて電流コラプス現象を抑制する第1絶縁層31と、ドレイン電極22に対向する第1絶縁層31の端とドレイン電極22との間に形成された開口部40と、開口部40に露出したキャリア供給層12に積層された第2絶縁層32とを備える。

(もっと読む)

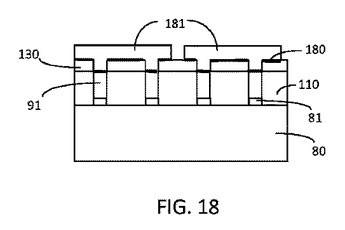

金属/有機誘電体界面でのクラックの低減

有機誘電体材料(110)中に埋め込まれた第2構造(91)への金属相互接続(181)を提供する方法であって、有機誘電体材料(110)中に埋め込まれた、例えば金属ピラー(91)のような第2構造を有する第1構造を得る工程と、少なくとも第1構造のいくつかの位置で、有機誘電体材料(110)の上に硬い層(130)を提供する工程であって、硬い層(130)は有機誘電体材料(110)の剛性より高い剛性を有する工程とを含む方法。この方法は、第1構造(91)と有機誘電体材料(110)との間の界面でクラックの無い相互接続構造を提供する。  (もっと読む)

(もっと読む)

半導体デバイスの製造方法

【課題】薄型化されたウェハにめっき処理をする際にウェハ裏面への金属析出やウェハの反り及び損傷を抑制すると共に、ウェハのめっき処理効率が良好な半導体デバイスの製造方法を提供する。

【解決手段】ウェハを薄型化する工程1、薄型化された前記ウェハの裏面をダイシングテープでリングフレーム内にマウントする工程2、及び、前記リングフレーム内にマウントされた前記ウェハの表面にめっき処理を行う工程3を備えた半導体デバイスの製造方法。

(もっと読む)

貫通シリコンビアを有するめっき物及びその形成方法

【課題】貫通シリコンビア形成時におけるビア内側壁の銅シード層のカバレッジが良好で均一な銅配線層を有するめっき物を提供することを目的とする。

【解決手段】基材上にバリア層として形成された、タングステン及びタングステンと合金化した際に銅に対するバリア性を有する金属(A)との合金薄膜、その上に無電解置換銅めっきにより銅シード層、さらに前記無電解置換銅めっきを実施したのと同一のめっき液を用いた電気銅めっきにより銅配線層がこの順番で形成されてなる、貫通シリコンビアを有するめっき物。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板に素子と貫通電極とが形成された半導体装置の製造方法において、貫通電極からの銅による素子の汚染を防止できる方法を提供する。

【解決手段】半導体基板10と、それに形成された素子ZDと、半導体基板10を貫通するスルーホールTHと、半導体基板10の両面側及びスルーホールTHの内面に形成されて、素子ZDを被覆する絶縁層12とを備えた構造体を用意する工程と、スルーホールTH内に貫通電極20を形成する工程と、貫通電極20を被覆する第1バリア金属層30aを形成する工程と、素子ZDの接続部に到達するコンタクトホールCH1を形成する工程と、コンタクトホールCH1内の素子ZDの接続部の自然酸化膜を除去する工程と、第1バリア金属層30aを利用して、貫通電極20に接続される第1配線層40と、コンタクトホールCH1を通して素子ZDの接続部に接続される第2配線層40aとを形成する工程とを含む。

(もっと読む)

半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器

【課題】生産性に優れた半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板7の一方の面側に、トランジスタ4のゲート絶縁体層44を形成する第1の工程と、ゲート絶縁体層44上に、厚さ方向に貫通する貫通部91を備える絶縁体層9を形成する第2の工程と、貫通部91内の底部付近のゲート絶縁体層44上、および、貫通部91の周囲の絶縁体層9上に、気相成膜法により同時にかつ互いに接触しないようにそれぞれ電極を形成し、ゲート絶縁体層44上に形成された電極を用いて、ゲート電極45を形成するとともに、絶縁体層9上に形成された電極を用いて、画素電極6を形成する第3の工程とを有する。また、平面視で、貫通部91の開口部の縁が、当該貫通部91の底部の縁より内側に位置する。

(もっと読む)

ポリマの指向性自己組織化を利用するサブリソグラフィ構造の形成方法

【課題】 ポリマの指向性自己組織化を利用するサブリソグラフィ構造の形成方法を提供する。

【解決手段】 ブロック・コポリマの自己組織化を含む方法であって、目標とするCD(限界寸法)を有する開口部(1つ又は複数の基板内の)から開始して、ホールを規則的な配列又は任意の配列に形成する方法を説明する。重要なことに、形成されたホールの平均直径の百分率ばらつきは、最初の開口部の平均直径の百分率ばらつきより小さくなる。形成されたホール(又はビア)を下層の基板に転写することができ、次にこれらのホールを金属導体のような材料で埋め戻すことができる。本発明の好ましい態様は、22nm以下の技術ノードにおいても、より狭いピッチ及びより優れたCDの均一性を有するビアの作成を可能にする。

(もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

ブロック共重合体を用いてホール又はビアを有するデバイスを形成する方法

【課題】 ブロック共重合体を用いて所定の位置にホール又はビアを有するデバイスを形成する方法を提供する。

【解決手段】 例えば、光リソグラフィを用いて、輪郭を付けられた凸状のセグメントによって与えられる断面を有する開口部を基板内に形成する。開口部の断面は、例えば、重なった円形領域によって与えることができる。側壁は、種々の点で隣接し、そこで突起を画定する。ブロック共重合体を含むポリマーの層を開口部及び基板の上に塗布し、自己集合させる。開口部内に個別分離ドメインが形成され、これらを除去してホールを形成し、これを下層の基板に転写することができる。これらのドメイン及びこれらの対応するホールの位置は、側壁及びそれらに付随する突起によって所定の位置に誘導される。これらのホールを隔てる距離は、何も側壁がない場合にブロック共重合体(及び何れかの添加剤)が自己集合したとする場合よりも大きく又は小さくすることができる。

(もっと読む)

半導体構造体及びその形成方法

【課題】 相互接続構造の信頼性及び拡張性を改善する相互接続構造のための冗長金属拡散バリア層を提供する。

【解決手段】 冗長金属拡散バリア層は、誘電体材料内に設けられた開口内に配置され、且つ開口内に存在する拡散バリア層及び導電性材料の間に配置される。冗長拡散バリア層は、Ru並びに純粋なCo若しくはN,B及びPのうちの少なくとも1つを含むCo合金からなる単層若しくは多層構造である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通配線が断線しにくい信頼性の高い半導体装置1および半導体装置1の製造方法を提供する。

【解決手段】第1の主面10Aと第2の主面10Bとを貫通する基板貫通孔10Hが形成された半導体基板と、第1の主面10Aから離れるにしたがい開口が段階的に小さくなる層間膜貫通孔13Hが形成された層間絶縁膜13とデバイス11と接続された再配線層14とを有する多層配線層15と、再配線層14と接続され層間膜貫通孔13Hの開口部を覆う電極パッド16と、電極パッド16から層間膜貫通孔13Hの側壁および基板貫通孔10Hの側壁を介して第2の主面10B側まで配設された貫通配線19と、第2の主面10B側の貫通配線19上に配設されたバンプ21と、を具備する。

(もっと読む)

複合体、複合体の製造方法及び半導体装置

【課題】複合体の樹脂層に形成された高密着、高信頼性、高周波対応の微細配線やビアを有する複合体、複合体の製造方法及び半導体装置を提供する。

【解決手段】樹脂層1と導体層2とを含む第1の複合体100であって、前記樹脂層1の表面に最大幅が1μm以上、10μm以下の溝3と当該溝3内部に導体層2を有し、当該導体層2と接する前記樹脂層1の表面の算術平均粗さ(Ra)が0.05μm以上、0.45μm以下である、及び/又は、前記樹脂層1に直径が1μm以上、25μm以下のビア孔と当該ビア孔内部に導体層2を有し、前記ビア孔内部の樹脂層1の表面の算術平均粗さ(Ra)が0.05μm以上、0.45μm以下であることを特徴とする。

(もっと読む)

C4ボール内の均一な電流密度のための金属配線構造体

【課題】 C4ボール内の均一な電流密度のための金属配線構造体を提供する。

【解決手段】 1つの実施形態において、金属構造体のサブパッド・アセンブリが、金属パッドの直下に配置される。サブパッド・アセンブリは、金属パッドに当接する上位レベル金属ライン構造体と、上位レベル金属ライン構造体とその下方に配置された下位レベル金属ライン構造体との間の電気的接続をもたらす一組の金属ビアとを含む。別の実施形態において、C4ボールの信頼性は、C4ボール内部の均一な電流密度分布を助長するように分割及び分布させた一組の統合された金属ビアを有する金属パッド構造体を用いることによって高められる。複数の金属ビアの断面積の面密度は、金属パッドの中央部分において金属パッドの平担部分の周縁部分よりも高い。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板に素子と貫通電極とが形成された半導体装置の製造方法において、貫通電極からの銅による素子の汚染を防止できる方法を提供する。

【解決手段】半導体基板10と、それに形成された素子ZDと、半導体基板10を貫通するスルーホールTHと、半導体基板10の両面側及びスルーホールTHの内面に形成されて、素子ZDを被覆する絶縁層12とを備えた構造体を用意する工程と、スルーホールTH内に貫通電極20を形成する工程と、貫通電極20を被覆する第1バリア金属パターン層30を形成する工程と、絶縁層12に、素子ZDの接続部に到達するコンタクトホールCHを形成する工程と、コンタクトホールCH内の素子ZDの接続部の自然酸化膜を除去する工程と、第1バリア金属パターン層30に接続されると共に、コンタクトホールCHを通して素子ZDに接続される配線層40,40aを形成する工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース抵抗を低減できる半導体装置およびその製造方法を提供する。

【解決手段】基板10上に配置された窒化物系化合物半導体層12と、窒化物系化合物半導体層12上に配置され、アルミニウム窒化ガリウム層18からなる活性領域AAと、活性領域AA上に配置されたゲート電極24、ソース電極20およびドレイン電極22と、窒化物系化合物半導体層12上に配置され、それぞれゲート電極24、ソース電極20およびドレイン電極22に接続されたゲート端子電極GE1〜GE3、ソース端子電極SE1〜SE4およびドレイン端子電極DEと、ソース端子電極が配置される側の基板の端面に配置され、ソース端子電極と接続された端面電極SC1〜SC4と、端面電極上に配置され、ダイボンディングで使用する半田層がソース端子電極SE1〜SE4に到達するのを防止する突起電極34とを備える半導体装置およびその製造方法。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながら、高いドレイン電流を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上方に形成されたソース電極5s、ドレイン電極5d及びゲート電極5gと、が設けられている。更に、ソース電極5sとゲート電極5gとの間の化合物半導体積層構造2上に形成され、シリコンを含む第1の保護膜6と、ドレイン電極5dとゲート電極5gと間の化合物半導体積層構造2上に形成され、第1の保護膜6より多くシリコンを含む第2の保護膜7と、が設けられている。

(もっと読む)

121 - 140 / 485

[ Back to top ]