Fターム[5F033GG02]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930) | 化合物半導体 (913) | III−V族 (485)

Fターム[5F033GG02]に分類される特許

201 - 220 / 485

半導体装置

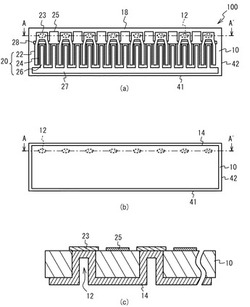

【課題】ビアホールに起因し基板に生じる亀裂を抑制し、かつチップ面積を削減することが可能な半導体装置を提供すること。

【解決手段】本発明は、長方形の基板10と、楕円形状または直線部分をその長軸方向に有するトラック形状からなり、その長軸が基板10の長辺方向に沿って配置されてなるビアホール12と、を具備することを特徴とするである。本発明によれば、ビアホールに起因した基板に生じる亀裂を抑制し、かつチップ面積を削減することができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】外部ストレスによる亀裂などの破損による形状不良や特性不良などの半導体装置の不良を低減することを目的の一とする。よって、信頼性の高い半導体装置を提供することを目的の一とする。また、作製工程中においても上記不良を低減することで半導体装置の製造歩留まりを向上させることを目的の一とする。

【解決手段】一対の第1の耐衝撃層及び第2の耐衝撃層に挟持された半導体集積回路において、半導体集積回路と第2の耐衝撃層との間に衝撃拡散層を有する。外部ストレスに対する耐衝撃層と、その衝撃を拡散する衝撃拡散層とを設けることで、半導体集積回路の単位面積あたりに加えられる力を軽減し、半導体集積回路を保護する。衝撃拡散層は弾性率が低く、破断係数が高い方が好ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート誘電膜を用いるpチャネルFETをゲート先作りプロセスにより形成すると閾値が大きくなる。

【解決手段】High-Kゲート誘電膜104の側面と接触するようにHigh-K誘電膜102を形成した後、酸素雰囲気中でアニールする。

(もっと読む)

半導体装置

【課題】電極パッド上に所望の形状でめっき層を形成できる構成を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、グラウンドに接続された電極パッド3aと、電極パッド3aの上に形成されためっき層6aと、半導体基板1のうち、電極パッド3aの下方に位置する領域を区画する絶縁膜7とを備えている。ウェハ裏面の一部または全部が電極パッド3aと電気的に分離される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極の周囲に形成される空洞と保護膜に形成されるホールとの境界部分の開口を封止しやすい構造を実現する。

【解決手段】半導体装置を、ゲート電極3と、高さが低い部分6Aと高さが高い部分6Bとを有する階段状の空間6をゲート電極3の周囲に有する保護膜4と、高さが低い部分6Aに接するように保護膜4に形成されたホール5とを備えるものとする。

(もっと読む)

メソポーラス材料および方法

【課題】 メソポーラス体およびメソポーラス体を作製する方法を提供する。

【解決手段】 本発明は、鋳型材料を含む鋳型を供給することと、鋳型に前駆体を浸透させること、前駆体を鋳型内で反応させて堆積物を形成すること、および鋳型から鋳型材料を除去してメソポーラス材料を形成すること、によってメソポーラス材料を形成する。

(もっと読む)

半導体素子、および半導体素子の製造方法

【課題】従来の半導体素子の製造方法では、半導体基板2の厚み方向のエッチングがエッチング工程とデポジション工程とを交互に繰り返して進行させられるために、規則的なくぼみが貫通孔1の側壁面に横方向の筋として発生してしまう。その結果、CVD法などにより貫通孔1の側壁面に堆積される前述の絶縁膜の、膜厚の均一性や側壁面に対する密着性が、凹凸構造3aのために悪くなってしまう。そして、その絶縁膜上に形成されるシード層の膜厚の均一性も悪くなってしまうために、続いて貫通孔1にめっき法により導電性物質を充填させることで形成される貫通電極の信頼性が低くなる現象が見られる。

【解決手段】半導体基板2と、半導体基板2に配置された回路素子と、半導体基板2に形成された、筋状の凹凸構造3をその側壁面に有する貫通孔1と、を備え、筋状の凹凸構造3の筋の方向は、半導体基板2の厚み方向である、半導体素子。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通孔底部にノッチを有する半導体装置のノッチ部に被覆性良好な連続した金属膜を積層するプロセスを提供し、半導体装置の歩留まりと信頼性向上をはかること。

【解決手段】ノッチ部を含む貫通孔にCVD絶縁膜を積層した後に、バリア層およびシード層のメタル層をスパッタ法により形成する。メタル層のスパッタ成膜中に基板バイアス(負電圧)を印加して、アルゴンやクリプトン等の希ガスのプロセスガスイオンを貫通孔内部へ引き込み、既にある程度貫通孔底部に積層したメタル層をスパッタエッチングするか、貫通孔底部にメタル層を積層すると同時にスパッタエッチングしたメタル材料を貫通孔底部周辺のノッチ部分へ飛散させる。飛散したメタル材料はノッチ部分の絶縁膜上に付着し積層する。Ar+イオン等により飛散されたメタルは高いエネルギーを有する為、メタル層がノッチ内部へ強固に付着する。

(もっと読む)

基板構造及びその形成方法

【課題】薄膜特性及び接着性が改善が可能な基板構造形成方法及びこれを用いて形成された基板構造を提供する

【解決手段】基板構造を形成する方法は、基板10をエッチングして垂直面51を有するエッチング部50を形成する段階と、基板10の全面上にまたは基板10に部分的に拡散物質層60を形成する段階と、拡散物質層60を熱処理して、一部が上記エッチング部50の表面の下へと拡散したシード層60’を形成する段階、及びシード層60’上に金属層70を形成する段階とを含む。上記方法によれば、シード層60’によって基板10のエッチング部50の表面特性が改善されることもあるので、エッチング部50の垂直面51に接着性に優れ且つ均一な厚さの金属層70を形成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】高精度なドライエッチングを行うことができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、開口幅が小さい密集した複数の開口からなる密集パターンと、開口幅が前記密集パターンの前記開口幅よりも大きい開口からなる幅広パターンとを有し、前記幅広パターンの開口側の角度が180度未満の角近傍に切欠部を設けたレジスト膜を、エッチング対象上に形成する工程と、前記レジスト膜をマスクとして用いて前記エッチング対象に対しドライエッチングを行い、前記レジスト膜の前記密集パターン及び前記幅広パターンを転写する工程とを含む。

(もっと読む)

半導体チップ及び半導体装置

【課題】小型化が可能な半導体チップ及び半導体装置を提供する。

【解決手段】上面、底面、及びこれらの面を接続する側面13を有する半導体基板11と、上面にあり、半導体基板11に形成された半導体素子と接続された上部配線15と、底面にあり、側面13で囲まれた内側に側面13から離間して配置された複数の接続端子26と、半導体基板11を貫通する貫通孔21を通り、上部配線15と接続端子26とを電気接続する貫通配線25と、接続端子26間の底面にあり、接続端子26とは凹部31を隔てて配置された絶縁性の分離膜27とを備えている。

(もっと読む)

半導体基板の電解めっき方法および電解めっき装置

【課題】貫通孔を有するシリコンウエハの貫通孔にオーバーハング形状や内部ボイドがなくめっきを充填する方法を提供すること。

【解決手段】シリコンウエハ内の貫通孔開口部と同位置に開口部を有するプレートを一定の距離をおいてシリコンウエハの貫通孔開口部にプレート開口部を合わせて、めっき電極側に向けて配置してめっきを行う。プレート開口径は貫通孔開口径より少し小さくする。プレート開口径と貫通孔開口径Rの差を2xとしたとき、x/Rを0.1〜0.3、シリコンウエハとプレートの距離を0.05mm〜1.0mmとしたときに、前記課題を実現できる。プレートは、多孔質セラミックのような絶縁体でかつ多孔質材料が望ましく、シリコンウエハ表面のめっき成長も抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の異なる半導体層上においても、良好にゲート電極を形成可能な半導体装置の製造方法を提供する。

【解決手段】絶縁体2上の膜厚の異なる半導体層3a,3bにそれぞれ形成された電界効果型トランジスタを有する半導体装置の製造方法である。まず、膜厚の異なる半導体層3a,3bを絶縁体上に形成する。そして、半導体層3a,3b上にゲート絶縁膜5a,5bを形成し、ゲート絶縁膜5a,5b上にゲート電極材料を積層する。パターニング時におけるフォトリソグラフィに影響を与えない膜厚を有する犠牲膜をゲート電極材料上に形成し、エッチングにより犠牲膜をパターニングするとともに、パターニングされた犠牲膜8aをマスクに用いてゲート電極材料をパターニングしてゲート電極11,12を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】アライメントマークの形成に関連する歩留まりの低下を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】GaN層2及びn型AlGaN層3に、絶縁性基板1の表面まで到達する開口部6を形成する。次に、開口部6内にソース電極4sに接続されるNi層8を導電性エッチングストッパとして形成すると共に、n型AlGaN層3上にアライメントマーク8aを形成する。次に、絶縁性基板1の裏面にフォトレジスト膜を形成し、アライメントマーク8aを基準として、ビア用遮光部及びアライメント用遮光部が設けられたフォトマスクの位置合わせを行う。次に、フォトマスクを用いてフォトレジスト膜からビアホール形成用レジストパターンを形成する。次に、ビアホール形成用レジストパターンを用いて、絶縁性基板1に、その裏面側からNi層8まで到達するビアホール1sを形成する。そして、ビア配線16を形成する。

(もっと読む)

半導体装置

【課題】従来の半導体装置に比べてさらなる小型化を可能とする、複数の半導体素子が並列に接続された半導体装置を提供する。

【解決手段】半導体装置1は、ソース領域15と、ドレイン領域17と、ゲート領域16とを有するJFET10を複数個備えている。複数個のJFET10は、ソース領域15同士を接続するソース電極25と、ドレイン領域17同士を接続するドレイン電極27と、ゲート領域16同士を接続するゲート電極26とにより並列に接続されている。ソース電極25は、ソース電極25を外部と接続するソース電極パッド25Aを含んでいる。ドレイン電極27は、ドレイン電極27を外部と接続するドレイン電極パッド27Aを含んでいる。そして、ソース電極パッド25Aおよびドレイン電極パッド27Aは、絶縁体からなる絶縁保護膜28を挟んでゲート電極26の上側に突出するように形成されている。

(もっと読む)

半導体チップ及び半導体装置

【課題】半導体基板の裏面側から効率よく放熱する半導体チップを実現できるようにする。

【解決手段】半導体チップ10は、基板11と、基板11の素子形成面側に形成され、複数の半導体素子を含む集積回路12と、基板11における複数の半導体素子のうちの所定の半導体素子30と対応する領域に形成さた放熱プラグ31とを備えている。放熱プラグ31は、素子形成面と反対側の面に開口する非貫通孔に埋め込まれた基板11と比べて熱伝導率が大きい材料からなる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間容量を低減する。

【解決手段】半導体装置70には、積層形成される配線膜6及び10から構成される配線層が設けられる。キャップ膜3上に形成される層間絶縁膜4の第1の開口部には、配線膜6が埋設される。配線膜6の底部及び側面部にはバリアメタル膜5が設けられる。層間絶縁膜4及び配線膜6上に形成されるキャップ膜7及び層間絶縁膜8の第2の開口部には、配線膜10が埋設される。配線膜10の底部及び側面部にはバリアメタル膜9が設けられる。層間絶縁膜8及び配線膜10上に形成される。配線膜10は配線膜6上に設けられ、配線膜10の端部は配線層6の端部よりも内側に設けられる。

(もっと読む)

半導体チップ、光電変換チップおよび半導体チップの製造方法

【課題】衝撃や振動になどに対して強度を向上させることで高い信頼性が得られる半導体チップ、光電変換チップおよび半導体チップの製造方法を提供する。

【解決手段】半導体基板2と、受光部3および制御回路部4とを形成する集積回路と、前記半導体基板2の側面に形成され、半円筒形状に形成された外部端子5と、底面を除く全体を覆う樹脂封止部6とを備えた光電変換チップ1は、プリント配線基板に搭載する場合に、ワイヤによる接続が不要なので、ワイヤボンディング工程が不要である。

(もっと読む)

積層体およびその製造方法

【課題】リーク電流を低減された積層体およびその製造方法を提供する。

【解決手段】積層体は、基材と、前記基材の上方に設けられたシリカ系絶縁部と、前記シリカ系絶縁部に設けられた導電部と、前記シリカ系絶縁部および前記導電部の上に設けられたバリア層と、を含み、前記バリア層はポリカルボシランを含む。

(もっと読む)

多層配線用パッド構造およびその製造方法

【課題】プローブをパッドに接触させる際の接触不良およびプローブ破損の発生を抑制できる多層配線用パッド構造およびその製造方法を提供すること。

【解決手段】第1の配線2が形成されている半導体基板1に、第1の層間絶縁膜3、第1のコンタクトホール6、第2の配線11と第1の層間絶縁膜3との間の密着性を向上するためのW系金属薄膜7、第2の配線11を形成するためのめっき用金属薄膜8、第2の配線11、第2の層間絶縁膜12、第2のコンタクトホール13、第3の配線16と第2の層間絶縁膜12との間の密着性を向上させるためのW系金属薄膜14、第3の配線16を形成するためのめっき用金属薄膜15、第3の配線16が形成され、パッド中央17の表面は平坦で、パッド端18は下側に曲がっていることを特徴とする多層配線用パッド構造を構成する。

(もっと読む)

201 - 220 / 485

[ Back to top ]