Fターム[5F033GG02]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930) | 化合物半導体 (913) | III−V族 (485)

Fターム[5F033GG02]に分類される特許

81 - 100 / 485

シリコンおよびIII−V族のモノリシック集積デバイス

【課題】シリコン基板上にIII−V族半導体で形成されたHEMTとシリコン面に形成されたショツトキーダイオードのモノリシック集積デバイスを開示する。

【解決手段】少なくとも1つのビアは、III−V族半導体を通じて延在して、III−V族トランジスタの少なくとも1つの端子をシリコン基板に形成されたシリコンデバイスに結合させる。シリコンデバイスはショットキーダイオードと、III−V族トランジスタはGaNHEMTとすることができる。ショットキーダイオードのアノードは、一実施形態においては、シリコン基板202に形成され、他の実施形態においては、シリコン基板上の低濃度にドープされたエピタキシャルシリコン層204に形成される。HEMTはGANで構成されたチヤネル層212、AlGaNで構成された電子供給層214より構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】簡便に半導体集積回路を小領域に電気的に分離する。

【解決手段】厚さが150〜600μm程度のInP基板、GaAs基板等の化合物半導体基板1の表面に半導体集積回路2を形成し、化合物半導体基板1の裏面(半導体集積回路2が形成された表面とは反対側の面)に、直角に交わっている複数の切込溝3を設け、半導体集積回路2の表面から切込溝3の底面までの距離を50〜150μmとし、切込溝3内にAu等の金属4を埋め込み、金属4を化合物半導体基板1の裏面全面にも設ける。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

電界効果トランジスタ及びその製造方法

【課題】デバイス特性を維持し、ゲートリーク電流を低減できる電界効果トランジスタ及びその製造方法を提供する。

【解決手段】本発明に係る電界効果トランジスタ100は、III−V族窒化物半導体層構造と、半導体層構造上に離間して形成されたソース電極105及びドレイン電極106と、ソース電極105及びドレイン電極106の間に形成されたゲート電極108と、ソース電極105上及びドレイン電極106上に形成された電極保護膜107と、半導体層構造上に、ソース電極105、ドレイン電極106、ゲート電極108及び電極保護膜107の上面の少なくとも一部を覆うように形成され、半導体層構造を保護する第1のパッシベーション膜109を備え、第1のパッシベーション膜109は、所定の材料に対して化学的に活性であり、電極保護膜107は、所定の材料に対して化学的に不活性な金属である。

(もっと読む)

スパッタリング用ターゲットおよび半導体装置の製造方法

【課題】スパッタリング用ターゲットから垂直方向に叩き出されるターゲット原子の個数を増大させる。

【解決手段】薄膜形成に用いられるターゲット原子Pから構成されたターゲット5において、ターゲット5から斜め方向に叩き出されたターゲット原子Pを側壁に衝突させることでターゲット原子Pがターゲット5から放出されるのを遮る凹部5aを表面に形成する。

(もっと読む)

ビア及びエッチングされた構造におけるコンフォーマル絶縁層の形成方法及びパターン形成方法

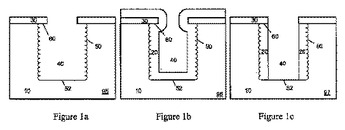

マスク層の下にアンダーカット形状を形成するエッチングプロセスによって基板にビアが形成される。ビアはコンフォーマルな絶縁層で覆われ、この構造にエッチングプロセスを実施して水平面から絶縁層を取り除くと共にビアの垂直な側壁の絶縁層を残す。ビアの上部領域はエッチバックプロセスの際、アンダーカットハードマスクによって保護される。  (もっと読む)

(もっと読む)

ドライエッチング方法

【課題】コストの上昇を招くことなく、より安定した状態でInPの層がドライエッチング法によりエッチングできるようにする。

【解決手段】塩素ガスを用いたドライエッチング法によりマスクパターン106をマスクとして基板101を選択的にエッチングすることで、基板101にビアホール(開口パターン)107を形成する。例えば、温度条件を200℃程度とし、塩素ガスを用いた反応性イオンエッチング法によりエッチングすればよい。

(もっと読む)

半導体装置

【課題】本発明は小型化を図ると共に、デバイス形成層を保護した状態で貫通孔及び貫通電極を形成することを課題とする。

【解決手段】デバイス形成層18と電極パッド20を有する半導体素子14の電極パッド20と半導体素子14の他面側に形成された再配線パターン52とを接続する貫通電極56を有する半導体装置50であって、半導体素子14の上面側にデバイス形成層18及び電極パッド20を形成し、電極パッド20及びデバイス形成層18の表面に第1レジスト層62を形成し、電極パッド20にエッチングにより開口64を形成し、開口64に連通する位置に貫通孔54をエッチングにより半導体素子14に形成する。第1レジスト層62によりデバイス形成層18を保護すると共に、貫通電極56を設けてフリップチップ接続を可能にして小型化を図る。

(もっと読む)

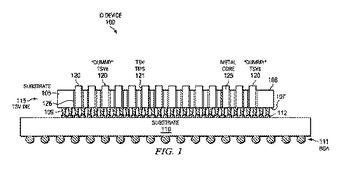

ICデバイスのエンハンストされた熱放散のための突出するTSV

集積回路デバイス(100)が、基板パッド(102)を含む上面を有する基板(110)、及び能動回路を含む上部半導体表面(107)と(底面)106とを含む半導体基板(105)を含む複数の基板貫通ビア(115)ダイを含む。上部半導体表面(107)は、基板の上面上の基板パッドに結合されるボンドコネクタ109を含む。複数の基板貫通ビア(TSV)が、底面から外に延びる突出するTSVティップ(121)に上側半導体表面から延びる内部金属コア(125)を含む。複数のTSVの少なくとも1つが、そこへの如何なる電気的接続もない、突出するTSVティップを有し、TSVダイの底面からの熱消散を可能にするための付加的な表面領域を提供するダミーTSV(120)である。

(もっと読む)

(もっと読む)

半導体装置製造方法及び積層半導体装置

【課題】複数の基板を貼り合わせる積層半導体装置を効率よく製造できる方法を提供する。

【解決手段】複数の基板を貼り合わせて積層半導体装置を製造する半導体装置製造方法であって、回路が形成された複数の基板のうちの一の基板に凹部を形成する凹部形成ステップと、一の基板を複数の基板のうちの他の基板に重ね合わせる重ね合わせステップと、重ね合わせステップの後に、一の基板の凹部に導電性材料を導入することにより、一の基板の回路と他の基板の回路との間の電気的な導通路を形成する導通形成ステップとを備える半導体装置製造方法が提供される。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

窒化物半導体装置

【課題】パワートランジスタに適用可能なノーマリオフ型の窒化物半導体装置に生じる電流コラプスを抑制できるようにする。

【解決手段】窒化物半導体装置は、サファイアからなる基板11と、該基板11の上に形成されたGaNからなるチャネル層13と、該チャネル層13の上に形成され、該チャネル層13よりもバンドギャップエネルギーが大きいAlGaNからなるバリア層14と、該バリア層14の上に形成され、p型AlGaN層15及びp型GaN層16を含むp型窒化物半導体層と、該p型窒化物半導体層の上に形成されたゲート電極19と、該ゲート電極19の両側方の領域にそれぞれ形成されたソース電極17及びドレイン電極18とを有している。p型窒化物半導体層は、ゲート電極19の下側部分の厚さが該ゲート電極19の側方部分の厚さよりも大きい。

(もっと読む)

半導体装置

【課題】 パッケージに封止される半導体素子は、使用環境によって湿度の影響を受けて、半導体素子の劣化が起こることがある。パッケージに実装することが容易で、半導体素子周囲の湿度・水分量を測定・記録できる湿度センサを得る。

【解決手段】 半導体基板2上に形成した絶縁膜7の上に、水溶性金属の薄膜8を用いた湿度センサ6を形成し、水溶性金属の薄膜8の抵抗を測定する。水溶性金属とは、電位−pH図において、電位がゼロ、pHが7付近で腐食域にある金属を意味する。

(もっと読む)

金属キャリアを有する半導体デバイスおよび製造方法

【課題】 金属キャリアを有する半導体デバイス及び製造方法を提供する。

【解決手段】 金属キャリア基板を含む半導体デバイス。キャリア基板の上には、Alx1Gay1Inz1N(x1+y1+z1=1、x1≧0、y1≧0、z1≧0)の第1の半導体層が形成される。第1の半導体層の上にはAlx2Gay2Inz2N(x2+y2+z2=1、x2>x1、y2≧0、z2≧0)の第2の半導体層が配され、第2の半導体層の上にはゲート領域が配置される。半導体デバイスはさらに、ソース領域およびドレイン領域を含み、これらの領域のうちの一方が金属キャリア基板と電気的に接続され、第1の半導体層を介して延在する導電性領域を含む。

(もっと読む)

電子デバイスの製造方法および該方法により製造された電子デバイス

GaAs半導体基板(HS)を備えた電子デバイスにおいて、基板前面には半導体素子(BE)が、基板背面には多層の背面金属化部(RM)が設けられている。このような電子デバイスのために、背面金属化部の有利な積層体構造が提案される。たとえば背面金属化部は固着層としてAu層を有している。  (もっと読む)

(もっと読む)

電子装置の切断方法

【課題】半導体装置を含む電子装置の製造コストの増大を抑制可能であり、かつ、低誘電体膜の損傷を防止可能な電子装置の切断方法を提供すること。

【解決手段】本電子装置の切断方法は、基板上に複数の絶縁層及び複数の配線層が積層されている電子装置を準備する第1工程と、ブラスト処理を含む工程により、前記電子装置の切断可能領域に存在する全配線層及び全絶縁層を除去して前記基板を露出させる第2工程と、前記切断可能領域に露出する前記基板をブレードにより切断する第3工程と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の良好な半導体装置及びその製造方法を提供することにある。

【解決手段】一方の主面に於ける半導体素子領域2内に複数の機能素子が配設された半導体基板1と、半導体基板1の一方の主面上に配設され、複数の配線層3と複数の絶縁層4とを含む多層配線層2と、多層配線層2上に形成された第1の有機絶縁物層6と、第1の有機絶縁物層上に形成され、配線層に電気的に接続された他の配線層と、第1の有機絶縁物層6上に、他の配線層を覆うように形成された第2の有機絶縁物層10とを具備し、半導体素子領域を囲む半導体基板領域に、多層配線層を貫く溝が半導体素子領域を囲繞して配設されており、溝内には、前記有機絶縁物層6、有機絶縁物層10のいずれからも分離された有機絶縁物が配設されている。

(もっと読む)

半導体装置

【課題】半導体装置を構成するトランジスタを製造する際にトランジスタ能力のばらつきが発生しても、期待通りの性能を発揮することができる半導体装置を提供する。

【解決手段】半導体基板100上に、トランジスタ104A及び104Bと、電極パッド106とが形成されている。電極パッド106の上側領域を除く半導体基板100を覆うように、保護膜107が形成されている。トランジスタ104Aの上側領域を除く保護膜107を覆うように、凸方向に応力160を生じる保護膜108が形成されている。保護膜108によって、トランジスタ104Bの能力を基準として、トランジスタ104Aの能力が相対的に高く又は低く変動している。

(もっと読む)

半導体装置及びその製造方法

【課題】放熱性に優れ、製造歩留まりの向上を図ることができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】

半導体装置は、基板1の上方に設けられた化合物半導体層2,3,4と、化合物半導体層2,3,4の上方に設けられた複数のソース電極7及び複数のドレイン電極9と、化合物半導体層2,3,4を貫通し、複数のソース電極7のそれぞれに接続される複数のビア配線22と、化合物半導体層2,3,4を貫通し、複数のドレイン電極9のそれぞれに接続される複数のビア配線23と、複数のビア配線22に接続され、基板1に埋め込まれたソース共通配線18と、複数のビア配線23に接続され、基板1に埋め込まれたドレイン共通配線20とを有する。

(もっと読む)

半導体装置のパッド構造

【課題】半導体装置のパッド構造を提供する。

【解決手段】半導体装置200は、半導体基板202、相互接続構造、複数のダミーメタルビア235及びパッド構造を備える。半導体基板202は、内部に複数の微小電子素子が設けられている。相互接続構造は、半導体基板202上に設けられ、複数の金属層210a〜210iと、金属層を隔離する複数のIMD層220とを有する。金属層210a〜210iは、最上金属層210iと、最下金属層210aと、最上金属層210iと最下金属層210aとの間に設けられた少なくとも2層の金属層とを含む。複数のダミーメタルビア235は、少なくとも2層の金属層間に設けられた1層又は2層以上のIMD層220内に形成される。パッド構造は、ダミーメタルビア235の上に直接設けられている。

(もっと読む)

81 - 100 / 485

[ Back to top ]