Fターム[5F033HH33]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 化合物 (5,420) | 窒化物 (4,637) | TiN (2,127)

Fターム[5F033HH33]に分類される特許

201 - 220 / 2,127

半導体装置

【課題】工程数の増大を抑制しつつ、チップ上に形成された再配線または突出電極の信頼性を向上させる。

【解決手段】配線2bおよびパッド電極2aが形成された半導体基板と、半導体基板上に形成された応力緩和層4と、応力緩和層4上に合金シード膜5を形成した後、応力緩和層4と合金シード膜5とを熱処理にて反応させることで、応力緩和層4と合金シード膜5との間に反応性バリア絶縁膜6を形成する。再配線8または突出電極は合金シード膜5上に形成する。

(もっと読む)

半導体装置の製造方法

【課題】低コストで、かつ簡便な方法で、コンタクトプラグ上に形成される銅配線の上面にヒロックが生じて短絡が発生することを抑制可能な半導体装置の製造方法を提供する。

【解決手段】配線13を覆う層間絶縁膜15の上面に、層間絶縁膜よりもエッチング速度の遅いエッチングストッパ膜16を形成する。エッチングストッパ膜のうち、配線と対向する部分を貫通する第1の開口部16Aを形成する。エッチングストッパ膜よりも層間絶縁膜がエッチングされやすい条件を用いて、配線の上面が露出するまで第1の開口部の下方に位置する層間絶縁膜をエッチングして、第1の開口部と共にコンタクトホールを構成する第2の開口部15Aを形成する。第1の開口部を埋め込むように、コンタクトホール内に導電膜を成膜することでコンタクトプラグ27を形成する。電解メッキ法により、コンタクトプラグの上面と接触する銅配線39を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

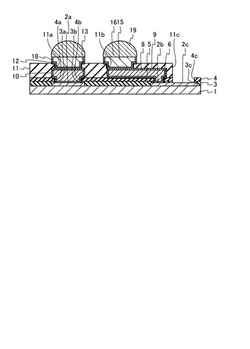

【課題】半導体層の表面から貫通孔絶縁層が後退した場合においても、半導体層と貫通電極との絶縁性を確保する。

【解決手段】貫通孔6には、貫通孔絶縁層7、8を介して貫通電極9が埋め込まれ、貫通孔絶縁層7、8は、半導体層3の表面から後退するようにして形成され、半導体層3と貫通電極9との間には、貫通孔絶縁層7、8の後退部分の対応した凹部10が形成され、貫通電極9の側壁には、凹部10に埋め込まれたサイドウォール絶縁膜12が形成される。

(もっと読む)

パターン化金属膜及びその形成方法

【課題】ドライエッチングが困難な遷移金属の膜を、サイドエッチングが極力生じないようにパターニングする。

【解決手段】絶縁膜の上にバリア層・密着層を形成し(S1)、その上に遷移金属からなるシード層を形成する(S2)。シード層の上にSiO2膜及びフォトレジスト膜を順次形成し(S3、S4)、フォトレジスト膜、SiO2膜をパターニングして開口を形成し(S5,S6)、開口内にCu膜及びマスクAl膜を積層する(S7、S8)。次に、SiO2膜をエッチング(S9)、露出したシード層をその膜厚方向に異方的に改質し(S10)、改質されたシード層、露出したバリア・密着層、及びマスクAl膜を順次エッチングにより除去することにより(S10〜S13)、パターン化金属膜を得る。

(もっと読む)

カーボンナノチューブ配線の製造方法

【課題】カーボンナノチューブを有するプラグ配線において良好な電気的接続を得ることができるカーボンナノチューブ配線の製造方法を提供する。

【解決手段】第1配線層12上に層間絶縁膜13を形成する工程と、第1配線層上の層間絶縁膜内にコンタクト孔15を形成する工程と、コンタクト孔内の第1配線層上にカーボンナノチューブ16を成長させ、コンタクト孔から先端が突き出た複数のカーボンナノチューブを形成する工程と、層間絶縁膜上及び複数のカーボンナノチューブ間に、ストッパ膜17を形成する工程と、ストッパ膜上及び複数のカーボンナノチューブ上に絶縁膜を形成する工程と、ストッパ膜をストッパとして用い、ストッパ膜上の絶縁膜と共に、コンタクト孔上の複数のカーボンナノチューブを除去する工程と、複数のカーボンナノチューブ上に第2配線層14を形成する工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスにより金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】部分反応方式のサリサイドプロセスによりゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの表面に金属シリサイド層41を形成する。金属シリサイド層41を形成する際の第1の熱処理では、熱伝導型アニール装置を用いて半導体ウエハを熱処理し、第2の熱処理では、マイクロ波アニール装置を用いて半導体ウエハを熱処理することにより、第2の熱処理を低温化し、金属シリサイド層41の異常成長を防ぐ。これにより金属シリサイド層41の接合リーク電流を低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極の幅を十分に確保して、ゲート電極の抵抗値を小さくすることが可能で、かつゲート電極間の容量を小さくすることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板に設けられ、Y方向に延在する第1の溝15と、半導体基板に設けられ、第1の溝15と交差するXの方向に延在する第2の溝25と、第1及び第2の溝15,25に囲まれ、第2の溝25に露出された対向する第1及び第2の側面26a,26bを有するピラー26と、ゲート絶縁膜28を介して、ピラー26の第2の側面26bに接触するように、第2の溝25の下部に設けられた1つのゲート電極29と、ゲート電極29の側面とピラーの第1の側面26aとの間に配置された空隙と、を有する。

(もっと読む)

半導体装置の作製方法及び表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して、信頼性の高い半導体

装置を作製する方法を提供する。

【解決手段】基板上に導電層を形成し、該導電層上に光透過層を形成し、該光透過層上か

らフェムト秒レーザを照射して、該導電層及び該光透過層を選択的に除去する工程を有す

る。なお、該導電層の端部は、該光透過層の端部より内側に配置されるように該導電層及

び該光透過層を除去されていてもよい。また、フェムト秒レーザを照射する前に、該光透

過層表面に撥液処理を行ってもよい。

(もっと読む)

半導体装置、半導体装置の製造方法、及び半導体装置の検査方法

【課題】層間絶縁膜に生じたボイドを高感度に検出する。

【解決手段】この半導体装置は、多層配線層(非図示、以下略)と、多層配線層中に形成された第一TEGパターン(非図示)を備える。第一TEGパターンは、互いに平行に延伸した複数の第一下層配線402と、層間絶縁膜(非図示)を貫通し、平面視で第一下層配線402間に位置する第一ビア602と、多層配線層の最上層(非図示)に形成され、第一ビア602に接続している第一端子762と、上記した同一の最上層に形成され、第一下層配線402に接続している第二端子764と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】 接続孔のホールサイズについて制御性良い半導体装置の製造方法を提供する。

【解決手段】 実施形態の半導体装置の製造方法では、半導体基板上に上層絶縁膜が形成され、前記上層絶縁膜上にSiを含む非晶質膜が形成される。前記非晶質膜上に第1のレジスト膜が形成され、前記第1のレジスト膜に第1のレジストパターンが形成される。前記第1のレジスト膜をマスクとして、前記非晶質膜が加工され、前記上層絶縁膜が露出される。前記第1のレジストパターンが除去され、前記非晶質膜および露出した前記上層絶縁膜上に遷移金属膜が形成される。前記非晶質膜および前記遷移金属膜の熱反応により、前記非晶質膜よりも体積が大きいシリサイド膜が形成される。前記遷移金属膜が除去され、前記シリサイド膜をマスクとして、前記上層絶縁膜を加工し、前記上層絶縁膜に第1の溝が形成される。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

液晶表示装置及びその製造方法

【課題】製造に際して配線にヒロックが発生せず、かつエッチング形状の制御が容易な液晶表示装置を提供する。

【解決手段】液晶表示装置は、基板上にマトリクス配置された走査線と、信号線12と、前記走査線及び信号線に接続される薄膜トランジスタと、前記薄膜トランジスタに接続される画素電極27とを有する液晶表示装置において、前記走査線が下層からアルミニウム−ネオジム合金層211と高融点金属層212との積層構造からなり、前記信号線12が下層から高融点金属層231とアルミニウム−ネオジム合金層232と高融点金属層233との3層構造からなり、高融点金属の種類に応じて、ネオジム含有量を調整する。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】保護膜(Al2O3)の膜質変化に起因するTFT特性のばらつきを軽減することが可能な薄膜トランジスタの製造方法を提供する。

【解決手段】TFT1の製造プロセスにおいて、ソース・ドレイン電極15上に、第1保護膜16(Al2O3層)とAl層とをこの順に、スパッタリングにより連続的に成膜する。各層のスパッタリングでは、いずれもターゲットとしてアルミニウムを用いるが、Al2O3層の成膜過程では、反応ガスとして使用する酸素ガスによってターゲット表面が変質し易い。その後、連続してAl層を成膜する(酸素ガスを使用しないスパッタリングを行う)ことで、ターゲット表面が改質される(成膜処理の度に、ターゲット表面が改質される)。従って、成膜処理回数が増しても、保護膜における膜厚や屈折率が変化しにくい。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

貫通配線基板の製造方法及び貫通配線基板

【課題】貫通孔の底面部付近において、導電層をカバレッジ良く形成し、接触不良がなく、電気的な安定性を向上させた貫通配線を、工程やコストを増加することなく形成する。

【解決手段】半導体基板の一方の面に第一絶縁層を介して導電部を形成する第一工程、ドライエッチング法により半導体基板の他方の面側から第一絶縁層が露呈するように貫通孔を形成する第二工程、貫通孔の内壁面および底面に第二絶縁層を形成する第三工程、第二絶縁層及び第一絶縁層のうち貫通孔の底面に位置する部分を除去し導電部を露呈する第四工程、第二絶縁層上に導電層を形成し該導電層を導電部と電気的に接続する第五工程、を有し、第四工程において、第二絶縁層に続いて導電部の一部をエッチングすると共に、エッチングにより除去された第一金属成分とエッチングガス成分とからなる第一副生成物を、貫通孔の底面部及びその近傍に位置する内壁面部に堆積させ、テーパー部を形成する。

(もっと読む)

埋め込み配線を備える基板、その製造方法、これを利用する半導体装置およびその製造方法

【課題】 低抵抗の埋め込み配線を備える基板の製造方法を提供する。

【解決手段】 始めに半導体用基板100の第1面S1上に導電層120を形成する。次に、導電層120をパターニングして第1方向に延長する線形の導電層パターン122を形成する。導電層120をパターニングするとき露出する半導体用基板100をエッチングして導電層パターン120の下部に第1方向に延長する線形の半導体パターン104を形成する。次に導電層パターン120および半導体パターン104上に絶縁層150を形成する。半導体用基板100の第1面S1側の絶縁層150が支持基板160と当接するように支持基板160上に配置する。次に半導体用基板100のイオン注入層102側の絶縁層150が露出するように半導体用基板100を除去する。これにより、導電層パターン120は、半導体パターン104の埋め込み配線として利用することができる。

(もっと読む)

半導体装置

【課題】pn接合ダイオードの接合面積を大きくし、かつコストダウンを可能とすること。

【解決手段】半導体基板10とpn接合を形成する第1拡散領域32を含む第1pnダイオード33を含み、前記半導体基板上に形成された電子回路20と、前記電子回路とスクライブライン26との間の前記半導体基板内に設けられ前記電子回路を囲み前記第1拡散領域と同じ導電型であり前記半導体基板とpn接合を形成する第2拡散領域24を、含む第2pnダイオード23と、前記電子回路と前記スクライブラインとの間の前記半導体基板上に、前記第2拡散領域と重なるように設けられ、前記電子回路を囲む金属層18と、を具備する半導体装置。

(もっと読む)

半導体デバイス用基板洗浄液及び洗浄方法

【課題】基板表面を腐食することなく微粒子付着による汚染、有機物汚染及び金属汚染を同時に除去することができ、しかも水リンス性も良好で、短時間で基板表面を高清浄化することができる半導体デバイス用基板洗浄液を提供する。

【解決手段】

半導体デバイス製造における化学的機械的研磨工程の後に行われる、半導体デバイス用基板の洗浄工程に用いられる洗浄液であって、以下の成分(A)〜(D)を含有してなる半導体デバイス用基板洗浄液。

(A)有機酸

(B)スルホン酸型アニオン性界面活性剤

(C)ポリビニルピロリドン及びポリエチレンオキシド−ポリプロピレンオキシドブロック共重合体から選ばれる少なくとも1種の高分子凝集剤

(D)水

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の検査特性を向上させる。

【解決手段】本発明の半導体装置の製造方法は、(a)基板の上方にアルミニウムを含有する導電性膜(アルミニウム膜10b)を形成する工程と、(b)上記導電性膜をパターニングすることにより配線を形成する工程と、(c)上記配線の上部に第1絶縁膜(第1保護膜)を形成する工程と、を有する。さらに、(d)上記第1絶縁膜をエッチングすることにより、上記配線のパッド領域(Pd)を露出する工程と(e)上記パッド領域(Pd)に、窒素系のプラズマガスを用いたプラズマ処理を行う工程と、(f)上記(e)工程の後、上記パッド領域(Pd)にプローブ針を当接し、上記パッド領域(Pd)に通電する工程と、を有する。上記(e)工程により、上記パッド領域(Pd)に窒化アルミニウム層(15)が形成され、パッド領域(Pd)とプローブ針(N)との接触抵抗を低減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】回路を形成した半導体ウェハをダイシングするときに発生するクラックの伝搬を抑制する。

【解決手段】ウェハ1上のチップ領域2にMOSトランジスタT1及び配線31,48,54,64,64を形成すると共に、チップ領域2内でMOSトランジスタT1及び配線31,48,54,64,64を囲むガードリング76を形成する。また、ウェハ1上のスクライブライン領域3には、チップ領域2に第1層の配線31を形成するときに、第1の応力吸収パターン33を同時に形成する。さらに、最上層の配線74を形成するときに、第2の応力吸収パターン77を同時に形成する。各応力吸収パターン33,77は、チップ領域2を囲むように連続して形成され、スクライブライン領域3の中心線SCを跨ぐベタパターンである。ダイシング時には、第1及び第2の応力吸収パターン33,77の一部が残るようにウェハ1を切断する。

(もっと読む)

201 - 220 / 2,127

[ Back to top ]