Fターム[5F033JJ01]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | コンタクト層なし、上層配線と一体形成 (1,607)

Fターム[5F033JJ01]に分類される特許

101 - 120 / 1,607

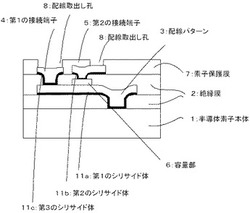

半導体素子

【課題】熱(工程)に耐性のある配線構造を採用し、配線上の析出物の発生を抑制できる半導体素子を実現する。

【解決手段】半導体素子本体に接続する金材を含む配線パターンと、この配線パターンに一端側が接続され金材を含む接続端子と、前記半導体素子本体と前記配線パターンと前記接続端子とを覆う絶縁体と、を具備する半導体素子において、前記配線パターンあるいは接続端子の一方の面に一面が接し他面が前記絶縁体に接する面状のシリサイド体を具備したことを特徴とする半導体素子である。

(もっと読む)

半導体装置

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

Cu合金膜、及びそれを備えた表示装置または電子装置

【課題】基板及び/又は絶縁膜との高い密着性を有し、且つ、液晶表示装置などの製造過程で施される熱処理後も低い電気抵抗率を有する新規なCu合金膜を提供する。

【解決手段】基板上にて、基板及び/又は絶縁膜と直接接触するCu合金膜であって、前記Cu合金膜は基板側から順に、合金成分としてX(Xは、Ag、Au、C、W、Ca、Mg、Al、Sn、BおよびNiよりなる群から選択される少なくとも一種の元素)を含有するCu−Mn−X合金層(第一層)と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる層(第二層)で構成されたCu合金膜である。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】デュアルダマシン法を用いて層間絶縁膜内にCu配線を形成する際、硬度が低い層間絶縁膜および硬度が高い層間絶縁膜のそれぞれに形成されたビアホール内に配線材料を良好に埋め込むことができるようにする。

【解決手段】第2層間絶縁膜17には、配線溝30aとビアホール28aとが形成されている。また、ビアホール28aの開口部には、第2層間絶縁膜17を斜め下方に後退(リセス)させることによって、テーパ状の断面形状を有するリセス部31が形成されている。これにより、ビアホール28aの開口部の直径は、開口部よりも下方の領域の直径に比べて大きくなり、ビアホール28aの直径が微細な場合であっても、ビアホール28aの内部に配線材料を良好に埋め込むことができる。

(もっと読む)

半導体積層体の製造方法

【課題】信頼性の高い半導体積層体を製造することのできる半導体積層体の製造方法を提供する。

【解決手段】貫通電極用溝2が形成されたウエハ1の貫通電極用溝2を有する面に、半導体加工用テープ4を介して支持体5を積層する工程(1)と、ウエハ1を半導体加工用テープ4と反対側の面から研削し、貫通電極用溝2を露出させる工程(2)と、露出した貫通電極用溝2に電極部6を形成する工程(3)と、ウエハ1の半導体加工用テープ4と反対側の面に封止樹脂層7を形成する工程(4A)と、封止樹脂層7を介してウエハ1にダイシング用テープ8を貼り合わせ、半導体加工用テープ4及び支持体5を剥離する工程(4B)と、ウエハ1を個片化して半導体チップを作製する工程(5)と、前記半導体チップを、封止樹脂層7を介して他の半導体チップ又は基板に積層する工程(6)とを有する。

(もっと読む)

電気光学装置の製造方法

【課題】素子基板に絶縁膜を成膜した際にフッ素が混入しても、電界効果型トランジスターに特性異常が発生することを防止することのできる電気光学装置の製造方法を提供すること。

【解決手段】素子基板10にシリコン酸化膜からなる絶縁膜12を成膜する第1絶縁膜成膜工程の後、画素トランジスター30(電界効果型トランジスター)の半導体層1aを形成する半導体層形成工程を行う前に、絶縁膜12に水素を導入する第1絶縁膜水素導入工程を行う。また、シリコン酸化膜からなる層間絶縁膜41を形成する第2絶縁膜成膜工程の後、層間絶縁膜41に対して水素の導入を行う第2絶縁膜水素導入工程を行う。このため、絶縁膜12や層間絶縁膜41にフッ素が混入していた場合でも、かかるフッ素は、水素と結合してフッ化水素として放出される。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置における配線形状を改善すること。

【解決手段】半導体装置の製造方法は、溝領域を規定する第1パターンを有する第1マスクを、サイドウォール形状の転写により、半導体装置の層間膜に設けられた金属膜上に形成する工程と、前記第1パターンに重なる少なくとも一つの開口を有する第2マスクを、平面図で見た場合に、前記2マスクが前記第1マスクに重なり、前記開口が前記溝領域に重なるように、形成し、第2パターンを形成する工程と、前記第1及び第2マスクを介して、前記層間膜をエッチングし、前記第1パターンを前記層間膜に転写させる工程と、前記第2マスクを介して前記層間膜をエッチングし、前記第2パターンを前記層間膜に転写させる工程とを具備する。前記第1パターンは、前記第2パターンとは異なる深さで前記層間膜に形成される。

(もっと読む)

電極構造及びその製造方法

【課題】ウェハハンドリングが容易であり、高精度の位置合わせを必要とせず、ビアホールとして機能する開口部を浅く形成でき、さらに開口部を埋め込む第1電極と基板との界面の割れを防止できる電極構造、及びその製造方法を提供することにある。

【解決手段】基板に、第1主表面側から、深さが基板の厚さよりも小さい開口部33を形成する。次に、開口部を埋め込む第1電極35を形成する。次に、第1主表面と対向する基板を第2主表面側から薄層化して、開口部の深さよりも大きい厚さとする。次に、第2主表面側111bから開口部の底面33bへ向けて、基板111に切り込みを入れる39ことによって、第2主表面側から第1電極を露出させる。次に、切り込みを埋め込む第2電極44を形成する。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

半導体装置

【課題】LSIチップの製造コストを低減することが可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板に形成され、第1の電源配線を含む第1の電源配線層を備える複数のLSI領域と、前記半導体基板に形成された第1の電源端子と、前記LSI領域の間のダイシングライン領域に、前記LSI領域と前記ダイシングライン領域とを区画するダイシングラインに沿って形成され、前記第1の電源配線と前記第1の電源端子とを電気的に接続する第2の電源配線を含む第2の電源配線層と、を備える。少なくとも前記LSI領域において、前記第1の電源配線と前記第2の電源配線との境界にバリアメタル膜が形成されている。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

半導体チップ及びその製造方法、並びに半導体装置

【課題】ダイシング工程で発生し得る裏面側のチッピングが、貫通電極が存在するアクティブエリアにまで侵入することを防止する。

【解決手段】メモリチップ1Aは、スクライブセンターSC側から、スクライブエリアSA、ガードリングエリアGA、及びアクティブエリアAAという領域に区分けされる。スクライブエリアSAの層間絶縁膜内には、メモリチップ1Aの表面側のチッピングを防止するための第1、第2クラックストップ3a,3bが設けられている。ガードリングエリアGAの表面側には、ガードリング4が設けられている。一方、ガードリングエリアGAの半導体基板10側(メモリチップ1Aの裏面側)には、裏面側のチッピングを防止するための溝5Aが設けられている。この裏面チッピング防止溝5Aによって、チッピングがサポート貫通電極2a及び信号等用貫通電極が形成されている領域に侵入することを防ぐことができる。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】十分なキャパシタ容量が得られ、リーク電流や寄生容量を抑制した薄膜トランジスタ装置およびその製造方法を提供する。

【解決手段】薄膜トランジスタを備え、そのゲート電極111、ソース電極131、ドレイン電極132、バス配線、画素電極133、ゲート絶縁膜121、層間絶縁膜122、半導体層141の全部もしくは一部が塗布法もしくは印刷法で形成されてなり、ゲート絶縁膜121および/もしくは層間絶縁膜122が連続膜から構成され、連続膜が薄膜部と厚膜部から構成されてなる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ダイシング面からチップ領域への水分の浸入を抑制しつつ、スクライブ領域とチップ領域とを配線により接続する。

【解決手段】半導体装置は、チップ領域16と、スクライブ領域15と、2重に配置された第1シールリング18及び第2シールリング17と、チップ領域16からスクライブ領域15まで延伸する配線60と、を有する。半導体装置は、2重に配置された第1シールリング18及び第2シールリング17のうちの一方のシールリングが配線60を通すためにシールしていない層を、他方のシールリングでシールする構造となっている。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】一つの実施形態によれば、半導体装置は、電極、メッキ膜、半田、及びコネクタが設けられる。電極は、半導体チップ表面に設けられた第一の電極部と、第一の電極部上に設けられた絶縁膜の開口部を覆うように設けられ、第一の電極部に接続された突起状の第二の電極部とから構成される。メッキ膜は、第二の電極部上に設けられる。半田は、絶縁膜及びメッキ膜上に設けられる。コネクタは、一端の第一の構成部が半田上に設けられ、他端の第二の構造部が端子に接続され、電極と電極端子の間を接続する。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】微細配線においてボイドの発生を確実に防ぐ。

【解決手段】層間絶縁膜102、103に形成された開口部12の底面及び側壁、並びに、開口部12以外の層間絶縁膜103上にあるフィールド部に、第一の金属を含むシード膜を形成し、シード膜上にレジストを形成して、開口部12をレジストで埋め込んだ後、開口部12の底面上に形成されたシード膜にレジストを残しつつレジストの一部を除去して、開口部12の側壁202A、Bの上部からフィールド部203にわたって形成されたシード膜を露出させ、開口部12の側壁の上部、及び、フィールド部203に位置するシード膜上に、第一の金属よりも抵抗率が高い第二の金属を含むカバー膜を形成した後、レジストを除去してシード膜を露出させ、露出させたシード膜に、第一の金属を含むめっき膜を形成するものである。

(もっと読む)

表示装置及びマスク

【課題】マスクの枚数を増やすことなく、ストレージキャパシタの電極間から半導体パターンを除去して高画質化を実現させる表示装置及びその製造方法を提供する。

【解決手段】本発明によるTFTパネルの製造では、半導体パターンとTFTのドレイン電極とを、同じマスクを利用したエッチングで同時にパターニングする。一方、画素電極の直下に形成される絶縁膜のパターニングには別のマスクを利用する。ドレイン電極を覆う絶縁膜の領域では、中央部の全体を感光させ、周辺部を半分の厚みまで感光させる。ストレージ電極の上方を覆う絶縁膜の領域は薄い一部を残して感光させる。ドレイン電極を覆う誘電膜をエッチングしてドレイン電極を露出させるとき、絶縁膜のその薄い一部がその下地の誘電膜を保護する。その後、絶縁膜のその薄い一部を画素電極の一部に置換し、保護された誘電膜を隔ててストレージ電極と対向させる。

(もっと読む)

101 - 120 / 1,607

[ Back to top ]