Fターム[5F033JJ01]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | コンタクト層なし、上層配線と一体形成 (1,607)

Fターム[5F033JJ01]に分類される特許

81 - 100 / 1,607

電気光学装置の製造方法

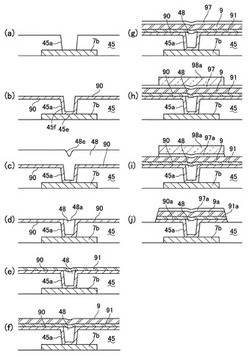

【課題】層間絶縁膜のコンタクトホールの内部にコンタクト用導電膜および埋め込み膜を設けた場合でも、コンタクトホールの外部で画素電極とコンタクト用導電膜とを確実に導通させることができる電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置100を製造するにあたって、層間絶縁膜45上にコンタクトホール45aの底部45eおよび内壁45fに重なるコンタクト用導電膜90をITO膜により形成した後、コンタクトホール45aの内部を埋める埋め込み膜48をシリコン酸化膜により形成し、その後、埋め込み膜48に対して反応性イオンエッチングを行い、コンタクト用導電膜90を露出させる。また、コンタクトホール45aの内部には埋め込み膜48を残す。その際、埋め込み膜48とコンタクト用導電膜90とのエッチング選択比を利用して埋め込み膜48を選択的に除去してコンタクト用導電膜90を露出させる。

(もっと読む)

半導体素子の製造方法

【課題】 製造コストの低減が可能な半導体素子の製造方法を提供する。

【解決手段】 第1再配線層400は、金属バンプ層320の一部分を露出するように形成される。第1再配線層400は、第1拡張パッド部410、第1延長部420及び第1連結部430を備える。第1拡張パッド部410は、金属パッド120と電気的に接続し、外部装置と接続する。第1延長部420は、金属バンプ層320上から第1拡張パッド部410上に延びるように形成される。第1連結部430は、スクライブレーン領域SRに形成され、複数の第1再配線層400を電気的に連結する。第1再配線層400は、銀、ニッケルまたは銅を含むペーストまたはインクを利用したプリンティング方法、または、ロールオフセットプリンティング方法によって形成される。これにより、金属パッドと再配線層との接触抵抗を小さくするとともに、製造コストを低減することができる。

(もっと読む)

半導体装置の製造方法

【課題】CMP法により、金属膜を研磨して、層間絶縁膜に設けられた開口部内に導体パターンを形成する際、リセス、ディッシング、及びエロージョンを抑制可能な半導体装置の製造方法を提供する。

【解決手段】CMP法により、層間絶縁膜14の上面よりも上方に形成された金属膜19及びバリア膜18を除去することで、開口部内に、バリア膜18及び金属膜19よりなる導体パターンを形成する研磨工程と、を有し、該研磨工程では、層間絶縁膜14の上面が露出する前に、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件を用いて研磨を行なうことで、導体パターンを形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 薄板化の際に層間絶縁膜が破損することを抑制できる半導体装置を得る。

【解決手段】 第1の硬度を有する材料で構成された基板10と、基板10の第1主面10aに設けられたドリフト層11と、ドリフト層11上に絶縁膜60を介して形成されたゲート電極70と、ゲート電極70を覆うように形成され、第1の硬度よりも小さい第2の硬度を有する材料で構成された層間絶縁膜80とを備え、基板10とドリフト層11とを合わせた厚みは200μm以下であり、層間絶縁膜80に、平面視において、全ての内角が90°より大きい多角形、円形または楕円形の開口90が設けられている半導体装置。

(もっと読む)

半導体装置およびその製造方法、表示装置ならびに電子機器

【課題】信頼性を向上させることが可能な半導体装置等を提供する。

【解決手段】半導体装置は、下層側の第1導電体部および上層側の第2導電体部と、第1の導電体部と第2の導電体部との間に設けられた、厚膜状の絶縁体層と、この絶縁体層に対する貫通孔の内面形状に倣うように形成され、第1導電体部と第2導電体部とを電気的に接続するコンタクト部とを備え、貫通孔のテーパ角が鋭角となっている。

(もっと読む)

半導体基板の製造方法

【課題】サイドエッチ発生の可能性を軽減させた半導体基板の製造方法を提供する。

【解決手段】絶縁膜の形成後、シード膜の形成の前に配線パターンの形成を行う。次いで、シード膜の形成後、配線パターン用レジストの剥離を行う。次いで、メッキマスクレジストの形成を行なったのち、半導体基板の表面からのメッキ電流により、ウエットエッチング工法を行うこと無く、配線パターンの形成を行う。

(もっと読む)

配線基板、赤外線センサー及び貫通電極形成方法

【課題】基板と貫通電極との間で形成される浮遊容量が小さい基板を提供する。

【解決手段】第1面2aと第1面2aと対向する第2面2bとを貫通して開口するビアホール2cを有する基板2と、基板2の第1面2aに設置され熱酸化膜を含む第1絶縁膜3と、ビアホール2c内の面とに設置され熱酸化膜を含む第3絶縁膜5と、ビアホール2c内で第3絶縁膜5に囲まれた導電体7と、を有し、第1面2aにおける第1絶縁膜3の厚みに比べてビアホール2c内の面における第3絶縁膜5の厚みが厚くなっている。

(もっと読む)

半導体装置、及び、半導体装置の製造方法

【課題】 プローバーテストの製品への影響をさらに軽減して、より一層信頼性の高い半導体装置を提供する。

【解決手段】 半導体装置100を、半導体基板10aと、半導体基板10aの一方の面上に形成された絶縁膜10bと、縦孔配線部30と、金属膜11と、導電性保護膜12とを備える構成とする。金属膜11は、絶縁膜10b内に形成され、縦孔配線部30と電気的に接続される。そして、導電性保護膜12は、絶縁膜10b内において金属膜11に接して形成され、かつ、金属膜11の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成される。

(もっと読む)

ボンディングパッドを有する半導体デバイス及びその製造方法

【課題】 ボンディングパッドを有する半導体デバイス及びその製造方法を提供する。

【解決手段】 表面側及び裏面側を有するデバイス基板、前記デバイス基板の前記表面側に配置され、n層数の金属層を有する相互接続構造、及び前記相互接続構造を通過して延伸し、前記n層数の金属層の前記第n番目の金属層に直接接触するボンディングパッドを含む半導体デバイス。半導体デバイスは、前記デバイス基板の前記裏面側に配置された遮蔽構造、及び、前記デバイス基板の前記表面側に配置され、前記デバイス基板の前記裏面側から前記放射線検出領域に向けて投射された放射線を検出することができる放射線検出領域をさらに備える。

(もっと読む)

半導体装置の製造方法

【課題】基板のエッジ部分での膜剥がれを防止し、半導体装置を効率良く製造する。

【解決手段】基板1の上方に低誘電体膜31を形成する際に、基板1のエッジ部分1Aをエッジカット工程にて洗い流すことで段差部31Aが形成される。低誘電体膜31に配線溝41を形成した後、導電膜43を埋め込む。基板1のエッジ部分1Aの導電膜43を洗い流すと、導電膜43が埋め込まれていない配線溝41Aが形成される。配線溝41Aを保護フィルム51で覆ってから、CMP法にて余分な導電膜43を除去する。この後、保護フィルム51を基板1から取り外す。

(もっと読む)

半導体装置の製造方法

【課題】有機膜中における気泡の残存を抑制する。

【解決手段】半導体装置の製造方法は、開口(コンタクトホール36)を有する層間絶縁膜37を形成する工程と、層間絶縁膜37上及び開口内に導体膜39を形成する工程と、導体膜39上に第1感光性有機膜1を塗布形成する工程を有する。この製造方法は更に、第1感光性有機膜1において開口外の部位を露光する工程と、第1感光性有機膜1において開口外の部位を現像により除去する工程と、第1感光性有機膜1において開口内の部位を紫外線により硬化させることによって第1有機膜11を形成する工程を有する。この製造方法は更に、第1有機膜11を覆うように導体膜39上に第2感光性有機膜2を塗布形成する工程と、第2感光性有機膜2を紫外線により硬化させて第2有機膜12を少なくとも第1有機膜11上に形成する工程を有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】電極パッドの表面の突出部に起因する不具合が発生し難い半導体装置の製造方法及び半導体装置を提供する。

【解決手段】半導体装置の製造方法は、表面の突出部に突出部、例えば、プロービング痕21が存在する電極パッド2を備える基板1上に、電極パッド2の少なくとも一部を覆う第1の絶縁膜4を形成する第1の絶縁膜形成工程と、第1の絶縁膜4の表面から突起した部分22を除去することができる処理を行う除去処理工程と、除去処理工程後に、第1の絶縁膜4上及び電極パッド2上に第2の絶縁膜5を形成する第2の絶縁膜形成工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】 低k膜と金属マスクとの間の界面に歪みを引き起こすことなく、高い精度の望ましいパターンを得ること。

【解決手段】 半導体装置を製造する方法では、金属マスクと絶縁マスクをと備える多層ハードマスクを用いて形成される配線層を含む半導体装置が形成される。第1パターンにアラインされた第2開口パターンを形成するために、第1ステップで多層ハードマスクが使用された後、金属マスクが除去され、絶縁マスクが、第2のステップで絶縁層中に第1のパターン構造を形成するために使用される。

(もっと読む)

半導体装置およびその製造方法、並びに表示装置

【課題】3層以上の配線を接続する際に、最も効率的にかつ最小面積で接続を行えるコンタクト構造を実現可能な半導体装置およびその製造方法、並びに表示装置を提供する。

【解決手段】基板201上に3層以上のn層の導電層202〜204が積層して形成され、n層の導電層がコンタクトパターンを介して接続され、コンタクトパターンが形成される一つの主コンタクト領域には、(n−1)個の導電層202,203を接続する(n−1)個の接続領域211,212を有し、(n−1)個の導電層のうち基板201に対する積層方向(基板201の主面に対する法線方向)において第1層より上層の導電層は、その終端部がコンタクトパターンCPTNの縁の一部に臨むように形成され、(n−1)個の導電層は、第n層の導電層により電気的に接続されている。第n層の導電層は、コンタクトパターンCPTNであるコンタクト孔を埋めつくよう形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の一表面上に絶縁膜を介して形成された導電層と、半導体基板の他面上に形成されたバンプ部と、導電層とバンプ部とを接続する半導体基板を貫通する貫通電極部とを有する半導体装置を提供する。

【解決手段】半導体基板の他面側から導電層に接続する貫通孔を形成し、貫通孔及び他面上にメタル膜(バリアメタル及びシードメタル)6を形成し、その上にフォトレジスト10を形成し、貫通孔より大きなパターンに加工してメッキマスク層を形成し、電解メッキ法により銅からなる第1メッキ膜7を形成して、貫通電極部と第1バンプ部を形成し、第1バンプ部上に第2バンプ部となる第2メッキ膜8を形成する。

(もっと読む)

電子部品、電子部品の製造方法、基板

【課題】チッピング検出用配線が他の部材で覆われている状態であっても、ダイシングによって電子部品を形成した後に、チッピング検出用配線の導通状態を検出するための電圧を印加できる基板を提供する。

【解決手段】電子部品40は、互いに平行を成す一方の主面41aと他方の主面41bが矩形状の基体41を有する。基体41の一方の主面41aには、第一チッピング検出用配線42が配されている。また、基体41の他方の主面41bには、第二チッピング検出用配線44が配されている。第一チッピング検出用配線42は貫通配線43aを介して第二チッピング検出用配線44に電気的に接続される。

(もっと読む)

半導体装置、半導体装置の製造方法、固体撮像装置及び電子機器

【課題】 ビア形成時のエッチングによる基板や配線への影響を抑制しつつ積層された半導体ウェハの回路どうしを接続する。

【解決手段】 半導体装置の製造方法は、第1基板と第1基板の一面と接するように形成された第1絶縁層を有する第1の半導体ウェハと、第2基板と第2基板の一面と接するように形成された第2絶縁層を有する第2の半導体ウェハを接合する工程と、第1基板の他面に第3絶縁層を形成する工程と、第3絶縁層、第1基板、及び第1絶縁層を貫通し第2絶縁層に形成された第2の配線上に第2絶縁層が残るようにエッチングを行い第1接続孔を形成する工程と、第1接続孔に絶縁膜を形成する工程と、第2の配線上の第2絶縁層及び絶縁膜のエッチングを行い第2接続孔を形成し第2の配線を露出させる工程と、第1及び第2接続孔の内部に形成され第2の配線と接続する第1のビアを形成する工程とを備え、第1基板の他面に形成された第1接続孔の径は第3絶縁層に形成された前記第1接続孔の径より大きい。

(もっと読む)

配線膜、薄膜トランジスタ、ターゲット、配線膜の形成方法

【課題】信頼性の高い薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ20のゲート電極15、ソース、ドレイン電極33、34のうち、いずれか一つ以上の電極はバリア膜25を有し、バリア膜25が成膜対象物21又は半導体層30に密着している。NiとMoを100原子%としたときに、バリア膜25は、Moを7原子%以上70原子%以下含有し、ガラスからなる成膜対象物21や半導体層30に対する密着性が高い。また、バリア膜25表面にCuを主成分とする金属低抵抗層26が形成された場合に、Cuが半導体層30に拡散しない。

(もっと読む)

半導体装置

【課題】とりわけ表面マークの下部に配線タングステンパッドがある場合でも、表面マークのコントラスト低下を抑制する。

【解決手段】メモリチップ31は、配線タングステン階層WTL、第1、第2、第3アルミニウム配線階層1AlL,2AlL,3AlLを備える多層配線構造を備える。各配線層の間には、第1、第2、第3層間絶縁膜315,316,317がそれぞれ形成され、第3アルミニウム配線階層3AlLとポリイミド膜PIとの間には、第4層間絶縁膜318が形成されている。第1のダミーパターンDP1は、第1アルミニウム配線階層1AlLに形成され、第2層間絶縁膜316に覆われている。第2のダミーパターンDP2は、第2アルミニウム配線階層2AlLに形成され、第3層間絶縁膜317に覆われている。第2ダミーパターンDP2は、第1ダミーパターンDP1よりも幅が長い。

(もっと読む)

半導体素子

【課題】熱(工程)に耐性のある配線構造を採用し、配線上の析出物の発生を抑制できる半導体素子を実現する。

【解決手段】半導体素子本体に接続する金材を含む配線パターンと、この配線パターンに一端側が接続され金材を含む接続端子と、前記半導体素子本体と前記配線パターンと前記接続端子とを覆う絶縁体と、を具備する半導体素子において、前記配線パターンあるいは接続端子の一方の面に一面が接し他面が前記絶縁体に接する面状のシリサイド体を具備したことを特徴とする半導体素子である。

(もっと読む)

81 - 100 / 1,607

[ Back to top ]