Fターム[5F033JJ12]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Cu (3,263) | Cu合金 (406)

Fターム[5F033JJ12]に分類される特許

101 - 120 / 406

半導体装置

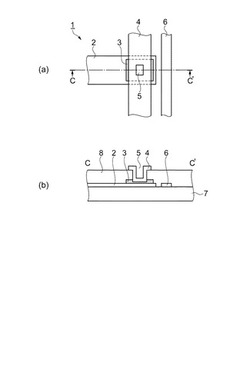

【課題】コンタクトホールの加工時において配線のダメージを受けにくく、信頼性の低下を抑制できる構造の接続部を有する半導体装置を提供すること。

【解決手段】接続部1は、第1導電層2と第2導電層4とが、その交差個所に設けられたコンタクトホール5を介して接続されたものである。矩形状のコンタクトホール5は第2導電層4の幅方向の略中央に配置されている。そして、コンタクトホール5のパターンを囲むように矩形状の半導体層3が設けられている。半導体層3は、コンタクトホール5の底部において第1導電層2上に形成されている。この半導体層3は、第1導電層2とのエッチング選択比が高く、第1導電層2に対するエッチング効率が充分に高いものである。

(もっと読む)

マスクを使用せずに導電性ビアに対して裏面位置合わせを行うことによる半導体構成部品の製造方法

半導体構成部品(90)を製造する方法が、回路面(54)と、裏面(56)と、導電性ビア(58)とを有する半導体基板(52)を提供するステップと、導電性ビア(58)の端子部分(76)を露出するために、基板(52)の一部分を裏面(56)から除去するステップと、端子部分(76)を封入するポリマー層(78)を裏面(56)に堆積するステップと、次いで、ポリマー層(78)および端子部分(76)の端部を平坦化して、ポリマー層(78)に埋め込まれた自己整合導体を形成するステップとを含む。導電性ビア(58)に電気的に接触させて、端子接点(86)や裏面再分配導体(88)等の追加の裏面要素を形成することもできる。半導体構成部品(90)は、半導体基板(52)と、導電性ビア(58)と、およびポリマー層(78)に埋め込まれた裏面導体とを有する。積重ね半導体構成部品(96)が、電気的に互いに通じる位置の整合した導電性ビア(58)を有する複数の構成部品(90-1、90-2、90-3)を有する。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】印加電界の履歴によって抵抗値が変化する抵抗変化層を有するスイッチ素子を多層配線中に形成し、かつ配線又は抵抗変化層の表面がダメージを受けることを抑制できるようにする。

【解決手段】この半導体装置は、第1配線層12、第2配線層16、及びスイッチビア35を備える。第1配線層12は第1配線32を有しており、第2配線層16は第2配線39を有している。スイッチビア35は、第1配線32と第2配線39を接続する。またスイッチビア35は、少なくとも底部に、抵抗変化層33を有しているスイッチ素子を有している。抵抗変化層33は、電界印加履歴に応じて抵抗値が変化する。

(もっと読む)

半導体装置の製造方法

【課題】銅層形成の下地となるシード層のオーバーハングが抑制された半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の上方に、絶縁膜を形成する工程と、絶縁膜に凹部を形成する工程と、凹部の内面に、バリアメタル層を形成する工程と、バリアメタル層上に、RuとCuを含むシード層を形成する工程と、シード層上に銅層を形成する工程とを有する。

(もっと読む)

半導体装置とその製造方法

【課題】ダマシン配線構造を有する半導体装置に形成される配線表面の酸化物部を選択的に除去する。

【解決手段】ダマシン配線構造を有する半導体装置を製造するに際し、配線表面を、Xeのプラズマで逆スパッタリングする。本発明によれば、Xeのプラズマガスで逆スパッタリングすることにより、配線表面の酸化物部等を選択的に効率よく除去でき、ダマシン配線構造において、上下配線間のコンタクト抵抗の増大を回避できる。また、配線の上に形成されたCFなどの絶縁膜へのダメージを抑制でき、絶縁膜の誘電率変動も抑制できる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【目的】、配線層とその下層のプラグ層との配線抵抗を抑えながら下層のプラグの埋め込み性を向上させることが可能な半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、Cu配線10と、Cu配線10の下層側でCu配線10と接触して接続されるCuプラグ20と、Cuプラグ20の底面側及び側面側に配置された、Cuに対してバリア性を有するBM膜240と、Cu配線10とCuプラグ20との内Cuプラグ20側に選択的に、かつCuプラグ20とBM膜240との間に介在するように配置された、BM膜240よりも前記導電性材料に対して濡れ性が高いRu膜242と、Cu配線10とCuプラグ20とが接触する箇所を少なくとも除くCu配線10の底面側と、Cu配線10の側面側とに配置された、Cuに対してバリア性を有するBM膜244と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】低抵抗の導電部を備える、信頼性の高い半導体装置を提供する。

【解決手段】ビアホール36a内及び配線溝36b内に、バリア層37を介して、CnMnを含有する第1導電層38、及びCuを主成分とする第2導電層39を形成し、清浄化後、低温酸化を行い、第1,第2導電層38,39表面にCu酸化物層40を形成する。その後、キャップ層の形成を行い、その状態で高温条件の熱処理を行うことで、第1,第2導電層38,39内のMnをCu酸化物層40に拡散させ、キャップ層との界面に、Cu酸化物層40にMnが含有された化合物層を形成する。これにより、第1,第2導電層38,39内のMnを減少させることが可能になり、さらに、キャップ層の密着性を向上させることが可能になる。

(もっと読む)

半導体装置

【課題】ノイズの影響を低減できるともに、レイアウト効率のよいMIM型容量素子を提供する。

【解決手段】半導体装置100は、下部電極112と、下部電極112上に設けられた中間電極116と、中間電極116上に設けられた上部電極124と、下部電極112と中間電極116との間に設けられた第1の絶縁膜と、中間電極116と上部電極124との間に設けられた第2の絶縁膜と、中間電極116と同層に設けられている第1の接続配線118と、下部電極112と第1の接続配線118とを電気的に接続する第1のビア114と、第1の接続配線118と上部電極124とを電気的に接続する第2のビア122とを有し、第1の接続配線118、第1のビア114、および、第2のビア122が、中間電極116の第1の辺に隣接して設けられているとともに、中間電極116の第1の辺と対向する第2の辺に隣接して設けられている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】エアギャップ部を有し、かつ、高い機械的強度を有する半導体装置およびその製造方法を提供する。

【解決手段】酸素を含有する層間絶縁膜IL1の複数の溝部の側壁を被覆するバリア金属層ALが形成される。複数の溝部を充填するように配線金属層PCが形成される。層間絶縁膜IL1の酸素を熱拡散させることによってバリア金属層ALの少なくとも一部を酸化することで、酸化物バリア層BL1が形成される。配線金属層のうち複数の溝部の外側の部分を除去することによって、第1および第2の配線間領域IW1,IW2と第1〜第3の配線WR1〜WR3とが形成される。第1の配線間領域IW1を覆い、かつ第2の配線間領域IW2上に開口部OPを有するライナー膜LN1が形成される。開口部OPを介したエッチングが行なわれる。

(もっと読む)

半導体装置及びその製造方法

【課題】エレクトロマイグレーションの抑制が図られた半導体装置を提供する。

【解決手段】半導体装置は、半導体素子の形成された半導体基板と、半導体基板の上方に、水分を含み、凹部が形成された層間絶縁膜と、凹部の内面上に形成され、非晶質及び多結晶の一方の結晶性を有する第1のバリアメタル層と、第1のバリアメタル層上に形成され、非晶質及び多結晶の他方の結晶性を有する第2のバリアメタル層と、第2のバリアメタル層上に形成された銅配線と、銅配線を覆って前記層間絶縁膜上に形成された銅拡散防止絶縁膜と、銅配線と銅拡散防止絶縁膜との界面に形成された金属酸化物層とを有する。

(もっと読む)

集積回路デバイスのヒューズ構造

【課題】 集積回路デバイスのヒューズ構造を提供する。

【解決手段】 本発明のヒューズ構造は、半導体基板の一部の上に配置された金属含有導電性材料のストリップを含み、ストリップは、第1方向に沿って延伸し、均一な線幅を有する。誘電体層は、導電層を覆う。誘電体層内は、第1ビアと第2ビアを有し、第1インターコネクトと第2インターコネクトをそれぞれ含む。第1インターコネクトは、ストリップ上の第1位置と物理的且つ電気的に接触しており、第2インターコネクトは、ストリップ上の第2位置と物理的且つ電気的に接触している。導電ストリップ上の第1と第2位置は、シリコンを含まない。誘電体層の上方は、第1インターコネクトに電気的に接続された第1配線構造と、第2インターコネクトに電気的に接続された第2配線構造である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】上層配線の幅によらずにコンタクトプラグの底面がアンカー構造となり、下層配線との接続抵抗を低減できる半導体装置とその製造方法を提供する。

【解決手段】基板に下層配線W1となる第1導電層を形成し、絶縁膜を形成し、上層配線用溝とこれに連通するようにコンタクトホールCHを形成する。次に、コンタクトホール及び上層配線用溝の内壁面を被覆してバリアメタル層を形成し、その上層にコンタクトホール及び上層配線用溝に埋め込んで第2導電層を形成する。ここで、上層配線用溝及びコンタクトホールを形成する工程において、上層配線W2と下層配線W1の交差する領域に、上層配線にスリットSL1,SL2または切り欠きを設けて幅が狭くなった部分NPが設けられるように上層配線用溝を形成し、この幅が狭くなった部分NPにおいてコンタクトホールCHを形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エアーギャップ型の多層配線構造を有する半導体装置の上部配線のたわみを少なくするとともに、前記半導体装置の製造方法を簡略化するという課題があった。

【解決手段】半導体素子102を含む層間膜層95と、層間膜層95上に備えられ、エアーギャップ部96cを有する多層配線部96と、層間膜層95の上に立設され、多層配線部96を構成する複数の配線部のうちいずれか一つの配線部を支持するものであって、前記配線部と同一の材料からなり、前記一の配線部のみと電気的に接続された柱状の支持体51と、を具備してなる半導体装置111を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置の製造方法

【課題】パターン内のボイドの発生を抑制する。

【解決手段】下層配線30に達するビアホール33を形成し、バリアメタル層34及びシード層35aを形成した後、電解めっき法により、ビアホール33内をめっき層で埋め込む。その際、シード層35a形成後に、ビアホール33の間口にオーバーハング101bが形成されることを想定し、例えば開口径70nm以下のビアホール33であれば、シード層35a形成後のビアホール33の開口径W2を20nm以上にする。これにより、そのシード層35aを用いた電解めっき時に、ビアホール33内がめっき層で埋まる前にその間口が塞がってボイドが発生するのを回避する。

(もっと読む)

配線構造及び配線構造の製造方法

【課題】シリコンへのオーミック接合が得られると共に、シリコン中への元素の拡散を抑制できる配線構造及び配線構造の製造方法を提供する。

【解決手段】本発明に係る配線構造1aは、シリコン層10と、シリコン層10上に設けられ、マンガン(Mn)が添加された銅合金からなる下地層20と、下地層20上に設けられる銅層30とを備え、シリコン層10と下地層20との界面を含む領域でMnが濃化することにより、電気導電性を有する拡散バリア層25が形成される。

(もっと読む)

配線構造及び配線構造の製造方法

【課題】シリコンへのオーミック接合が得られると共に、シリコン中への元素の拡散を抑制できる配線構造及び配線構造の製造方法を提供する。

【解決手段】本発明に係る配線構造1aは、シリコン層10と、シリコン層10上に設けられ、ニッケル(Ni)が添加された銅合金からなる下地層20と、下地層20上に設けられる銅層30とを備え、シリコン層10と下地層20との界面を含む領域でNiが濃化することにより、電気導電性を有する拡散バリア層25が形成される。

(もっと読む)

半導体装置

【課題】製造バラツキに関わらず、切断箇所を制御できる構成の電気ヒューズを得る。

【解決手段】半導体装置200は、基板(不図示)上に形成された上層ヒューズ配線112、下層ヒューズ配線122、および上層ヒューズ配線112の一端と接続され、上層ヒューズ配線112と下層ヒューズ配線122とを接続するビア130から構成される電気ヒューズ100を含む。上層ヒューズ配線112には、一端側で配線幅が狭くなった幅変動領域118が設けられている。

(もっと読む)

半導体装置

【課題】金属パッドの下方に位置する層間絶縁膜にクラックが発生し、クラック内に水分が進入することがあっても、金属パッドの近傍の配線の信頼性が低下することを防止する。

【解決手段】半導体基板10上に形成された層間絶縁膜18と、層間絶縁膜18を貫通して設けられたリング用金属配線20Aと、層間絶縁膜18を貫通して設けられたコンタクト用金属配線20Bと、層間絶縁膜18上及びリング用金属配線20Aの全上面上に形成された第1の保護絶縁膜21と、第1の保護絶縁膜21上に形成された金属パッド23とを備え、リング用金属配線20Aは、層間絶縁膜18のうち金属パッド23の下方に位置する領域にリング状に設けられており、金属パッド23は、第1の保護絶縁膜21に形成された第1の開口部21aを通じてコンタクト用金属配線20Bに接続されている。

(もっと読む)

半導体装置の製造方法

【課題】銅を主成分とするコンタクトプラグを有する半導体装置において、コンタクトプラグに隆起が発生することを防止する。

【解決手段】第1の層間絶縁膜102に、金属シリサイド層101に到達するコンタクトホール103を形成する工程(c)と、コンタクトホールの底面及び側壁に、高融点金属膜104を形成する工程(d)と、高融点金属膜上に、銅を主成分とする金属膜106Aを形成し、コンタクトホール内に、高融点金属膜を介して、金属膜が埋め込まれてなるコンタクトプラグ107を形成する工程(e)と、第1の層間絶縁膜及びコンタクトプラグの上に、第2の層間絶縁膜108を形成する工程(f)とを備え、工程(f)は、コンタクトプラグの表面に存在する酸素ガスを除去する工程(f1)と、工程(f1)の後に、コンタクトプラグの表面に存在する酸素ガスが除去された状態で、第2の層間絶縁膜を形成する工程(f2)とを含む。

(もっと読む)

テーパ型形状の再配線に接続される接着パッド

【課題】テーパ型形状の再配線に接続される接着パッドを提供する。

【解決手段】集積回路構造は、前面と後面を有する半導体基板からなる。シリコン貫通ビア(TSV)は半導体基板を貫通し、TSVは、半導体基板の後面に延伸する後端を有する。再配線(RDL)は半導体基板の後面に形成されて、TSVの後端に接続される。パッシベーション層はこれに形成される開口によりRDL上に形成され、RDLの上表面と側壁部分は、開口により露出する。金属仕上げ層が開口中に形成されて、RDLの上表面と側壁部分に接触する。

(もっと読む)

101 - 120 / 406

[ Back to top ]