Fターム[5F033JJ12]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Cu (3,263) | Cu合金 (406)

Fターム[5F033JJ12]に分類される特許

81 - 100 / 406

半導体装置の製造方法

【課題】

太幅配線の添加元素を細幅配線の添加元素とは独立に制御する。

【解決手段】

層間絶縁膜に、第1の幅を有する第1の配線溝および第1の幅より広い第2の幅を有する第2の配線溝を形成し、第1の配線溝および第2の配線溝内に、第1の添加元素を含む第1のシード層を形成し、第1のシード層上に第1の銅層を形成し、第1の配線溝内の第1の銅層および第1のシード層を残存させつつ、第2の配線溝内の第1の銅層および第1のシード層を除去し、その後、第2の配線溝内に、第2の添加元素を含む又は添加元素を含まない第2のシード層を形成し、第2のシード層の上に第2の銅層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ダマシン法を使用して配線を形成する半導体装置の製造技術において、信頼性の高い配線を形成する技術を提供する。

【解決手段】ハードマスク膜HM1上にハードマスク膜HM2が形成され、このハードマスク膜HM2上に有機樹脂膜ORFが形成された状態で、レジストCMPを実施する。これにより、ハードマスク膜HM2上に形成されている有機樹脂膜ORFが除去されるとともに、ハードマスク膜HM2の膜厚が膜減りする。その後、膜減りしたハードマスク膜HM2を除去し、露出したハードマスク膜HM1をマスクにしてトレンチを加工する。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

ビアがガウジングされた相互接続構造体及びその製造方法

【課題】 ビア開口部の底部にガウジング構造部を含む相互接続構造体、及びその形成方法を提供する。

【解決手段】 本発明の方法は、ビア開口部の上に配置されるライン開口部内の堆積されたトレンチ拡散バリアの被覆率に影響を与えず、及び/又は、ビア開口部及びライン開口部を含む相互接続誘電体材料内にスパッタリングを行なうことによりビア開口部の底部にガウジング構造部を生成することに起因する損傷を生じさせない。こうした相互接続構造体は、最初に相互接続誘電体内にライン開口部を形成し、その後、ビア開口部、次いでガウジング構造部を形成することによって、ビア開口部の底部内にガウジング構造部を提供することにより達成される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線絶縁膜としてSiOCH膜を用いる場合に、ビアホールの開口径に依らず、その加工制御性を十分に得て、下層Cu配線の表面の組成のバラツキを十分に抑制する。

【解決手段】下層Cu配線3上に形成されている積層構造20は、シリコンと炭素を含有するキャップ絶縁膜4と、キャップ絶縁膜4上に形成されている配線絶縁膜5としてのSiOCH膜を有する。積層構造20にビアホール8、9を形成する工程は、第1及び第2ドライエッチングを組み合わせて行う。第1ドライエッチングでは開口径が小さいビアホール9のエッチングレートが、開口径が大きいビアホール8のエッチングレートよりも大きくなるようにO2濃度が設定された第1混合ガスを用いる。第2ドライエッチングではビアホール8のエッチングレートがビアホール9のエッチングレートよりも大きくなるようにO2濃度が設定された第2混合ガスを用いる。

(もっと読む)

半導体装置

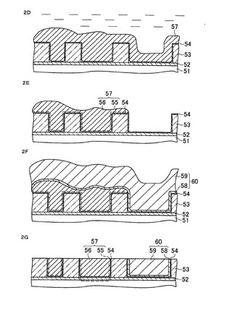

【課題】下層導電層の表面を十分保護することができ、信頼性が高く、配線容量が小さなデュアルダマシン配線を有する半導体装置の製造方法を提供する。

【解決手段】導電性領域11を有する下地と10、下地の表面を覆う絶縁性エッチストッパ膜12と、絶縁性エッチストッパ膜上に形成された層間絶縁膜と、層間絶縁膜表面から第1の深さで形成された配線用溝と、配線用溝底面から導電性領域に達する接続用孔と、配線用溝および接続用孔を埋め込んで形成されたデュアルダマシン配線である。層間絶縁膜が配線用溝の側面および底面を包む第1種の絶縁層15と、第1種の絶縁層よりも下に配置され、第1種の絶縁層とエッチング特性の異なる第2種の絶縁層56とを含む。接続用孔は、断面で見た時に第1種の絶縁層内で傾斜し、上方に向かって次第に開口が増大する部分を有する。

(もっと読む)

半導体装置の製造方法

【課題】配線構造におけるクリティカルディメンションの制御性を向上させる。

【解決手段】配線構造の製造方法が提供される。本発明の一態様によれば、絶縁層内に溝またはビアが形成される際、別のビアおよび/または溝の側壁面が金属酸化層で覆われている。金属酸化層は、側壁面の侵食を防止するおよび/または抑制することができる。その結果、方法は、ビアおよび溝のクリティカルディメンションの制御性を向上させることができる。

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106の一端は、導通部106の他端より面積重み付けした平均結晶粒径が大きい金属材料を少なくとも含む。また、導通部106は、結晶粒径が13μm以上の金属材料を含む。

(もっと読む)

多層配線の形成方法

【課題】 工程数の増加がなく、しかも銅を使用している配線にダメージが及ぶ可能性も少ない多層配線の形成方法を提供すること。

【解決手段】 銅を使用している下層配線3上にエッチングストップ層5を形成し、エッチングストップ層5上に層間絶縁膜6を形成し、層間絶縁膜6にエッチングストップ層5に達する開孔7を形成し。層間絶縁膜6上に酸化マンガン膜8を形成し、酸化マンガン膜8を開孔7から露呈した層間絶縁膜6の表面に残しながら、下層配線3上に形成されたエッチングストップ層5を除去し、開孔7の底に下層配線3を露呈させ、開孔7の底に露呈した下層配線3上に、上層配線を形成する。

(もっと読む)

半導体装置の製造方法

【目的】キャップ成膜時に起因するlow−k膜の絶縁性劣化を低減する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜上に絶縁材料を用いたキャップ膜を形成する工程(S106)と、前記キャップ膜を形成した後に、前記キャップ膜を介して前記前記キャップ膜の下層のシリル化処理を行なう工程(S108)と、前記シリル化処理の後、エッチング法を用いて、前記キャップ膜上から前記絶縁膜内へと続く開口部を形成する工程(S114)と、前記開口部に導電性材料を堆積させる工程(S124)と、を備えたことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バリアメタルの被覆性を向上させる。

【解決手段】本発明の半導体装置は、キャップ絶縁膜1d上に形成された絶縁膜と、絶縁膜に形成された配線溝と、配線溝の底面に形成されたビア孔と、少なくともビア孔の側壁を覆うバリアメタル膜と、を有する。ビア孔は、径が異なる複数の孔から構成されており、複数の孔は、下に向けて径が小さくなるように深さ方向に接続し、複数の孔の接続部にキャップ絶縁膜に対してほぼ平行な面を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の埋め込み不良及び配線抵抗の上昇を抑えると共に、信頼性を向上した半導体装置を実現できるようにする。

【解決手段】半導体装置は、基板101の上に形成された絶縁膜105と、絶縁膜105中に形成された、銅を含む材料からなる埋め込み配線115とを備えている。絶縁膜105と埋め込み配線115との間には、白金族元素を含む材料からなるバリア膜110が形成されている。絶縁膜105とバリア膜110との間には、絶縁膜105よりも密度が高い高密度絶縁膜109が形成されている。

(もっと読む)

半導体構造体及びその形成方法

【課題】 相互接続構造の信頼性及び拡張性を改善する相互接続構造のための冗長金属拡散バリア層を提供する。

【解決手段】 冗長金属拡散バリア層は、誘電体材料内に設けられた開口内に配置され、且つ開口内に存在する拡散バリア層及び導電性材料の間に配置される。冗長拡散バリア層は、Ru並びに純粋なCo若しくはN,B及びPのうちの少なくとも1つを含むCo合金からなる単層若しくは多層構造である。

(もっと読む)

気相成長装置と半導体装置の製造方法

【課題】シランとアンモニアの混合ガスソークによる銅拡散防止絶縁膜形成前の銅配線表面処理を改善できる気相成長装置、および表面状態がよく、抵抗が低い銅配線を有する半導体装置の製造方法を提供する。

【解決手段】シランを供給できるガス供給系1aと反応室を接続する、2つ以上のバルブを含む連続バルブの1つをノーマリオープンとし、ガス供給系と排気系を接続する捨てガスライン3のノーマリクローズのバルブV14と連動させることにより、反応室内の残留ガスの影響を抑制する。

(もっと読む)

配線構造、薄膜トランジスタ基板およびその製造方法、並びに表示装置

【課題】純CuまたはCu合金のCu系合金配線と半導体層との間のバリアメタル層を省略することが可能なダイレクトコンタクト技術であって、幅広いプロセスマージンの範囲においてCu系合金配線を半導体層に直接かつ確実に接続することができる技術を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、純CuまたはCu合金のCu系合金膜とを備えた配線構造であって、前記半導体層と前記Cu系合金膜との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、且つ、前記(N、C、F、O)層を構成する窒素、炭素、フッ素、および酸素のいずれかの元素は、前記半導体層のSiと結合している。

(もっと読む)

表示装置及び表示装置製造方法

【課題】表示装置の薄膜トランジスタ基板において、窒化ケイ素膜上への銅の微細配線を、より簡易に行う。

【解決手段】微細配線がされたTFT基板は、無アルカリガラスからなるガラス基板101と、インジウム錫酸化物からなる透明導電膜102と、アルミニウムを4原子%含有し銅を主成分とする合金からなる第一の導電層103及び109と、99.99%純度の純銅からなる銅配線である第二の導電層104及び110と、窒化ケイ素からなるゲート絶縁膜106と、非晶質ケイ素からなる半導体層107と、n+型非晶質ケイ素からなるコンタクト層108と、透明導電膜102と第一の導電層103との界面の金属酸化物層105と、を備える。

(もっと読む)

半導体装置

【目的】プロービング試験での導電パッド下に配置された金属配線上の絶縁膜のクラック発生を抑制することが可能な半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、導電パッドと、前記導電パッド上に配置され、前記導電パッドの一部が露出するように開口領域が形成された第1の絶縁膜と、前記導電パッドの下方に配置された第2の絶縁膜と、銅(Cu)を用いた配線を有し、前記第2の絶縁膜を介して前記導電パッドの下方に配置され、前記開口領域と重なる領域での最上層における前記配線の最大配線幅w(nm)と前記配線の被覆率R(%)とがある条件を満たすように配置された少なくとも1層の配線層と、を備えたことを特徴とする。

(もっと読む)

半導体装置とその製造方法、電気光学装置とその製造方法、回路基板とその製造方法、及び電子機器

【課題】フォトリソグラフィー法及びエッチング法を用いることなく導電層間を接続することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、基板上に第1導電層と層間絶縁膜と第2導電層とを順に積層形成する導電層工程と、前記第2導電層の表面から物理的加工を施すことで、前記第2導電層と前記層間絶縁膜とを貫通して前記第1導電層に達する凹部を形成するコンタクトホール形成工程と、を有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

半導体装置の製造方法及び半導体基板

【課題】表面に段差部分を有する構造物を覆う上部絶縁膜を基板全面に亘って均一に表面平坦化し、上部絶縁膜の表面平坦化及び膜厚均一化を共に実現して、所期の半導体素子を安定且つ確実に形成する。

【解決手段】半導体基板1上に、多層配線構造の下層部分2を適宜形成した後、半導体基板1のベベル部1aを覆うように、下層部分2と略同等の膜厚に縁部絶縁膜14を形成し、上部絶縁膜11aをCMPで表面研磨して平坦化する。

(もっと読む)

81 - 100 / 406

[ Back to top ]