Fターム[5F033JJ12]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Cu (3,263) | Cu合金 (406)

Fターム[5F033JJ12]に分類される特許

121 - 140 / 406

半導体装置

【課題】金属パッドの下方に位置する層間絶縁膜にクラックが発生し、クラック内に水分が進入することがあっても、金属パッドの近傍の配線の信頼性が低下することを防止する。

【解決手段】半導体基板10上に形成された層間絶縁膜18と、層間絶縁膜18を貫通して設けられたリング用金属配線20Aと、層間絶縁膜18を貫通して設けられたコンタクト用金属配線20Bと、層間絶縁膜18上及びリング用金属配線20Aの全上面上に形成された第1の保護絶縁膜21と、第1の保護絶縁膜21上に形成された金属パッド23とを備え、リング用金属配線20Aは、層間絶縁膜18のうち金属パッド23の下方に位置する領域にリング状に設けられており、金属パッド23は、第1の保護絶縁膜21に形成された第1の開口部21aを通じてコンタクト用金属配線20Bに接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通ビアと電極パッドとの接合強度を増大させることにより、3次元配線構造を有する半導体装置の機械的強度を増大させる。

【解決手段】第1の半導体チップ100と第2の半導体チップ200とが貼り合わされている。第1の半導体チップ100の表面部に電極パッド104が形成されている。第2の半導体チップ200中に貫通ビア114が形成されている。電極パッド104には掘り込み部111が形成されており、当該掘り込み部111内に貫通ビア114の底部が埋め込まれている。

(もっと読む)

ダメージフリー被覆刻設堆積法

【課題】周辺表面を汚染もしくは乱さずに、スパッタリングした銅シード層を堆積させて、所望の形状に刻設する方法を提供する。

【解決手段】底部516と、側壁514と、上側開口526とを有する複数の凹状のデバイス特徴を含む基板上に銅シード層を堆積させる方法であって、a)基板表面からのスパッタリングを引き起こす態様において前記凹状のデバイス特徴の基板表面に衝突することなく前記銅シード層の第1の部分を前記基板上にスパッタ堆積するステップと、b)前記銅シード層の第2の部分を前記基板上にスパッタ堆積すると同時に、銅シード層の前記第1の部分の少なくとも一部を、前記複数の凹状のデバイス特徴のそれぞれの底部から対応する側壁へと再配分するステップと、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を介してのチップ間の電気的接続を確実に行えるようにする。

【解決手段】シリコン基板11中に裏面に達するように貫通電極16が形成されている。シリコン基板11の裏面側にシリコン基板21が貼り合わされていると共に、貫通電極16の露出先端部とシリコン基板21上の電極端子25とが電気的に接続されている。貫通電極16における露出先端部の側壁の傾斜角は、その他の部分の側壁の傾斜角と比べて大きい。

(もっと読む)

半導体装置の製造方法

【課題】Cu配線中のMnの残留量を減らすことができる、半導体装置の製造方法を提供する。

【解決手段】第2バリア膜13の形成後に、SiH4を含むガスを用いたPECVD法により、Cu層20上にSiおよびOを含む絶縁材料からなる犠牲層21が積層される。犠牲層21にSiおよびOが含まれるので、犠牲層21の積層過程で、Cu層20と犠牲層21との界面にMnSiOからなる反応生成膜22が生じる。この反応生成膜22の生成にMnが使用されることにより、Cu層20に含まれるMnの量が減少する。よって、Cu層20からなる第2Cu配線中のMnの残留量を減らすことができる。

(もっと読む)

半導体デバイスのメタライゼーションシステムにおけるキャップ層のCMP及びエッチング停止層としての使用

【解決手段】

進歩的なメタライゼーションシステムを製造する間、敏感な誘電体材質上に形成される誘電体キャップ層が、過剰な金属を除去するためのCMPプロセスの間に部分的に維持されてよく、それにより、CMPプロセスの間に誘電体キャップ材質を実質的に完全に消耗する場合に従来の手法で必要であろうような専用のエッチング停止層を堆積させる必要性が回避され得る。従って、低減されたプロセスの複雑性及び/又は高い柔軟性が低k誘電体材質の高い完全性との組み合わせにおいて達成され得る。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、配線上面部からの金属拡散を抑制することができる、半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明では、半導体基板上の第一層間膜1内に形成された溝2内に、銅と第一金属元素とを含有する銅シード膜4を形成する。その後、銅メッキ処理を施す。その後、銅層の酸化が行われない第一雰囲気中にて第一熱処理を行う。そして、余分な銅合金金属層を除去し、溝2内に銅合金配線6を形成する。その後、酸素を含有する第二雰囲気中にて第二熱処理を行うことにより、銅合金配線6表面に、第一金属元素の酸化物である酸化物層7を形成する。

(もっと読む)

半導体装置

【課題】切断された電気ヒューズの切断状態を良好に保つ。

【解決手段】半導体装置200は、基板上に形成された下層配線120と、下層配線120上に下層配線120に接続して設けられたビア130と、ビア130上にビア130に接続して設けられた上層配線110とを含む電気ヒューズ100であって、切断状態において、電気ヒューズ100を構成する導電体が外方に流出してなる流出部が形成されることにより切断される電気ヒューズ100と、上層配線110および下層配線120の一方と同層に上層配線110および下層配線120の一方の側方に形成されるとともに、上層配線110および下層配線120と電気的に接続された熱拡散用上層配線152aを含む熱拡散部150aとを含む。

(もっと読む)

半導体装置の製造方法

【課題】溝の側面上における金属膜の膜剥がれの発生を防止することができながら、Cu配線中のMnの残留量を低減させることができる、半導体装置の製造方法を提供する。

【解決手段】第1配線5上に、SiおよびOを含む第2絶縁層6が形成された後、第2絶縁層6に、第2溝11およびビアホール12が形成される。次に、スパッタ法により、溝の内面およびビアホールの内面に、MnOからなる金属膜18が被着される。このとき、第2溝11の内面およびビアホール12の側面には、スパッタリングのエネルギーによって、金属膜18中のMnOが入り込み、MnSiOからなる第2バリア膜13が形成される。そして、金属膜18におけるビアホール12の底面に形成された部分が除去された後、ビアホール12にビア15が埋設されるとともに、第2溝11に第2配線14が埋設される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線を高信頼性化する。

【解決手段】半導体装置70には、キャップ膜3上の層間絶縁膜4に第1の開口部が設けられ、第1の開口部には、バリアメタル膜5とCu(銅)からなる配線層6が埋設される。層間絶縁膜4及び配線膜6上のキャップ膜7及び層間絶縁膜8に第3の開口部が設けられ、層間絶縁膜8上の層間絶縁膜9に第3の開口部に接するように第2の開口部が設けられる。第2及び第3の開口部はT字型開口部を形成する。T字型開口部には、バリアメタル膜10とCu(銅)からなる配線層11が埋設される。配線層6は、Cu(銅)よりも応力が高い高応力膜26と熱処理により膜中の原子空孔(Vacancy)が排出される。配線層11は、Cu(銅)よりも応力が高い高応力膜36と熱処理により膜中の原子空孔(Vacancy)が排出される。

(もっと読む)

薄膜トランジスター

【課題】薄膜トランジスター中間体および薄膜トランジスターを提供する。

【解決手段】n−アモルファスSi半導体膜4の上に形成されたn+アモルファスSiオーミック膜4´と、n+アモルファスSiオーミック膜4´の上に形成されたバリア膜11と、バリア膜11の上に形成されたドレイン電極膜5およびソース電極膜6を有する薄膜トランジスター中間体であって、ドレイン電極膜およびソース電極膜は、バリア膜11に接して形成されているSr:0.2〜2モル%、酸素:1〜20モル%を含有し、残部がCuからなる酸素−ストロンチウム含有銅合金下地層12と、酸素−ストロンチウム含有銅合金下地層12の上に形成されたCu層13とからなる複合銅合金膜14が形成されている薄膜トランジスター中間体、並びにこの薄膜トランジスター中間体をプラズマ水素処理して得られた薄膜トランジスター。

(もっと読む)

電子デバイス及びその製造方法

【課題】層間絶縁膜に形成した空隙部を導電材料で充填して配線・接続部を形成する際に問題となる、下層の導電領域と配線・接続部との接続状態に起因する不都合を生ぜしめることなく、微細な配線及び接続部が所望の状態に正確且つ容易に実現されてなる信頼性の高い電子デバイスを実現する。

【解決手段】ダミー構造物16を形成し、ダミー構造物16の側面のみに側壁膜17を形成する。このダミー構造物16を覆うように層間絶縁膜18を形成する。そして、側壁膜17が残るようにダミー構造物16のみを除去し、下層配線14の表面の一部を露出させ、層間絶縁膜18に形成された開口18aをCuで埋め込み、Cuの表層を層間絶縁膜18の表面に合わせて平坦化する。以上により、下層配線14と直接的に接続されるCu接続部22を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 選択性トップバリアを用いた配線におけるリークを抑制することができ、配線の信頼性の向上をはかる。

【解決手段】 埋め込み配線を有する半導体装置の製造方法であって、配線間絶縁膜102上に該絶縁膜102とは材料の異なる犠牲膜103を形成した後、犠牲膜103及び配線間絶縁膜102を選択的にエッチングして配線用溝105を形成し、次いで配線用溝105内にCuを主成分とする導電膜107を埋め込み形成し、次いで導電膜107の上面に選択的にトップバリア層108を形成し、次いで犠牲膜103を除去することによりメタル残渣108aを除去する。

(もっと読む)

導電材料構造体の形成方法

【課題】実用化の障害となるめっきの長時間化を改善し、貫通電極による三次元実装を実現するのに好適な導電材料構造体をより短時間で形成できるようにする。

【解決手段】貫通電極用凹部12を形成した基板Wの表面の該凹部12表面を含む全表面に導電膜14を形成し、基板W表面の所定位置にレジストパターン30を形成し、導電膜14を給電層とした第1めっき条件で第1電解めっきを行って貫通電極用凹部12内に第1めっき膜36を埋込み、貫通電極用凹12部内への第1めっき膜36の埋込みが終了した後に、導電膜14及び第1めっき膜36を給電層とした第2めっき条件で第2電解めっきを行って、レジストパターン30のレジスト開口部32に露出した導電膜14及び第1めっき膜36上に第2めっき膜38を成長させる。

(もっと読む)

絶縁性被膜を有する構造体及びその製造方法、樹脂組成物並びに電子部品

【課題】電気絶縁性に優れる均一な絶縁性被膜を有する構造体及びその製造方法、絶縁性被膜を形成することができる樹脂組成物並びに電子部品を提供する。

【解決手段】本発明の絶縁性被膜を有する構造体の製造方法は、孔部を有する基板に、溶剤を塗布する工程と、樹脂組成物を、この樹脂組成物が孔部内の溶剤と接触するように、基板に塗布する工程と、塗膜を乾燥し、孔部の内壁面及び底面のうちの少なくとも内壁面に樹脂成分を含む被膜117、118、119を形成する工程と、孔部の内壁面及び底面を含む基板の全表面に形成されている被膜を加熱し、樹脂成分の硬化物を含む絶縁性被膜217、218、219とする加熱硬化工程と、基板の表面に形成されている絶縁性被膜219及び基板の孔部の底面に形成されている絶縁性被膜218を除去し、孔部の内壁面に形成されている絶縁性被膜217を残存させる表底面側絶縁性被膜除去工程と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ダマシン法によるCu配線構造の形成において、Cu−Mn合金をバリアメタル膜に組み合わせて欠陥の自己修復および密着性の向上を図る際に、Mnの拡散によるCu配線パターンの抵抗増加を抑制する配線の製造方法を提供する。

【解決手段】半導体基板上方に形成された酸素を含む絶縁膜21と、前記絶縁膜に形成された凹部21Tと、凹部の内壁に形成された高融点金属膜22と、高融点金属膜上に形成された銅とマンガンと窒素を含む金属膜23と、金属膜上に形成され、凹部を充填する銅膜24Aと、を含む構造とする。

(もっと読む)

半導体装置およびその製造方法

【課題】配線抵抗を低く維持したままエレクトロマイグレーションの信頼性を向上できる半導体装置およびその製造方法を提供する。

【解決手段】銅配線層CL1は層間絶縁膜II2の表面の配線溝IT1内に形成されている。拡散防止絶縁膜DPは、銅配線層CL1上を覆うように形成されており、かつSiCおよびSiCNの少なくともいずれかよりなっている。絶縁膜SIは、拡散防止絶縁膜DPを介して銅配線層CL1上に形成されており、かつSiNよりなっている。

(もっと読む)

半導体装置の製造方法

【課題】WPP技術を使用する半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】半導体ウェハW3に形成されている製品チップ領域(例えば、製品チップ領域CAや製品チップ領域CB)に製品パターンを形成する。そして、製品チップ領域の外側にある外周領域の大部分にも製品パターンの一部を形成する。一方、外周領域に形成されているネーミング領域NRを覆うように開口部を有さないレジストパターンRMを形成する。外周領域に形成されているレジストパターンRMと製品チップ領域CBとの間に開口パターンKP1を形成する。このようなパターンが形成された半導体ウェハW3に対して、電解めっきを実施する。

(もっと読む)

電子装置及びその製造方法

【課題】絶縁膜とCuを含む配線との間に介在する下地膜であって、特に酸素のバリア性が高い下地膜を含む電子装置を提供する。

【解決手段】電子装置は、凹部の形成された絶縁膜と、凹部内に形成され、Cuを含む配線層と、絶縁膜と前記配線層との間に形成され、Ta及びMnを含む下地膜とを有する。

(もっと読む)

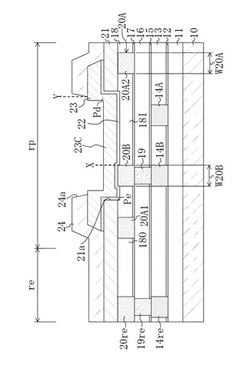

電磁波検出素子

【課題】信号配線の電子ノイズをより低減させた電磁波検出素子を提供する。

【解決手段】走査配線101(2)、信号配線3、及び共通配線102(18)をセンサ部103よりも下層に各々絶縁膜を介して設けられた異なる金属層により形成されており、信号配線3を走査配線101及び共通配線102よりも厚く形成した。

(もっと読む)

121 - 140 / 406

[ Back to top ]