Fターム[5F033JJ21]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | 高融点金属 (7,010) | Ta (1,326)

Fターム[5F033JJ21]に分類される特許

121 - 140 / 1,326

半導体装置

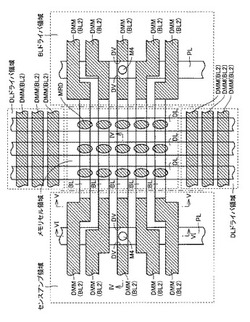

【課題】隣接するビット線同士の短絡が抑制されており、かつ層間絶縁膜が平坦に研磨された半導体装置を提供する。

【解決手段】磁気抵抗素子MRDが複数配置されたメモリセル領域と、平面視においてメモリセル領域の周囲に配置された周辺回路領域とを備える。磁気抵抗素子MRDは、磁化固定層と磁化自由層とトンネル絶縁層とを含んでいる。磁気抵抗素子MRDの上方には、主表面に沿った方向に向けて延びる複数の第1の配線BLを有している。上記周辺回路領域には、第1の配線BLと同一レイヤにより構成される第2の配線BL2と平面視において重なるように、磁化自由層と同一材質の層、トンネル絶縁層と同一材質の層および磁化固定層と同一材質の層が積層された積層構造DMMが配置されている。積層構造DMMは、周辺回路領域にて平面視において隣接する1対の第2の配線BL2の両方と重ならない。

(もっと読む)

半導体装置の製造方法

【課題】デュアルダマシン法による銅配線接続において、コンタクト抵抗の上昇を抑制する半導体装置の製造方法を提供する。

【解決手段】第1の配線25上に積層された第1の拡散防止膜27及び層間絶縁膜のうち、第1の層間絶縁膜28をエッチングすることで第1のホールを形成する。第1の拡散防止膜がエッチングされにくい条件で、第1のホールの下方に位置する第1の層間絶縁膜をエッチングして第2のホールを形成する。第2のホールを埋め込むように、第1の層間絶縁膜よりもエッチング速度の速い第2の層間絶縁膜を形成する。第1の層間絶縁膜の上面が露出するまで第2の層間絶縁膜をエッチングすることで、第2のホールと一体とされた配線形成用溝を形成する。第2のホール内に残存する第2の層間絶縁膜を選択的に除去し、第2のホールの下方に位置する第1の拡散防止膜を選択的に除去する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁層及び金属層の密着性を向上させる。

【解決手段】半導体基板1には、一方の平面1aから他方の平面1bに貫通するビアホール2が形成され、ビアホール2の底部2aとなる電極パッド層4が他方の平面1bに設けられている。この半導体基板1の一方の平面1a及びビアホール2の側壁部2bには、絶縁層6が形成されている。また、金属層7が、半導体基板1の一方の平面1a及びビアホール2の側壁部2bに絶縁層6を介して形成され、ビアホール2の底部2aに直接形成されている。ビアホール2の側壁部2bには、ビアホール2の底部2aにおける開口径がビアホール2の開口端部2cにおける開口径よりも大きくなるように傾斜面2dが形成されている。傾斜面2dには、複数の凹凸2eが形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】実効誘電率が低く、かつ信頼性の高いバリア絶縁膜を有する半導体装置を提供することができる。

【解決手段】半導体装置100は、層間絶縁膜10と、層間絶縁膜10中に設けられた配線20と、層間絶縁膜10上および配線20上に設けられたSiN膜30と、を備え、FTIRによって測定したSiN膜30のSi−N結合のピーク位置が845cm−1以上860cm−1以下である。これにより、配線金属の拡散を防ぐためのバリア絶縁膜である窒化シリコン膜において、リーク電流を抑制することができる

(もっと読む)

半導体構造およびその製造方法

【課題】カーボンナノチューブによりビアプラグを構成する半導体装置の製造方法において、製造効率を向上させる製造方法を提供する。

【解決手段】絶縁膜中にビアホールを形成し、ビアホールの底に触媒粒子3cを付着させる。ビアホール中において触媒粒子を起点に、カーボンナノチューブを絶縁膜の表面を超えて成長させ、複数のカーボンナノチューブよりなるカーボンナノチューブの束を形成する。絶縁膜上に前記カーボンナノチューブの束を覆って、誘電体膜の塗布液を塗布し、絶縁膜上における塗布液の厚さを、絶縁膜上における塗布膜の表面の高さが絶縁膜表面におけるカーボンナノチューブの高さ以下になるように減少させる。厚さが低減された塗布膜を硬化させて誘電体膜4Dを形成し、誘電体膜を除去して絶縁膜の表面を露出させ、絶縁膜の表面に、カーボンナノチューブによりビアプラグ4VA,4VBを形成する。

(もっと読む)

半導体装置及びその製造方法並びにそれを用いた積層型半導体装置

【課題】貫通電極に起因する応力を抑制し、半導体装置の動作を安定化し、半導体装置の信頼性を向上する。

【解決手段】半導体装置は、表面側に活性領域を有する半導体基板1と、半導体基板1の表面から裏面までを貫通するように形成され、導電材からなる貫通電極24と、貫通電極24に囲まれるように形成され、導電材とは異なる応力緩衝部25とを備えている。応力緩衝部25は、貫通電極24の内部であって半導体基板1の表面が横切る位置に形成されている。

(もっと読む)

半導体装置

【課題】半導体チップ内の銅配線が一部消失することを防ぐ。

【解決手段】上層プラグ一本当たりの下層の配線の面積が10000μm2以上になるような大面積の多層配線を有する半導体装置において、前記多層配線が半導体基板1Sの主面においてn型拡散層NSを介してpウエルPWに接続される構造を形成せず、前記多層配線をp型拡散層PSを介してpウエルPWに接続する構造、前記多層配線をp型拡散層PSを介してn型拡散層NSに接続する構造、前記多層配線をn型拡散層NSを介してnウエルに接続する構造、または半導体基板1S上に形成されたMISFETのゲート電極に接続する構造を形成する。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極やゲート配線及びソース配線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前記半導体層とを接続する接続電極と、前記半導体層と接続する画素電極とを有することを特徴としている。

(もっと読む)

半導体装置及びその製造方法

【課題】同層配線間の容量及び、上下層配線間の容量を低減し、配線間領域の実効誘電率を低減できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板上に形成された第1の絶縁膜101と、第1の絶縁膜101の上部に埋め込まれた複数の第1の配線120と、第1の絶縁膜101上及び複数の第1の配線120上に形成され、開口部を有するライナー絶縁膜104と、ライナー絶縁膜104上に形成された第2の絶縁膜107と、第2の絶縁膜107の上部に埋め込まれた複数の第2の配線110とを備える。第1の絶縁膜101における、第1の配線120の間であって、ライナー絶縁膜104の開口部と重なる部分には、絶縁膜によって塞がれたエアギャップ108が形成されており、第2の絶縁膜107の比誘電率は2.5以下である。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数を削減し、電気抵抗値のバラツキを低減して歩留まりを向上させる。

【解決手段】まず、半導体基板1の平面1aに、開口部を有するマスク層を形成し、次いで、半導体基板1に、マスク層の開口部から電極パッド層4に達するビアホール6を形成した後、マスク層を除去する。次に、金属層形成工程において、半導体基板1に形成したビアホール6の底部6aとなる電極パッド層4上に、電極パッド層4よりも絶縁材料の密着性が低い金属層8を形成する。次に、絶縁層形成工程において、化学気相成長法にて金属層8を除く部分、即ちビアホール6の側壁部6bに絶縁材料からなる絶縁層9を形成する。そして、導電膜形成工程において、半導体基板1の平面1a及びビアホール6の内部に導電層12を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、アルミ配線パターンに含まれるアルミニウムと銅配線に含まれる銅とが反応して高抵抗の合金が生成されることを防止した上で、導電膜である窒化チタン膜に起因する半導体基板の反りを低減することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】第2の層間絶縁膜18に形成されたコンタクト孔27により露出された銅配線16の上面16aを覆うように、窒化チタン膜を含む第1の導電膜21を設けると共に、アルミ配線パターン23と第1の導電膜21及び第2の層間絶縁膜18との間に、窒化チタン膜を含まない第2の導電膜22を設ける。

(もっと読む)

分離トレンチの形成方法

【課題】隣接デバイスの特性への悪影響を低減するTSV相互接続構造の製造方法を提供する。

【解決手段】第1の主面S1を有する基板を設け、少なくとも一つのTSV穴部と、TSV穴部を囲み残りの基板材料によって分離されるトレンチ状構造3、とをエッチングにより同時に作製する。基板の第1の主面でトレンチ状構造の開口をピンチオフするためと、TSV穴部側壁を平滑にするために、誘電性のライナー2a、2bを堆積し、トレンチ状構造にエアギャップ4を作製する。TSV相互接続10を生成するためにTSV穴部に導体材料を堆積する。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極のための開口部を形成する時に、上部配線層の配線とのミスアラインメント問題が発生しない半導体装置を製造する方法の提供。

【解決手段】第1面及び第1面の反対側に第2面を有する基板を準備する段階と、基板の第1面から基板の厚さ方向に延長して貫通電極が形成される領域に犠牲膜パターンを形成する段階と、基板の第1面上に形成され、犠牲膜パターン上に位置する配線を有する上部配線層を形成する段階と、基板の第2面を部分的に除去して犠牲膜パターンを露出させる段階と、犠牲膜パターンを基板の第2面から除去して配線を露出させる開口部を形成する段階と、開口部内に配線と電気的に接続される貫通電極を形成する段階と、を有する。

(もっと読む)

貫通電極基板の製造方法

【課題】材料コストが安く高周波特性が良好な貫通電極基板を簡便な工程で得ることができ、製造時間とコストの大幅な削減が可能な貫通電極基板の製造方法を提供する。

【解決手段】厚さ方向に形成された複数の貫通孔を有するガラス基板の前記貫通孔内に、導電性材料からなる貫通電極を有する貫通電極基板の製造方法であって、金属粒子を含む流動性の導電性組成物を前記ガラス基板上に塗布して、該導電性組成物を前記貫通孔内に充填する工程と、前記貫通孔内に充填された前記導電性組成物を加熱して、該貫通孔内に前記貫通電極を形成する工程を備える貫通電極基板の製造方法を提供する。

(もっと読む)

半導体装置、その製造方法、および半導体装置を含む半導体パッケージ

【課題】装置特性の低下を防止するとともに、半導体基板と貫通電極の短絡を防止する半導体装置を提供する。

【解決手段】第1面と、第1面と対向してトレンチが形成された第2面とを有する基板と、基板内に形成されたビアホールを充填し、ビアホールの内壁から順にビアホール絶縁膜、障壁膜、および導電性接続部を有してなる貫通ビアと、第2面上に形成されて貫通ビアの一部領域を露出する開口部を有する絶縁膜と、トレンチ内に埋め込まれ、貫通ビアと電気的に接続される再配線と、を有し、絶縁膜は導電性接続部の一部領域と重複する。

(もっと読む)

半導体装置の製造方法

【課題】 接続孔のホールサイズについて制御性良い半導体装置の製造方法を提供する。

【解決手段】 実施形態の半導体装置の製造方法では、半導体基板上に上層絶縁膜が形成され、前記上層絶縁膜上にSiを含む非晶質膜が形成される。前記非晶質膜上に第1のレジスト膜が形成され、前記第1のレジスト膜に第1のレジストパターンが形成される。前記第1のレジスト膜をマスクとして、前記非晶質膜が加工され、前記上層絶縁膜が露出される。前記第1のレジストパターンが除去され、前記非晶質膜および露出した前記上層絶縁膜上に遷移金属膜が形成される。前記非晶質膜および前記遷移金属膜の熱反応により、前記非晶質膜よりも体積が大きいシリサイド膜が形成される。前記遷移金属膜が除去され、前記シリサイド膜をマスクとして、前記上層絶縁膜を加工し、前記上層絶縁膜に第1の溝が形成される。

(もっと読む)

液晶表示装置及びその製造方法

【課題】製造に際して配線にヒロックが発生せず、かつエッチング形状の制御が容易な液晶表示装置を提供する。

【解決手段】液晶表示装置は、基板上にマトリクス配置された走査線と、信号線12と、前記走査線及び信号線に接続される薄膜トランジスタと、前記薄膜トランジスタに接続される画素電極27とを有する液晶表示装置において、前記走査線が下層からアルミニウム−ネオジム合金層211と高融点金属層212との積層構造からなり、前記信号線12が下層から高融点金属層231とアルミニウム−ネオジム合金層232と高融点金属層233との3層構造からなり、高融点金属の種類に応じて、ネオジム含有量を調整する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の多層配線において配線間隔を低減させても所定の低比誘電率を維持できるとともに、電気的特性の劣化などを抑制できる多孔性の層間絶縁膜の形成方法を提供する。

【解決手段】 半導体基板1上に形成される配線構造を構成し、空孔を有する多孔性絶縁膜13を得るための母体となる母体絶縁膜を気相成長法を用いて堆積する。この際、多孔性絶縁膜13の比誘電率、配線20間の間隔や絶縁耐圧のような、配線構造を決める因子に要求される設計値に応じて、多孔性絶縁膜13の分子骨格形成材料の流量に対する多孔性絶縁膜13の空孔形成材料の流量の比の、少なくとも範囲をまず決定する。この後、決定した流量比の範囲で母体絶縁膜を堆積し、この母体絶縁膜に熱や紫外線などのエネルギーを与えて空孔を有する多孔性絶縁膜13にする。

(もっと読む)

半導体装置

【課題】pn接合ダイオードの接合面積を大きくし、かつコストダウンを可能とすること。

【解決手段】半導体基板10とpn接合を形成する第1拡散領域32を含む第1pnダイオード33を含み、前記半導体基板上に形成された電子回路20と、前記電子回路とスクライブライン26との間の前記半導体基板内に設けられ前記電子回路を囲み前記第1拡散領域と同じ導電型であり前記半導体基板とpn接合を形成する第2拡散領域24を、含む第2pnダイオード23と、前記電子回路と前記スクライブラインとの間の前記半導体基板上に、前記第2拡散領域と重なるように設けられ、前記電子回路を囲む金属層18と、を具備する半導体装置。

(もっと読む)

121 - 140 / 1,326

[ Back to top ]