Fターム[5F033JJ21]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | 高融点金属 (7,010) | Ta (1,326)

Fターム[5F033JJ21]に分類される特許

161 - 180 / 1,326

カーボンナノチューブ配線の製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】カーボンナノチューブ配線の製造方法は、第1導電層200上に、絶縁膜18を形成し、前記絶縁膜内に、前記絶縁膜を貫通するホール40を形成し、前記ホール内の底面の前記第1導電層上および前記ホール内の側面の前記絶縁膜上に、触媒下地膜19を形成し、前記ホール内の側面の前記触媒下地膜上に、触媒不活性膜20を形成し、前記ホール内の底面の前記触媒下地膜上および前記ホール内の側面の前記触媒不活性膜上に、触媒膜21を形成し、前記ホール内の底面の前記触媒膜上から複数のカーボンナノチューブ22を成長させる。

(もっと読む)

半導体基板の製造方法

【課題】ビア配孔内に形成したカーボンナノチューブを埋め込む埋め込み膜が基板に均一に形成されないため基板の平坦化処理工程において層間絶縁膜が不均一に研磨されて、下層配線と上部電極がビア配線以外で電気的につながってしまう場合が発生する。

【解決手段】半導体基板における層間絶縁膜内のビアホール内にカーボンナノチューブを形成した後、基板全体をフッ化処理することにより、カーボンナノチューブが存在するビアホールにのみ埋め込み膜が形成され、その後に基板全体の平坦化処理のために基板を研磨する工程において、層間絶縁膜が局所的に研磨されることを防止する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

半導体装置およびその製造方法

【課題】ダマシン構造を有するCu配線において、バリア膜の拡散防止機能を低下させずにCu配線内のCuの埋め込み性を改善し、半導体装置の歩留まりおよび信頼性を向上する。

【解決手段】ダマシン配線を有する半導体装置において、第2層間絶縁膜6に形成した配線溝G2およびビアホールV2のそれぞれの内壁にバリア膜としてTaN膜7およびCuと濡れ性の良いTiからなるTi膜8とを順に形成することにより、Ti膜8上に均一にCuシード膜9aを形成することを可能とする。これにより、Cuシード膜9aを電極として電界メッキ法によりCu膜9を形成した際に、配線溝G2およびビアホールV2内に空隙が形成されることを防ぐ。

(もっと読む)

半導体装置とその作製方法

【課題】特性が良好なトランジスタを提供する。

【解決手段】例えば、ボトムゲート・ボトムコンタクト構造のトランジスタを作製するに際して、ソースとドレインを構成する導電層を3層の積層構造とし、2段階のエッチングを行う。すなわち、第1のエッチング工程には、少なくとも第2の膜及び第3の膜に対するエッチングレートが高いエッチング方法を採用し、第1のエッチング工程は少なくとも第1の膜を露出するまで行う。第2のエッチング工程には、第1の膜に対するエッチングレートが第1のエッチング工程よりも高く、「第1の膜の下に接して設けられている層」に対するエッチングレートが第1のエッチング工程よりも低いエッチング方法を採用する。第2のエッチング工程後にレジストマスクをレジスト剥離液により剥離するに際し、第2の膜の側壁が少し削られる。

(もっと読む)

半導体装置及び半導体装置の製造方法

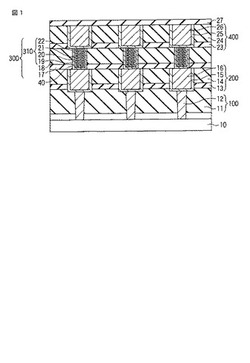

【課題】ビアに位置ずれが生じても、ビアがエアギャップにつながることを抑制できるようにする。

【解決手段】複数の配線240は例えばCu配線であり、互いに平行に延伸している。側壁絶縁膜212は、複数の配線240それぞれの側壁に形成されている。エアギャップは、複数の配線240それぞれの相互間に形成され、複数の側壁絶縁膜212の間に位置している。絶縁膜302は、複数の配線240上、複数の側壁絶縁膜212上、およびエアギャップ214上に形成されている。ビア344は絶縁膜302を貫通しており、いずれかの配線240に接続している。そして側壁絶縁膜212は、絶縁膜302がエッチングされる条件では絶縁膜302よりエッチングレートが低い材料により形成されている。

(もっと読む)

半導体装置の製造方法

【課題】CMP法による研磨のばらつきを抑制できる半導体装置の製造方法を提供する。

【解決手段】ウェハ1の周辺領域2の第3層間絶縁膜に、ダミーパターン41を形成する。ダミーパターン41は、ウェハ1の接線及び法線に交差する斜パターン42と、斜パターン42に連結され、ウェハ1の周方向に延びる分離パターン43とを有する。配線溝に導電性材料を埋め込んだ後に、CMP法により余分な導電性材料を除去するときは、ダミーパターン41に形成された溝を通って研磨剤が分散されるので、導電性材料や第3層間絶縁膜の研磨量が均一になる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間容量を低減する。

【解決手段】半導体装置の製造方法は、基板の上方に絶縁膜を形成する工程と、絶縁膜を貫通する第1の溝及び絶縁膜の内部で終端する第2の溝を絶縁膜に形成する工程と、絶縁膜の内部で終端する配線溝を絶縁膜に形成する工程と、第1の溝の表面及び配線溝の表面に第1の金属膜を形成するともに、第2の溝の上方を覆うように第1の金属膜を形成する工程と、第1の溝及び配線溝に第2の金属膜を埋め込む工程と、を備える。

(もっと読む)

配線基板、半導体装置、及びそれらの作製方法

【課題】集積化が進む配線基板、又は半導体装置において、導通不良を軽減する。信頼性の高い配線基板、又は半導体装置を歩留まり良く作製する。

【解決手段】多層配線構造を有する配線基板、又は半導体装置において、該配線に用いる導電層の接続構造に曲面を有する導電層を用いる。周囲の絶縁層の除去によって露出された下層の導電層の先端部は曲面であり、下層の導電層上に積層する上層の導電層の被覆性を良好とすることができる。曲面な表面を有するレジストマスクを用いて導電層をエッチング加工することによって曲面な表面を有する導電層を形成する。

(もっと読む)

半導体装置

【課題】ディッシング及び埋め込み不良のないパッド構造を短時間で安定して形成する。

【解決手段】基板100上に形成された第1の絶縁膜108Bに、複数のパッド配線109pを含むパッドが形成されている。第1の絶縁膜108B上に、前記パッドの少なくとも一部分の上に位置する開口部を有する第2の絶縁膜110が形成されている。複数のパッド配線109pのうち互いに隣り合う配線同士を電気的に接続するように配線接続部109qが設けられている。各パッド配線109pの幅W1は、各パッド配線109pの高さよりも小さく且つ配線接続部109qの幅W3よりも大きい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】機械的強度および密着力に優れた低誘電率の層間絶縁層を有する半導体装置を提供すること。

【解決手段】基板上に形成された、SiO2骨格を含む第1の多孔質層6と、第1の多孔質層6の直上に形成された、SiO2骨格を含む第2の多孔質層7と、第1の多孔質層6に埋め込まれたビア10と、第2の多孔質層7に埋め込まれた配線11と、を有し、第1の多孔質層6の孔密度x1は40%以下であり、第2の多孔質層7の孔密度x2は、(x1+5)%以上である半導体装置を提供する。

(もっと読む)

半導体装置の作製方法

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置の作製方法を提供することを目的の一とする。

【解決手段】酸化物半導体膜と、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有する半導体装置の作製方法であって、酸化物半導体膜上に接して、酸化ガリウムを含む第1の絶縁膜を形成し、第1の絶縁膜上に接して第2の絶縁膜を形成し、第2の絶縁膜上にレジストマスクを形成し、第1の絶縁膜および第2の絶縁膜にドライエッチングを行ってコンタクトホールを形成し、レジストマスクを、酸素プラズマによるアッシングを用いて除去し、コンタクトホールを介して、ゲート電極、ソース電極またはドレイン電極のいずれか一または複数と電気的に接続される配線を形成する、半導体装置の作製方法である。

(もっと読む)

固体撮像装置

【課題】 暗電流やリーク電流の発生を抑制することが可能な固体撮像装置を提供する。

【解決手段】 固体撮像装置は、光電変換素子が主面に配された第1基板と、導電体を含む第1の接合部を有する第1配線構造と、周辺回路の一部が主面に配された第2基板と、導電体を含む第2の接合部を有する第2配線構造と、を有する。そして、第1基板と、第1配線構造と、第2配線構造と、第2基板とがこの順に配置されるように第1の接合部及び第2の接合部とが接合されている。そして、第1の接合部の導電体と、第2の接合部の導電体とは、導電体に対する拡散防止膜で囲まれている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】研磨工程を含む新規な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、絶縁膜を形成する工程と、絶縁膜に、第1の深さを有するダミー溝と、第1の深さよりも深い第2の深さを有する配線溝と、配線溝の底面に配置されるビアホールとを形成する凹部形成工程と、ダミー溝内、配線溝内、ビアホール内、及び絶縁膜上方に、導電材を堆積させる工程と、絶縁膜上方の導電材を研磨除去する工程とを有する。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子のビア構造物及び導電構造物を提供する。

【解決手段】前記ビア構造物は、平坦部及び突出部を含む表面を有する。前記導電構造物は前記平坦部のうち、少なくとも一部上に形成され、前記突出部のうち、少なくとも一部上には形成されない。例えば、前記導電構造物は前記平坦部上のみに形成されて前記突出部上には全く形成されない。これによって、前記導電構造物と前記ビア構造物との間に高品質の接続を形成することができる。

(もっと読む)

半導体装置の製造方法、配線用銅合金、及び半導体装置

【課題】半導体装置の歩留まりと信頼性を向上させる。

【解決手段】配線凹部に埋め込まれた部分以外のバリアメタル膜3b上のCu膜5bを化学機械研磨によって除去する。そして配線凹部内のCu膜5b上に、添加元素からなる層6bを形成する。添加元素を層6bからCu膜5b中に拡散させて、Cu表面、及びCu結晶粒の粒界及び該粒界近傍の位置においてCu結晶粒内部よりも添加元素の濃度が高い界面及びその近傍を形成するとともに、Cu膜5b中の酸素を層6bにゲッタリングさせる。その後、余剰な層6bを除去し、さらに絶縁膜上のバリアメタル膜3bを除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体集積回路の高集積化と機能素子の高性能化とを同時に実現する。

【解決手段】実施形態に係わる半導体装置は、半導体基板1の表面領域に配置されるスイッチ素子3,4と、下面がスイッチ素子3,4に接続されるコンタクトプラグ6と、コンタクトプラグ6の上面の直上に配置される機能素子7とを備える。コンタクトプラグ6の上面の最大表面粗さは、0.2nm以下である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】歩留まりに優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、基板内の記憶回路領域に形成されており、多層配線層内に埋め込まれた少なくとも1以上の容量素子および周辺回路を有する記憶回路と、平面視において、基板内の憶回路領域とは異なる領域である論理回路領域に形成された論理回路と、を備え、容量素子は、下部電極、容量絶縁膜、上部電極、埋設電極および、上部接続配線で構成されており、上部接続配線と埋設電極とは、同一の材料かつ一体に構成されており、上部接続配線と下部電極との間には、論理回路を構成する前記配線が少なくとも1以上設けられており、上部接続配線の上面と、上部接続配線と同じ配線層に形成された論理回路を構成する配線の上面とが、同一面を構成する。

(もっと読む)

半導体装置及びその作製方法

【課題】微小なコンタクトホールを形成し、集積回路を微細化することを目的とする。

【解決手段】スイッチング素子および各配線を覆う層間絶縁膜111として有機材料を用い、且つ、金属膜112のマスクを用い、ドライエッチング法によってコンタクトホールを形成し、配線114を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】積層される半導体基板同士が、貫通孔の内部に埋め込まれる導電体により、電気的に良好に接続される半導体装置を提供する。

【解決手段】第1半導体基板SCPは、主表面を有する基板SUBと、基板SUB内および基板SUB上に形成された半導体素子TRと、半導体素子TRに電気的に接続された配線MTLと、基板SUBの主表面であり、互いに対向する第1主面と第2主面とを貫通し、配線MTLに達する貫通孔の内部に形成された導電層TSVとを有する。第1半導体基板SCPと第2半導体基板SCPとが積層され、導電層TSVは第2半導体基板SCPの配線MTLと電気的に接続される。導電層TSVの第2主面では、貫通孔の端部の周囲には凹部DUMが形成され、凹部DUMの底壁面は基板SUBの内部に存在する。導電層TSVを構成する導電材料CUが凹部DUMの内部に充填される。

(もっと読む)

161 - 180 / 1,326

[ Back to top ]