Fターム[5F033JJ27]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | シリサイド (585) | 高融点金属のシリサイド (433) | TiSi (189)

Fターム[5F033JJ27]に分類される特許

161 - 180 / 189

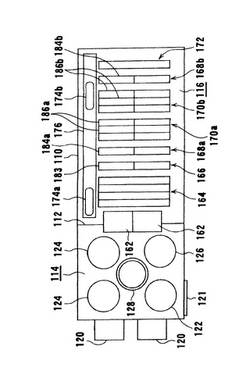

めっき装置及びめっき方法

【課題】 比較的簡単な構成で、例えアスペクト比が高く、深さが深いビアホール等にあっても、金属膜を内部にボイドを発生させることなく確実に埋込むことができるようにする。

【解決手段】 第1めっき液を該第1めっき液にアノードを浸漬させて保持する第1めっき槽170aと、第1めっき液より金属濃度の低い第2めっき液を該第2めっき液にアノードを浸漬させて保持する第2めっき槽170bと、第1めっき槽170aと第2めっき槽170bとの間を移動自在で、被めっき材を該被めっき材に通電可能に保持するホルダ160を有し、ホルダ160で保持した被めっき材を第1めっき槽170a内の第1めっき液に接触させて行う第1めっき処理と、第2めっき槽170b内の第2めっき液に接触させて行う第2めっき処理を順次繰返す。

(もっと読む)

被覆キャップを有する相互接続構造およびその製造方法

【課題】 製造許容値を緩和した相互接続構造を提供する。

【解決手段】 相互接続構造を製造する方法であって、誘電層に相互接続部を設けるステップと、相互接続部の一部が誘電層の上面よりも上に延出するように誘電層をくぼませるステップと、相互接続部の延出した部分の上に被覆キャップを堆積するステップと、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 信頼性に優れた銅配線層を有する半導体装置およびその製造方法を提供する。

【解決手段】 第1の層間絶縁膜1および第1の銅配線層3の上に、拡散防止膜4、第2の層間絶縁膜5および第3の層間絶縁膜11を順に形成し、第1の銅配線層3に至る接続孔6を形成する。また、第3の層間絶縁膜11に接続孔6に対応する配線溝7を形成した後、接続孔6および配線溝7の内面を被覆するようにして、第3の層間絶縁膜11の上に第2のバリアメタル膜8を形成する。接続孔6の底部における第2のバリアメタル膜8を除去し、さらに第1の銅配線層3の上面を断面で見て凹状に加工した後、ALD法またはCVD法により、第2のバリアメタル膜8の上および第1の銅配線層3の上に、窒化タンタル、チタンおよびタングステン並びにこれらの窒化物および窒化圭化物よりなる群から選ばれる1の材料からなる膜を形成する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】白金族金属、白金族合金または白金族金属の導電性酸化物を主成分とする膜を電極材料に用いた容量素子を有するDRAMの微細化を推進する。

【解決手段】酸化シリコン膜43に溝44を形成した後、あらかじめ酸化シリコン膜43の下層に形成しておいた導電性下地膜42をカソード電極とする電解メッキ法によって、溝44の内部にPt膜45を形成する。その後、酸化シリコン膜43をエッチングで除去した後、Pt膜45をマスクにして導電性下地膜42をドライエッチングすることにより、Pt膜45とその下部に残った導電性下地膜42とで容量素子の下部電極を形成する。

(もっと読む)

表面被覆方法、及び該方法を使用するマイクロエレクトロニクス相互接続の作製、並びに集積回路

本発明は、基板の表面を、金属材料から作られる核生成フィルムで被覆する方法に関し、前記表面は、導電性又は半導電性表面であり、凹部及び/又は凸部を含む。 本発明方法は、有機フィルムを表面上に蒸着する工程であって、前記フィルムの厚さが、その自由面が、導電性又は半導電性表面(その上に、フィルムが蒸着されている)の凹部及び/又は凸部に共形的にならうものから成る工程;金属材料の前駆体を、表面上に蒸着した有機フィルムに挿入する工程であって、前記表面上に有機フィルムを蒸着させることから成る工程と同時の又はその後に続く工程;及び金属材料の前駆体を金属材料に変換する工程にある。 本発明方法は、集積回路、超小型電子相互接続及びマイクロシステムの製造のために使用することができる。  (もっと読む)

(もっと読む)

工業製品の製造方法

【課題】各製造工程段階の評価が正確且つ現実的に適用できる工業製品の製造方法を提供する。

【解決手段】工業製品の実マスクによるリソグラフィ工程を利用して、被処理基体の表面に、工業製品の一部をなす実パターン112j-2,112j-1,112j,112j+1,112j+2を形成する工程と、この実パターンの上に配線変更用絶縁膜を形成する工程と、この配線変更用絶縁膜の一部を実パターンの一部が露出するように選択的に除去し、複数の電位抽出用コンタクトホール113j-2,113j-1,113j,113j+1,113j+2;を開口する工程と、電位抽出用コンタクトホールを介して実パターンに電気的に接続される複数の評価用引出し配線111i,111i+1,を形成する工程と、この評価用引出し配線を用いて、実パターンのパターン欠陥を電気的に検出する工程とを含む。

(もっと読む)

インシチュ薄膜蒸着方法

【課題】TiSiX/Ti膜またはTiSiX/Ti/TiN膜を連続的に蒸着できるインシチュ薄膜蒸着方法を提供する。

【解決手段】インシチュ薄膜蒸着方法は、内部にロボットアーム11が設置される移送チャンバ10と、移送チャンバ10にクラスタータイプに設置されて内蔵された基板W上に薄膜を蒸着する複数個のチャンバ20、30、50とを備える薄膜蒸着装置を利用して、基板W上に抵抗性コンタクト及びバリヤーの役割を行う薄膜を蒸着するに際し、任意のチャンバに、Ti元素を含む第1反応ガスとSi元素を含む第2反応ガスとを供給し、チャンバ20の内部にプラズマを印加して、基板WにTiSiX膜を蒸着し、基板Wを移送チャンバ10を介して他のチャンバ30に移送した後、TiSiX膜上にTiN薄膜を蒸着する。

(もっと読む)

多孔性低k誘電体膜上への不透過性膜の堆積方法

【課題】多孔性低k誘電体膜上に不透過性膜を堆積させる方法を提供する。

【解決手段】相互接続構造における多孔性低k誘電体膜のようなデバイス上への不透過性膜の接着性を改善するための方法。本方法は、多孔性低k誘電体膜の水、アルコール、HCl、HF蒸気のような捕捉された蒸気又は吸着された分子を放出するために、不透過性膜の堆積前の原位置アニーリング段階を提供する。本方法はまた、多孔性低誘電性膜の堆積に続いて、捕捉可能分子を含む大気に露出することなく不透過性膜の原位置堆積を提供する。本方法は、更に、多孔性低k誘電体膜の一部分の除去に続いて、捕捉可能分子を含む大気に露出することなく不透過性膜の原位置堆積を提供する。実質的に全ての捕捉又は吸着分子を多孔性低k誘電体膜から除去することにより、堆積した不透過性膜と低k誘電体膜の間の接着性が改善される。本方法は、多孔性ハイドロシルセスキオキサン又は多孔性メチルシルセスキオキサン、エアロゲルのような多孔性シリカ構造体、低温堆積シリコン炭素膜、低温堆積Si−O−C膜、及びメチルドープ多孔性シリカのような多くの多孔性低k誘電体膜に特に適用可能である。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】銅を主導体膜とする配線間の絶縁破壊耐性を向上させる。

【解決手段】複数の配線層N1〜Nxのうち、ウエハの主面に相対的に近い配線層N1の配線形成工程においては、埋込配線Lnの上面と絶縁膜12bの上面との間に段差が形成されるようにし、複数の配線層N1〜Nxのうち、ウエハの主面から相対的に遠い配線層Nxの配線形成工程においては、上記段差を形成する工程を経ずに、主導体膜18aの上面が絶縁膜12bの上面とほぼ一致した状態で絶縁膜15bを堆積する。これにより、TDDB寿命を向上させることができ、また、プロセス上の制約を満たすことができるので、全体的に信頼性の高い半導体装置を提供することが可能となる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】半導体集積回路装置の高速化を図り、また、エレクトロマイグレーションやストレスマイグレーションの発生を抑え、配線寿命を長くする技術を提供する。

【解決手段】半導体基板1上に形成された酸化シリコン膜23および窒化シリコン膜22中の配線溝内を含む酸化シリコン膜23上にバリア層26aおよび銅膜26bを順次形成後、前記配線溝外部のバリア層26aおよび銅膜26bを除去することによって配線26を形成し、配線26上にタングステンを選択成長もしくは優先成長させることにより、配線26上にタングステン膜26cを形成する。

(もっと読む)

半導体装置の製造方法

【課題】 Cu系金属を充填したダマシン配線の信頼性、特にストレスマイグレーション(SM)耐性を向上させる。

【解決手段】 下地絶縁膜1上の層間絶縁膜2にトレンチ3を設け、トレンチ3に第1バリアメタル膜5を介して埋め込む第1Cu膜6を成膜し、20℃〜200℃範囲の第1の熱処理を施し清浄化した第1Cu膜6aにする。次に、第1Cu膜6aの第1キャップ層2c上の不要部分を化学的機械研磨で除去し、上記トレンチ3にCu配線8を形成する。その後に、300℃〜400℃の温度でCu配線8に第2の熱処理を施し、結晶性の優れたCu配線8aを形成する。同様に、ビアホールに埋め込む第2Cu膜を成膜した後に、300℃〜400℃範囲の第3の熱処理を施し、その後に化学的機械研磨してCuビアプラグを形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】特にゲート電極に逆バイアス電圧が印加された際のリーク電流(オフ電流)が低い薄膜トランジスタ(TFT)を得る。

【解決手段】絶縁表面上に形成された非単結晶珪素からなる活性層と、前記活性層に接して形成されたゲイト絶縁膜と、前記ゲイト絶縁膜に接して形成されたゲイト電極とを有する薄膜トランジスタを含む半導体装置において、前記活性層は、チャネル形成領域と、酸素、炭素および窒素の濃度が前記チャネル形成領域よりも高く、かつ、N型またはP型の不純物を有するソース領域およびドレイン領域とを有することを特徴とする半導体装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】配線と接続部との間の接触抵抗を低減し、エレクトロマイグレーション特性を向上させる。

【解決手段】その表面に、配線を構成する銅の拡散等を防止するためのタングステン膜CM1が形成された第1層配線上の絶縁膜(24a、24b、24c、26b、26c)をエッチングすることによりコンタクトホールC2および配線溝HM2を形成する際、コンタクトホールC2底部のタングステン膜CM1を除去し、バリア膜PM2aを形成した後、コンタクトホールC2底部のバリア膜PM2aを除去し、銅膜(PM2b、PM2c)を形成した後、その表面を研磨することにより第2層配線M2およびその下層のプラグP2を形成する。また、タングステン膜CM1又はバリア膜PM2aの少なくとも一方を除去するか、それらを不連続な膜で構成する。その結果、第1層配線M1とプラグP2との間の接触抵抗を低減できる。

(もっと読む)

銅配線層の形成方法、半導体装置の製造方法

【課題】 細りのない所望する断面積の銅配線を形成することができる銅配線層の形成方法および半導体装置の製造方法を提供すること。

【解決手段】 基板1上に下地絶縁膜2、下地バリア層3、銅シード層4を順次成膜したのち、この銅シード層4上にフォトレジスト層5の配線溝6パターンを形成し、この配線溝6の底部に露出した銅シード層4上に銅配線層7を形成し(図2(a))、この層7上に保護層8を形成したのちこの層8をマスクとしてフォトレジスト層5、銅シード層4、下地バリア層3を順次エッチングして図2(e)に示す銅配線層7のパターンを形成する。

この層7からの銅の拡散を防止するため表面に層間絶縁層を形成する。

(もっと読む)

成膜方法、半導体装置の製造方法、半導体装置、プログラムおよび記録媒体

【課題】 半導体装置のCu拡散防止膜とCu配線との密着力を良好とし、半導体装置の信頼性を良好とする。

【解決手段】 被処理基板上にCu膜を成膜する成膜方法であって、前記被処理基板上に形成されたCu拡散防止膜上に密着膜を形成する第1の工程と、前記密着膜上にCu膜を成膜する第2の工程と、を有し、前記密着膜はPdを含むことを特徴とする成膜方法。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】 リフレッシュ動作を必要とせず、かつ、高集積化・大容量化を実現する半導体記憶装置を提供する。

【解決手段】 半導体基板1上に形成されたメモリセルと、第1電荷保持部と、第2電荷保持部と、第1アクセストランジスタと、第1リークトランジスタ522Aと、第2アクセストランジスタと、第2リークトランジスタと、層間絶縁膜16と、層間絶縁膜16上に形成され、第1電荷保持部に接続されたメモリセル内の第1MISFET56A(Metal-Insulator-Semiconductor Field Effect Transistor)と、層間絶縁膜16上に形成され、第2電荷保持部と接続されたメモリセル内の第2MISFET(Metal-Insulator-Semiconductor Field Effect Transistor)とを備える。

(もっと読む)

自動設計装置、自動設計方法、及び半導体集積回路

【課題】 斜め配線と直交配線とを有する多層配線構造の半導体集積回路においてクロストークの発生を抑制でき、ビアホールの配置制約の少ない半導体集積回路が設計可能な自動設計装置、自動設計方法、及び半導体集積回路を提供する。

【解決手段】 第1線群及び第2線群により定義される第1格子領域401a及び第3線群及び第4線群により定義される第1斜め格子領域402aを第1配線層400a上に設定し、第1〜第4線群を基準として第1配線41a及び第1斜め配線42aを第1配線層400a上に配置する第1層配線部14と、第1格子領域401a及び第1斜め格子領域402a上に重なる位置に、第2格子領域501a及び第2斜め格子領域502aを第2配線層500a上に設定し、第1〜第4線群を基準として、第2配線51a及び第2斜め配線52aを第2配線層500a上に配置する第2層配線部15とを含む。

(もっと読む)

半導体装置の製造方法

【課題】 微細且つ電気的特性に優れた半導体装置の製造方法を提供する。

【解決手段】 層間絶縁膜10をマスクとしたストッパー膜9のドライエッチングによって、拡散層領域8に至るコンタクトホール11を形成する。この際、ストッパー膜9のオーバーエッチングによって、コンタクトホール11の底面をシリコン基板1の表面よりリセスする。続いて、シリコン基板1の表面を洗浄した後、コンタクトホール11の内面を覆うようにして層間絶縁膜10の上にポリシリコン膜12を形成する。ポリシリコン膜12の膜厚は、コンタクトホール11の底面がシリコン基板1の表面に対してリセスした深さより大きく、シリサイド化で消費されるシリコンの厚さより小さくなるようにする。これにより、オーバーエッチングおよびシリサイド化によってシリコン基板1から消失するシリコンの量を低減させることができる。

(もっと読む)

キャップ層を有する半導体相互接続構造上に金属層を堆積させる方法

【課題】

【解決手段】半導体ウェハの相互接続構造上に金属層を堆積させる方法を開示する。この方法では、金属導体を、キャップ層および誘電体層で被覆する。キャップ層を露出させるように、誘電体層をパターン形成する。次いで、キャップ層をスパッタ・エッチングして除去し、金属導体を露出させる。スパッタ・エッチング・プロセス中に、キャップ層がパターンの側壁に再堆積する。最後に、パターンの中に少なくとも1つの層を堆積させ、再堆積したキャップ層を被覆する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトと該コンタクトの上側の配線とのショートマージンを稼いだ半導体装置を得ること。

【解決手段】半導体基板1上に形成される所定形状の第1層配線10を含む第1の配線層8と、該第1の配線層8上に形成される層間絶縁膜11と、該層間絶縁膜11上に形成され、所定形状の第2層配線15を含む第2の配線層13と、第1層配線10と第2層配線15とを電気的に接続するコンタクト12と、を備える半導体装置において、コンタクト12は、所定の深さから上方に行くにしたがって積層方向におけるその断面形状が小さくなるように形成される。

(もっと読む)

161 - 180 / 189

[ Back to top ]