Fターム[5F033JJ27]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | シリサイド (585) | 高融点金属のシリサイド (433) | TiSi (189)

Fターム[5F033JJ27]に分類される特許

121 - 140 / 189

半導体装置およびその製造方法

【課題】従来の半導体装置では、微細化したコンタクトホールでの安定したコンタクト抵抗と、信頼性の高いアルミニウム配線とを両立することはできないという課題があった。

【解決手段】本発明の半導体装置は、コンタクトホールの内部と配線形成部とに、配向の異なるバリア層を有する。このバリア層は、チタン膜と窒化チタン膜とチタン膜との3層構造であって、配線形成部に形成するバリア層の(002)配向性がコンタクトホールの内部のバリア層の(002)配向性よりも高い。このような構成とすることによって、安定したコンタクト特性と、高エレクトロマイグレーション耐性とを有する半導体装置を構成することができる。

(もっと読む)

半導体接合部に薄膜物質を選択的に堆積させる方法

本発明の実施形態は、基板上に形成されたデバイスに高品質コンタクトレベル接続部を形成するプロセスを提供する。一実施形態において、基板上に物質を堆積させるための方法であって、基板を酸化物エッチング緩衝液にさらして、前処理プロセスで水素化シリコン層を形成するステップと、基板上に金属シリサイド層を堆積させるステップと、金属シリサイド層上に第一金属層(例えば、タングステン)を堆積させるステップと、を含む前記方法が提供される。酸化物エッチング緩衝液は、フッ化水素とアルカノールアミン化合物、例えば、エタノールアミン、ジエタノールアミン、又はトリエタノールを含有することができる。金属シリサイド層は、コバルド、ニッケル、又はタングステンを含有することができ、無電解堆積プロセスによって堆積させることができる。一例において、基板は、溶媒と金属錯体化合物を含有する無電解堆積溶液にさらされる。 (もっと読む)

半導体装置

【課題】Cu配線などの金属配線について、金属配線と金属拡散防止膜との密着性が向上し、金属配線のエレクトロマイグレーション耐性向上により金属配線寿命の長い半導体装置を提供する。

【解決手段】半導体基板上に形成された第1の絶縁膜中の溝部内に設けられ、銅および銅の合金のうち少なくとも1つを含有する第1の金属配線と、第1の金属配線および第1の絶縁膜の露出面を覆う第1の金属拡散防止膜を有する半導体装置において、第1の金属配線は金属シリサイド層を含有しないシリコン含有金属配線であり、第1の金属配線全体にシリコンを含む構成である。

(もっと読む)

半導体装置およびその製造方法

【課題】自然酸化膜下に位置する半導体基板や金属膜がオーバエッチングされず、位置によって厚みの異なる自然酸化膜を良好に除去できる半導体装置の提供。

【解決手段】半導体基板1の主表面に、第1導電型の第1不純物を導入して第1不純物領域3、4を形成する工程と、第2導電型の第2不純物を導入して第2不純物領域33、34を形成する工程と、第1不純物領域1上に第1ニッケルシリサイド膜21、22を形成すると共に、第2不純物領域33、34上に第2ニッケルシリサイド膜41、42を形成する工程と、NH3ガスと水素元素を含むガスとが混合された混合ガスを用いて、第1、第2ニッケルシリサイド膜21、22上に形成された酸化膜を除去する工程と、酸化膜を除去した状態で、第1ニッケルシリサイド膜21、22上に第1導電膜6a、7a、を形成すると共に、第2ニッケルシリサイド膜上に第2導電膜36a、37aを形成する工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体プロセスの微細化に伴い、信頼性の高い微細なゲート電極の形成がより困難なものとなっている。

【解決手段】ゲート電極105の上面に加え、ゲート電極105の側面に対しても金属シリサイド110を形成することで、ゲート電極105を所望の太さの幅に拡大しなくても、信頼性の高いゲート電極105を形成することができる。

(もっと読む)

電気光学装置及びその製造方法、並びに導電層の接続構造

【課題】画素の開口率を高める。

【解決手段】液晶装置1は、TFTアレイ基板10上の互いに異なる層に夫々形成されており、第2層間絶縁膜42を介して互いに電気的に絶縁された上部容量電極300及び下部容量電極71、サイドウォール91、接続用導電膜93、誘電体膜75及びコンタクトホール85を備えている。接続用導電膜93によれば、コンタクトホールを形成する際のマージンを確保するために広げざるを得なかった下部容量電極71及び上部容量電極300の面積を低減でき、画素毎の開口領域の間隙に位置する非開口領域を低減することが可能である。これにより、画素における非開口領域の幅W1をサイドウォール91の幅W2に応じて低減でき、非開口領域を狭めることによって画素における開口率を高めることが可能である。

(もっと読む)

銅でないメッキ可能層の上への銅の直接電気メッキのための方法

【課題】銅でないメッキ可能層の上への銅の直接電気メッキのためのプロセスを提供する。

【解決手段】半導体構造物中に相互配線を形成するためのプロセスであって、基板の上に誘電体層を形成する工程と、誘電体層の上に第一の障壁層を形成する工程と、第一の障壁層の上に第二の障壁層を形成する工程であって、第二の障壁層は、ルテニウム、白金、パラジウム、ロジウムおよびイリジウムからなる群から選ばれ、第二の障壁層の形成は、第二の障壁層中の酸素のバルク濃度が20原子パーセントまたはそれ未満となるように操作される工程と、第二の障壁層の上に導電層を形成する工程と、を含むプロセス。本プロセスは、さらに、第二の障壁を処理して第二の障壁層の表面の酸化物の量を減少させる工程を含むことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】封止される被対象物に段差部を備えているが、封止部を設けた際に該段差部に起因したボイドの発生が抑制され、ひいては優れた耐食性を備える半導体装置と、その製造方法を提供する。

【解決手段】本発明に係る半導体装置1は、導電性を有する剛体からなる基板2と、該基板の少なくとも一方の面に絶縁部3を介して配された導電部5と、該絶縁部及び該導電部を覆うように配された感光性樹脂からなるフィルム6と、を備えている。前記基板2は、一方の面に開口する凹部及び/又は貫通孔2aを備え、該凹部及び/又は該貫通孔はその内部が略全域にわたって、前記フィルム6により充填されている形態をなす。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性を向上することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、以下の工程を備えている。下部配線14が形成された層間絶縁膜11上に層間絶縁膜1を積層して形成する。下部配線14に達する上部孔5を層間絶縁膜1に開口する。上部孔5に連通するトレンチ6を形成する。上部孔5内をウエットエッチングすることにより、下部孔17を下部配線14内に形成する。トレンチ6の側面および底面と、上部孔5の側面と、下部孔17の底面とにバリアメタル2を形成する。下部孔17の底面に存在するバリアメタル2を物理的にエッチングすることにより、下部孔17の側面17aに導電膜15を形成する(エッチング工程)。エッチング工程の後に、Nなどの元素を含むプラズマを用いて層間絶縁膜1を形成する。トレンチ6内、上部孔5内および下部孔17内を埋めるようにCu膜4を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を備えた半導体装置を積層した3次元半導体装置において、貫通電極の抵抗と容量が大きく、高速データ転送ができないという問題がある。

【解決手段】貫通電極をゲート電極の第1導電膜をマスクとして形成する。第1導電膜の上に成膜されたゲート電極の第2導電膜を、貫通電極の配線電極とする。ゲート電極形成工程において貫通電極を形成することで高融点金属およびその化合物が使用でき、低抵抗化が図れる。さらに貫通電極からの配線工程をゲート電極からの配線工程と共有化する等、半導体標準プロセスに適合させることで工程を短縮することができる。

(もっと読む)

CMOS対応の浅いトレンチのeフューズ構造体及びその製造方法

【課題】 少なくとも1つのeヒューズを含む半導体構造体と標準的な半導体技術との統合が容易であり、よって実施コストが最小になる製造方法を提供する。

【解決手段】 半導体基板(バルク又は半導体オン・インシュレータ)内に配置されたトレンチ内に埋め込まれた少なくとも1つのeヒューズを含む半導体構造体が提供される。本発明によると、eヒューズは、半導体基板内に配置されたドーパント領域と電気接触した状態にある。本発明はまた、埋め込まれたeヒューズが、トレンチ分離領域とほぼ同時に形成される半導体構造体を製造する方法も提供する。

(もっと読む)

相変化メモリ装置および相変化メモリ装置の製造方法

【課題】相変化メモリ装置における良好な電気特性と良好な熱特性を両立させ、電極や配線の材料選択の自由度も高めて、大規模な相変化メモリ装置の量産を可能とすること。

【解決手段】ヒータ電極110と相変化層114の接触界面112の近傍で発生するジュール熱が、ヒータ電極110を介して下方に伝達され、下地の良導電性の金属コンタクトプラグから放熱されることを抑制するために、異種材料コンタクトプラグ104(106,108)を採用する。ヒータ電極110に接触する第1の導電材料プラグ106は、ヒータ電極110の構成材料と同種または同じ金属材料からなり、第2の導電材料プラグ108は、接地電位用プラグ100や接地配線102と同種あるいは同じ金属材料からなる。両プラグ106,108は、共通のコンタクトホール内に積層形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】抵抗特性が改善され、信頼性が向上する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、下部配線110、層間絶縁膜100、200、拡散防止膜120、240、上部配線230を備えている。層間絶縁膜200は、下部配線110上に形成され、下部配線110の上面が露出するビアホール230aを有する。拡散防止膜240は、ビアホール230aの両側壁に形成される。上部配線230は、ビアホール230aを埋め込み、下部配線110と直接接触する。下部配線110内にはビアホール230aの延びる方向に拡散防止膜120の成分を含む不純物領域130が形成される。

(もっと読む)

半導体素子及びその製造方法

【課題】オーミックコンタクト膜の形成を最適化して抵抗特性と漏洩電流特性などを向上させうる半導体素子及びその製造方法を提供する。

【解決手段】基板101の活性領域130上に形成されたシリサイド膜と、基板101の活性領域230上に形成されたシリサイド膜535とを備えている。シリサイド膜及びシリサイド膜535は、実質的に異なる厚さを有している。また、活性領域230は活性領域130に比べて密度の高いパターンを含んでいる。

(もっと読む)

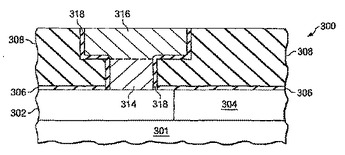

細孔シーリングライナーのデュアルダマシン方法及びデバイスへの統合

デバイスは、細孔シーリングライナーを有するダマシン層を使用し、半導体ボディを含んでいる。金属相互接続(302)からなる金属相互接続層が、半導体ボディ上に形成される。誘電層(308)が、金属相互接続層上に形成される。導電性トレンチフィーチャ(316)及び導電性バイアフィーチャ(314)が、誘電層内に形成される。細孔シーリングライナー(318)が、導電性バイアフィーチャの側壁に沿ってのみ、及び導電性トレンチフィーチャの側壁及び底面に沿って形成される。細孔シーリングライナーは、導電性バイアフィーチャの底面に沿っては実質的に存在しない。  (もっと読む)

(もっと読む)

触媒及び化学気相蒸着法を用いて銅配線及び薄膜を形成する方法

【課題】触媒を使用した銅CVD方法として、ピンチ−オフやボイドの発生なしにトレンチ、ビアホール及びコンタクトを充填して銅配線導電体を形成する方法を提供すること。

【解決手段】能動及び受動素子を配線連結するために、銅配線導電体を形成する方法が開示される。ここに開示された発明は、触媒と共に銅を配線導電体物質の原料とするCVD工程を含む。トレンチ、ビアホール、コンタクト、広い受動素子だけでなく電力素子と電力線のための大きいトレンチとホールを充填する配線方法がここに開示されて提供される。ここに提示された他の方法は、狭くて深いトレンチと小径で深いホールのような小さな陥没部を触媒を使用した銅CVDで充填する方法であり、湿式または乾式エッチバックまたは高温プラズマエッチバック工程により後続工程段階に備えて除去されるように扁平な最上部の表面に非常に薄い薄膜を形成する方法である。

(もっと読む)

触媒及び化学気相蒸着法を用いて銅配線及び薄膜を形成する方法

【課題】触媒を使用した銅CVD方法として、ピンチ−オフやボイドの発生なしにトレンチ、ビアホール及びコンタクトを充填して銅配線導電体を形成する方法を提供すること。

【解決手段】能動及び受動素子を配線連結するために、銅配線導電体を形成する方法が開示される。ここに開示された発明は、触媒と共に銅を配線導電体物質の原料とするCVD工程を含む。トレンチ、ビアホール、コンタクト、広い受動素子だけでなく電力素子と電力線のための大きいトレンチとホールを充填する配線方法がここに開示されて提供される。ここに提示された他の方法は、狭くて深いトレンチと小径で深いホールのような小さな陥没部を触媒を使用した銅CVDで充填する方法であり、湿式または乾式エッチバックまたは高温プラズマエッチバック工程により後続工程段階に備えて除去されるように扁平な最上部の表面に非常に薄い薄膜を形成する方法である。

(もっと読む)

基板処理装置,基板処理方法,プログラム,プログラムを記録した記録媒体

【課題】下地との界面がより平坦(フラット)で均一なTiシリサイド膜を形成することができ,これにより一層低抵抗なコンタクトを形成することがきる。

【解決手段】基板処理装置100は,処理室104A〜104Dに共通に連結される第1共通搬送室102と,処理室104E,104Fに共通に連結される第2共通搬送室120とを備える。各処理室104E,104F,104A,104C,104Bはそれぞれ,Siウエハ上の自然酸化膜を含む異物とガス成分とを化学反応させて生成物を生成するCOR処理室,Siウエハ上に生成された生成物を熱処理により除去するPHT処理室,SiウエハのSi表面上にTi膜を成膜するTi膜成膜処理室,Ti膜と下地との間で珪化反応を起させてTiシリサイド膜を形成するシリサイド形成処理室,Tiシリサイド膜上にTiN膜を成膜するTiN膜成膜処理室として構成した。

(もっと読む)

特徴画成部を形成する方法

【課題】 基板の表面上に特徴画成部を形成する改良された方法を提供する。

【解決手段】 基板の表面にネガティブマスク材料を堆積し、そのネガティブマスク材料を基板表面へとエッチングしてネガティブマスク特徴画成部を形成し、ネガティブマスク特徴画成部に耐エッチング材料を堆積し、その耐エッチング材料を研磨してネガティブマスク材料を露出させ、ネガティブマスク材料をエッチングして耐エッチング材料に特徴画成部を形成することにより、基板を処理する方法が提供される。

(もっと読む)

半導体装置

【課題】導電プラグの酸化を抑止し、コンタクト抵抗の安定化された信頼性の高い半導体装置を実現する。

【解決手段】下部電極101と上部電極103とで強誘電体膜102を挟持してなる強誘電体キャパシタ構造100と、導電プラグ110(プラグを構成する導電物は例えばタングステン(W))との間に、シリサイド膜111を形成する。ここでは、導電プラグ110の下地膜をシリサイド膜111とする場合を例示する。

(もっと読む)

121 - 140 / 189

[ Back to top ]