Fターム[5F033JJ27]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | シリサイド (585) | 高融点金属のシリサイド (433) | TiSi (189)

Fターム[5F033JJ27]に分類される特許

141 - 160 / 189

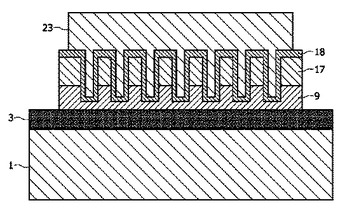

改良された接触パッドを有する半導体デバイスとその製造方法

半導体デバイスおよびその製造方法が開示される。このデバイスは、1以上の導電性ゲート(11)を具えた活性半導体領域(1A)と、前記活性半導体領域(1A)の周辺に位置し主としてフィールド酸化領域(3)よりなるコンタクト領域(1B)とを具える。周辺コンタクト領域(1B)上、および、少なくとも一部の活性半導体領域(1A)上に、導電性ゲート(11)の間にコンタクト窓(19a)が形成された絶縁層(17)が積層される。絶縁層(17)上に積層された金属コンタクトパッド(23)が、前記コンタクト領域(1B)に設けられる。この金属コンタクトパッド(23)は、導電性のパターンを介して、絶縁層(17)の下に埋設されているコンタクトストリップ(15)に接触し、この導電性のパターンは、コンタクト窓(19b)充填物の複数個で構成されており、コンタクトパッド(23)の実質的な領域を横切って延びている。このパターンは平行な一連のトレンチに充填されたもので構成されているのが好ましい。  (もっと読む)

(もっと読む)

有機絶縁膜及びその製造方法及び有機絶縁膜を用いた半導体装置及びその製造方法

【課題】現在、一般的に検討されているSiCやSiCNは比誘電率が4.5から5程度、SiOCは2.8から3.0程度である。デバイスの縮小化により、配線サイズと配線間隔の微細化が更に進むと、比誘電率の更なる低減が求められている。また、SiOCとSiCN及び、SiCとのエッチング選択比がちいさいために、エッチングストッパ膜として、SiCN及びSiCを用いた場合、金属配線層の表面が、フォトレジストを除去する際に酸化し、接続抵抗が高くなるという問題がある。

【解決手段】少なくともC/Si比が5以上で、且つ、分子量が100以上の有機シランを原料として形成された、SiOCH、SiCNH及び、SiCHからなる有機絶縁膜、及び、該有機絶縁膜を用いた半導体装置、特に、溝構造を有する半導体装置に関するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】従来の半導体装置は、コンタクトホールの底部に段差部があり、これにより、コンタクトホール内で配線金属が分断してしまうという問題があった。

【解決手段】本発明の半導体装置は、コンタクトホールの底部にもっとも近い部分の層間膜の開口径より半導体層の開口径が大きく、その開口径の差で生じる層間膜と半導体層との間の段差部を絶縁膜で埋める構成を有している。このような構成によって、コンタクトホールの内壁の縦端面と絶縁膜の表面とが段差のない連続したなめらかな曲面を形成し、コンタクトホール内での配線金属の分断を防止する。

(もっと読む)

半導体素子の金属配線およびその製造方法

【課題】銅配線のベリア金属層の物質としてCVD TiSiNを用いて65nm以下の半導体素子にも適用できるようにした半導体素子の金属配線およびその製造方法を提供する。

【解決手段】本発明に係る半導体素子の金属配線は、半導体素子が形成された半導体基板と、前記半導体素子に相応する部分にコンタクトホールを有し、前記半導体基板に形成される絶縁膜と、前記コンタクトホール内に形成されるTiSiNベリア金属層と、前記TiSiNベリア金属層上に形成される銅配線とを含んで構成される。

(もっと読む)

半導体素子の製造方法

【課題】コンタクトホールから露出する導電層間を連結するコンタクトパッドの形成の際、金属シリサイド層を用いて電気的な抵抗を低減する半導体素子の製造方法を提供する。

【解決手段】半導体基板上に第1導電層、第1層間絶縁膜、第2導電層、及び第2層間絶縁膜を順次形成し、マスク膜を食刻マスクとして用いて第2層間絶縁膜、第2導電層、及び第1層間絶縁膜を順次除去して第1導電層が露出するコンタクトホールを形成する段階と、コンタクトホールの側壁に露出した第2導電層を選択的に食刻してコンタクトホールの側壁に露出する第1層間絶縁膜と第2層間絶縁膜との間にリセスを形成する段階と、コンタクトホールの底部または側壁の少なくともいずれか一方に所定厚さの第3導電層を形成するとともに、リセスを埋める金属シリサイド層を形成する段階と、金属シリサイド層が形成された後、コンタクトホールを埋める第4導電層を形成する段階と、を含む。

(もっと読む)

半導体装置

【課題】 埋込銅配線を有する半導体装置の信頼性を向上させる。

【解決手段】 絶縁膜14,15に配線溝を形成し、その配線溝の底面および側面上を含む絶縁膜15上に導電性バリア膜18と銅の主導体膜19を形成し、CMP法により不要な部分を除去して配線20を形成する。そして、主導体膜19上にタングステンからなる金属キャップ膜22を選択成長させてから、配線20を埋込んだ絶縁膜15上に絶縁膜23〜26を形成し、ビア30が金属キャップ膜22を貫通して主導体膜19を露出するようにビア30及び配線溝31を形成し、ビア30の底部で露出した主導体膜19上にタングステンからなる金属キャップ膜32を選択成長させた後に、ビア30および配線溝31の内部を含む絶縁膜26上に導電性バリア膜33と銅の主導体膜34を形成し、CMP法により不要な部分を除去して配線35を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 1.5以上の高アスペクト比である微細ホールに対しても、金属配線膜を埋め込むことができるように、ホールへの金属配線膜の埋め込み性を従来よりも向上させる。

【解決手段】 TiN膜の成膜工程63で、スパッタにより、ホールの内壁に沿ってTiN膜を成膜する。このとき、成膜温度を、従来よりも低温の150℃とすることで、アモルファス構造のTiN膜を形成する。その後、スパッタ工程64、65で、アモルファス構造のTiN膜の表面上にAl合金膜を形成することで、TiN膜を下地とした状態で、Al合金膜をコンタクトホールの内部に埋め込む。このように、Al合金膜の下地となるTiN膜をアモルファス構造にすることで、TiN膜の表面エネルギーを大きくし、TiN膜のAl合金膜に対する濡れ性を従来よりも向上させることができ、ホールへのAl合金膜の埋め込み性を従来よりも向上させることができる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】配線と配線を接続する接続部のバリア膜の構造を最適化し、エレクトロマイグレーション特性を向上させる。

【解決手段】半導体基板上の第1層配線M1上に形成された層間絶縁膜TH2中に配線溝HM2およびコンタクトホールC2を形成した後、これらの内部にバリア膜PM2aを、コンタクトホールC2の底部の全周に渡ってコンタクトホールC2の底部の中央部から側壁に向かってその膜厚が増加するよう形成し、このバリア膜PM2a上に銅膜(PM2b、PM2c)を形成した後、CMP法により研磨することにより第2層配線M2と接続部(プラグ)P2を形成する。その結果、接続部(プラグ)P2を介して第2層配線M2から第1層配線M1へ流れる電流の幾何学的な最短経路と、電気的に抵抗が最小となるバリア膜PM2aの薄い部分が一致せず、電流経路を分散することができ、電子の集中を起こりにくくできる。

(もっと読む)

誘電体メモリ及びその製造方法

【課題】 COB構造を有する誘電体メモリにおいて、スタックコンタクトにおける下部コンタクトプラグのコンタクト抵抗の安定化を図る。

【解決手段】 不純物拡散層104に接続する第1のコンタクトプラグ108の上方に形成された配線109を覆う第2の絶縁膜110を形成する工程と、第2の絶縁膜110上に第3の絶縁膜111を形成する工程と、第3の絶縁膜111上に第1の水素バリア膜112を形成する工程と、第1の水素バリア膜112上にキャパシタ118を形成する工程と、第1の水素バリア膜112における第1のコンタクトプラグ108の上方に存在している部分を選択的に除去した後、キャパシタ108に対して熱処理を行う工程とを備える。これにより、熱処理時に、第1のコンタクトプラグ108の上面が第2の絶縁膜110及び第3の絶縁膜111によって覆われているので、第1のコンタクトプラグ108の酸化及び消失を防止することができる。

(もっと読む)

半導体装置およびその作製方法

【課題】薄膜トランジスタにおいて、ソース/ドレイン領域へのコンタクトの方法を改良することにより、配線抵抗を減らす。

【解決手段】ガラス基板上に第1の絶縁膜、島状の結晶性珪素膜、ゲイト絶縁層、ゲイト電極、第1の配線、ゲイト電極及び第2の絶縁膜を形成し、第2の絶縁膜及びゲイト絶縁層をエッチングしてゲイト電極及び第1の配線の側面に側壁を形成するとともに、島状の結晶性珪素膜のソース領域及びドレイン領域を露出し、ゲイト電極、第1の配線、側壁、島状の結晶性珪素膜及び第1の絶縁膜上に金属層を形成し、ソース領域及びドレイン領域と、金属層とを反応させて島状の結晶性珪素膜の側面から上面にわたって密着したシリサイド層を形成し、金属層をエッチングして、ソース領域又はドレイン領域の一方のシリサイド層と第1の配線とを接合する第2の配線を形成する。

(もっと読む)

成膜方法およびコンピュータにより読み取り可能な記憶媒体

【課題】CVD法において、500℃未満の低い成膜温度でも異常成長のない良質の金属窒化膜を成膜することが可能な成膜方法を提供すること。

【解決手段】成膜温度に加熱された被処理基板に金属化合物ガスおよび窒素含有還元ガスを供給してCVDにより被処理基板上に金属窒化膜を直接堆積させる期間を含む第1段階と、同様に金属化合物ガスおよび窒素含有還元ガスを供給してCVDにより前記第1段階で堆積された初期の金属窒化膜の上にさらに金属窒化膜を堆積させて所定の膜厚とする第2段階とを含み、前記第1段階および前記第2段階ともに、前記金属化合物ガスおよび窒素含有還元ガスを供給する第1ステップと、前記金属化合物ガスを停止して前記窒素含有還元ガスを供給する第2ステップとからなるサイクルを1サイクル以上繰り返す。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置に熱処理を施したとしてもコンタクトプラグの周囲に形成された窒化膜に生じる熱変形を抑え、半導体装置の電気的特性を維持することができる半導体装置の製造方法を提供する。

【解決手段】 工程14では、シリコン基板12上の層間絶縁膜14にコンタクトホール15aを形成する。工程15では、シリコン基板12におけるコンタクトホール15aの下側に不純物31を導入する。工程16では、導入した不純物31を、例えば、800℃の温度の熱処理によって拡散してドレイン電極23の領域を広げる。工程17及び18では、コンタクトホール15aの内面にチタン膜28及び窒化チタン膜29を形成する。工程19では、半導体装置11に、例えば、520℃の温度の熱処理を施して、シリコン基板12におけるバリアメタル26とシリコン基板12との間にシリサイド膜16を形成する。

(もっと読む)

キャパシタおよびその製造方法

【課題】

ギガビット級DRAM用キャパシタの誘電体に用いる酸化タンタルの高誘電率化のために結晶化すると、結晶粒界が膜厚方向に貫通してリーク電流のパスが生成され電荷保持特性が劣化する。リーク電流の増大を回避し、酸化タンタルを含む誘電体のEOTが2nm以下となる、MIM構造でスタックトレンチ型のキャパシタおよびその製造方法を提供する。

【解決手段】

酸化タンタルを原子層蒸着法で形成し、ポスト酸化アニールを不要とし、金属下部電極の酸化剥離を防止する。酸化タンタルの結晶化が容易な4〜4.8nmの膜厚で形成し非酸化性雰囲気で結晶化する。その上に厚さ0.5〜1.5nmの結晶分断層を形成し、さらに酸化タンタルおよび結晶分断層を積層して多層化する。これにより、酸化タンタル積層時のエピタキシャル成長を抑止して結晶粒界の膜方向貫通を防止する。

(もっと読む)

表示装置、及び表示装置の作製方法

【課題】信頼性の高い表示装置を低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【解決手段】一導電型の不純物領域を含む半導体層と、半導体層上にゲート絶縁層と、ゲート電極層と、一導電型の不純物領域と接する配線層と、ゲート絶縁層上に設けられ、配線層と接する導電層と、導電層と接する第1の電極層と、第1の電極層上に電界発光層と、第2の電極層とを有し、配線層は導電層を介して第1の電極層と電気的に接続している。

(もっと読む)

キャパシタおよびその製造方法

【課題】

DRAMに用いられる王冠型構造のキャパシタにおいて、厚い絶縁膜に形成された深孔の内壁に下部電極を形成した後、下部電極外壁周囲の絶縁膜を溶液エッチングすると、機械的強度が減少するため、下部電極が倒壊しペアビット不良が発生する問題を回避する。

【解決手段】

王冠型もしくは円柱状からなる内側下部電極と王冠型の外側下部電極とからなる2重下部電極構造とし、導電プラグが形成された層間絶縁膜上に窒化シリコン膜を設け、内側の電極底部は窒化シリコン膜を貫通して導電プラグと接続し、外側の電極底部は窒化シリコン膜の表面に張出すように形成する。これにより下部電極自身が窒化シリコンの側壁に加えて窒化シリコンの上面にも接している構造となるので横方向に加わる力に対して機械的強度を向上させることができ、倒壊を防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】良好な抵抗値を示すコンタクトプラグを備えた半導体装置の製造方法を提供する

こと。

【解決手段】

コンタクトプラグを備えた半導体装置の製造方法であって、半導体シリコン基板表面に設けられた高濃度N導電型拡散層の表面部分および層間絶縁層により形成されたコンタクトホールを通じて、加速エネルギーを30〜120keVの範囲とし、注入量を1.0×1013〜5.0×1014/cm2の範囲としてインジウムイオンを注入するこにより、前記コンタクトホール下部の前記高濃度N導電型拡散層の表面部分にインジウム含有層を形成することを特徴とする半導体装置の製造方法。

(もっと読む)

成膜方法、前処理方法および成膜システム

【課題】 混載デバイスに対しても、前処理によって接合部位の自然酸化膜を確実に除去し、抵抗上昇を生じさせない成膜方法を提供する。

【解決手段】 被処理体に露出したSi含有部表面に金属含有膜を成膜する成膜方法は、Si含有部分の表面を、高周波を用いたプラズマにより物理的に処理する物理的表面処理工程と、プラズマによる処理が施されたSi含有部分の表面を反応性ガスにより化学的に処理する化学的表面処理工程と、化学的表面処理が施されたSi含有部分上に金属含有膜を成膜する成膜工程と、を具備する。

(もっと読む)

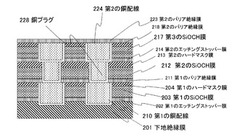

超小型電子相互接続構造の多層キャップ障壁

【課題】超小型電子相互接続構造の多層キャップ障壁を提供すること。

【解決手段】本明細書には、少なくとも1つの低kサブレイヤと少なくとも1つの空気障壁サブレイヤとを有する低k多層誘電拡散障壁層を有する構造が記載される。多層誘電拡散障壁層は金属の拡散に対する障壁であり、かつ空気の透過に対する障壁である。この構造の生成に関連した方法および組成物も記載される。これらの低k多層誘電拡散障壁層を利用する利点は、導電性金属フィーチャ間のキャパシタンスの低下によるチップ性能の増大、および多層誘電拡散障壁層が空気を通さず金属拡散を防ぐことによる信頼性の増大である。  (もっと読む)

(もっと読む)

半導体装置

【課題】電極構造下方のプラグの酸化を抑制する半導体装置を提供する。

【解決手段】半導体基板(S)と、この半導体基板に形成されたトランジスタの活性領域(107)に接続した導電性プラグ(118)と、この導電性プラグの底面部及び側面部に被覆する金属シリサイド膜(117)と、前記導電性プラグ上に形成された電極構造(200)と、を備えている。

(もっと読む)

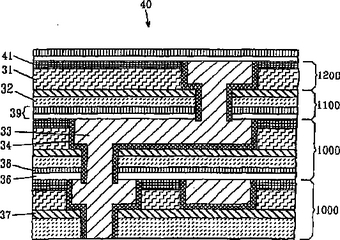

半導体装置及びその製造方法

【課題】 ビアプラグとCu配線層間におけるボイドの発生を抑制し、配線層相互間の電気的接続を良好にし得る半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板11と、半導体基板11上に第1の層間絶縁膜12を介して形成され、Cuを主材料とする第1の配線層15と、第1の層間絶縁膜12及び第1の配線層15上に第2の層間絶縁膜21を介して形成された第2の配線層25と、第2の層間絶縁膜21を貫通して形成され、第1の配線層15と第2の配線層25間を電気接続するビアプラグ26とを有し、第1の配線層15に存在する複数のCuの結晶粒界の内、ビアプラグ26の真下に存在する結晶粒界(51の位置)に選択的に、Cuとは異なる第1の材料を含有する。

(もっと読む)

141 - 160 / 189

[ Back to top ]