Fターム[5F033KK01]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 半導体基板 (2,232)

Fターム[5F033KK01]に分類される特許

41 - 60 / 2,232

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

半導体装置

【課題】バイアスに依存した抵抗値の変化をさらに低減できるようにした半導体装置を提供する。

【解決手段】N型シリコン層3と、N型シリコン層3上に形成されたP型拡散抵抗7と、P型拡散抵抗7上に形成されたシリコン酸化膜11と、シリコン酸化膜11を貫いてP型拡散抵抗7の一方の端部7aに接続され、一方の端部7aに高電位を印加するための高電位用電極15と、シリコン酸化膜11を貫いてP型拡散抵抗7の他方の端部7bに接続され、他方の端部7bに低電位を印加するための低電位用電極17と、を備える。高電位用電極15及び低電位用電極17はそれぞれシリコン酸化膜11上に延設されると共に、シリコン酸化膜11上において高電位用電極15と低電位用電極17との間にはスリット21が設けられている。このスリット21は、P型拡散抵抗7の一方の端部7aと他方の端部7bとの間の中間位置23よりも一方の端部7aに近い側に位置する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極を効率良く形成する。

【解決手段】シリコン基板1にビアホール25を形成し、絶縁膜22を形成した後、ビアホール25に低誘電率膜31を埋め込む。ビアホール25内の低誘電率膜31の膜厚を異方性ドライエッチングによって所望の値に減少させる。この異方性ドライエッチングによって、絶縁膜22上の低誘電率膜31が除去される。続いて、ビアホール25内に導電材を埋め込み、トランジスタT1,T2上に多層配線を形成する。この後、シリコン基板1の裏面側を研磨して導電材を露出させると、貫通電極が形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の反りを抑制し、且つ、その反りの経時変化を抑制する。

【解決手段】半導体装置は、基板と、基板上に形成された多層配線層と、を有し、多層配線層は、配線と、配線を覆う層間絶縁膜と、をそれぞれ有する複数層の配線層を有する。少なくとも何れか1つの層間絶縁膜(例えば、層間絶縁膜27、30)は、第1絶縁膜41と第2絶縁膜42とを有する。第1絶縁膜41は、基板を第1方向(例えば下に凸)に反らせる応力を基板に与える。第2絶縁膜42は、第1絶縁膜41よりも表層側に形成され、第1絶縁膜41よりも吸湿性が低く、基板を第1方向に対する反対方向(例えば上に凸)に反らせる応力を基板に与える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】シールリングの内側領域生じたクラックを低コストで検出することができる半導体装置を提供する。

【解決手段】図2に示すように、本実施形態に係る半導体装置は、多層配線層と、内部回路領域3と、多層配線層に形成され、内部回路領域3を囲うシールリング220と、平面視で内部回路領域3とシールリング220とに挟まれた領域に設けられているTEG200と、を含んでいる。TEG200は、多層配線層の少なくとも2層それぞれに設けられ、互いに接続する導体パターン7と、P型ウェル13と、N型ウェル14とによって構成されている。P型ウェル13とN型ウェル14は、平面視で交互に互いに接続された状態で配置されており、P型ウェル13とN型ウェル14のいずれか一つに導体パターン7が接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス条件の見直しを最小限に抑制しつつ電気的特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、半導体構造11の上面領域に形成された島状の絶縁膜20と、絶縁膜20の上面領域に配列された複数の凸状絶縁部23と、これら凸状絶縁部23と絶縁膜20とを被覆する層間絶縁膜26とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の外部端子に加わる外力により外部端子の下方の絶縁膜にクラックが生じるのを抑制または防止する。

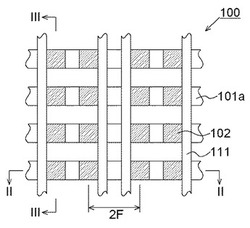

【解決手段】半導体基板1の主面上には複数の配線層が形成されている。この複数の配線層のうちの最上の配線層MHの直下の第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成しない。上記第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下以外の領域には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成する。

(もっと読む)

半導体磁気記憶装置

【課題】磁気記憶素子を構成する層を、周辺回路部内で有効に活用する。

【解決手段】実施形態によれば、半導体磁気記憶装置は、セルトランジスタを含むセル部と、周辺トランジスタを含む周辺回路部とが形成された半導体基板を備える。さらに、前記装置は、前記セル部内に配置され、下部電極と、前記下部電極上に形成された電極間層と、前記電極間層上に形成された上部電極とを含む磁気記憶素子を備える。さらに、前記装置は、前記周辺回路部内に配置され、前記下部電極を形成している第1の層と、前記電極間層を形成している第2の層と、前記上部電極を形成している第3の層とを含む構造体を備える。さらに、前記装置は、前記第1の層に電気的に接続された第1及び第2のプラグを備える。さらに、前記第1の層は、前記第1のプラグと前記第2のプラグを電気的に接続する配線として機能する。

(もっと読む)

半導体装置およびその製造方法

【課題】実施形態は、一括して形成することが可能なメモリセルを有し、その直下に制御回路を設けた構成を実現する半導体装置およびその製造方法を提供する。

【解決手段】実施形態は、基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置の製造方法であって、前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層に、前記p形半導体領域に連通する第1のコンタクトホールを形成する工程と、前記第1のコンタクトホールの内部に、前記p形半導体領域に接したコンタクトプラグを形成する工程と、を備える。さらに、前記n形半導体領域に連通する第2のコンタクトホールを前記絶縁層に形成する工程と、前記コンタクトプラグと、前記第2のコンタクトホールの内部に露出した前記n形半導体領域と、に接する配線を形成する工程と、を備える。

(もっと読む)

半導体装置

【課題】Low−k膜を層間絶縁膜として用いた半導体装置であっても、ダイシング時に発生するクラックがシールリング部へ伝播するのを抑制し、半導体装置の信頼性を向上する技術を提供する。

【解決手段】ダイシング領域側の各層にダミービア125,135,145,155,165を形成する。ダミービア125,135,145,155,165は上面からみて、縦横に等間隔に配置、あるいは千鳥配置されるように形成する。ダイシング時にクラックが発生しても、ダミービア125,135,145,155,165によって、クラックがシールリング部190にまで伝播するのを抑制することができる。その結果、回路形成領域の吸湿耐性を向上させ、信頼性の劣化を防止することができる。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】配線を形成したときに電極と配線との密着性を向上できる炭化珪素半導体装置の製造方法を提供する。

【解決手段】第1の面と、第1の面と反対の第2の面とを有する炭化珪素半導体層110が準備される。炭化珪素半導体層110の第2の面を部分的に覆う金属層と、炭化珪素半導体層110の第2の面を部分的に覆う熱酸化膜130とが形成される。金属層を熱処理することにより電極150が形成される。金属層を形成する工程は、金属層を熱処理する温度において炭素よりもシリコンとの反応性が高い材料を用いて行われる。電極150を形成する工程において電極150の表面上に炭素が偏析する。電極150の表面および熱酸化膜130の表面の両方において、炭素を除去可能なエッチングが行われる。

(もっと読む)

半導体装置の製造方法

【課題】アライメント光によるアライメントマークの検出感度を向上させて、低コストで貫通孔の位置合わせを行う。アライメントマークの誤検出を防ぐ。また、アライメントマーク検出時のアライメント光の露光マージンを大きくして、微細化に対応可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板の非有効ショット領域において、半導体基板の主面又は主面よりも上方にアライメントマークを形成する。半導体基板の裏面の方から、アライメントマークが形成された位置に対応する開口を形成する。半導体基板内に形成されている半導体装置の構成パターンと露光用マスクパターンとの位置合わせをして、有効ショット領域の半導体基板内に貫通孔を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】低抵抗の微細配線構造を有する半導体装置を提供する。

【解決手段】第1配線420は、半導体基板100上に設けられている。第1ビア440は、第1配線420上に設けられている。また、第1ビア440の底面は、第1配線420に接している。第1絶縁層330は、半導体基板100上に設けられ、少なくとも第1配線420の上面および第1ビア440の側面と接している。第1配線420および第1ビア440のうち各々の側面の少なくとも一部は、各々の金属の結晶粒を分断している。

(もっと読む)

半導体集積回路装置

【課題】銅埋め込み配線を主要な配線層とする半導体集積回路装置に於いても、通常、ワイヤボンディング特性を確保するために、最上層配線層をアルミニウム系パッド層とすることが多い。このアルミニウム系パッド層は、一般に、配線層(電源配線、信号配線等の一般相互接続配線)としても使用されている。しかし、このような一般相互接続配線は、配線長が比較的長いためアンテナ効果により、プラズマ処理時にデバイスにダメージが入り易い等のデメリットがある。

【解決手段】本願発明は、メタル多層配線系が、下層の埋め込み型多層配線層と上層の非埋め込み型アルミニウム系パッドメタル層を有する半導体集積回路装置に於いて、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に電源リング配線を有しないものである。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、製造コストを低減し、さらにゲート電極およびゲートコンタクトの抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、ゲート電極7の少なくとも上層は、第2金属シリサイド膜としてのWSix膜72からなり、第1金属シリサイド膜としてのNiSi2膜18に含まれる第1金属(Ni)とシリコンとの結合エネルギーが、WSix膜72に含まれる第2金属(W)とのシリコンとの結合エネルギーよりも小さく、WSix膜72の組成MSix(Mは第2金属を示す)において、xが1.5以上2.0未満であることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の素子形成領域へのクラックなどの伝播を確実に防止する。

【解決手段】ウェハ1上の素子形成領域を覆うガード領域4の外側に、n型拡散層15を形成する。n型拡散層15の上には、導電性リング33,48,58を形成する。最上層の導電性リング48の上に、導電層65を形成する。導電層65の端面65Sは、導電性リング58の端面58Sから距離L1だけ内側に形成し、導電性リング58の上面の一部を露出させる。この後、半導体基板をアミン系薬液に浸すと、n型拡散層15と導電層65の間の導電性プラグ33,48,48の導電性材料を溶出し、スリットが形成される。

(もっと読む)

電界効果トランジスタ

【課題】ゲート電極とソース電極との間に印加される電圧がソース電極パッドの電気抵抗による電圧降下で低下することを防止でき、安定した動作を実現できる電界効果トランジスタを提供する。

【解決手段】このGaN HFETによれば、ボンディング部16Bの第2のパッド部16B‐2は、電極接続部16Aが含有する複数の接続部分19のうちの第2の方向(ソース電極12とドレイン電極11が対向している方向)の一端に配置された接続部分19の上記第2の方向の外端を電極延在方向へ延長した仮想延長線L1に関して第1のパッド部16B‐1とは反対側に位置している。第2のパッド部16B‐2に接続された第2のソース配線24のボンディング箇所の第2の方向の位置を電極接続部16Aのソース電極12との接続部分19の第2の方向の位置と重ならないようにして、ソース電極12からの電流が第2のソース配線24に流れにくくできる。

(もっと読む)

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

41 - 60 / 2,232

[ Back to top ]