Fターム[5F033KK01]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 半導体基板 (2,232)

Fターム[5F033KK01]に分類される特許

61 - 80 / 2,232

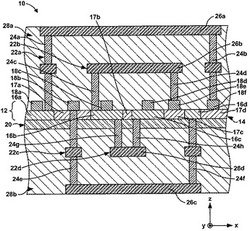

表側および裏側の電気インターコネクトを含む集積回路

【課題】シリコン・オン・インシュレータ(SOI)基板の層内に配置された複数のトランジスタ、および層の第1の側の上に配置されたベース酸化物層を含むSOI基板を備えた集積回路を提供すること。

【解決手段】集積回路はまた、層の第1の側に形成された第1のインターコネクトを含むことができ、第1のインターコネクトが、複数のトランジスタのうちの第1のトランジスタと複数のトランジスタのうちの第2のトランジスタとを電気的に接続することができる。加えて、集積回路は、層の第1の側とは反対の層の第2の側に形成された第2のインターコネクトを含み、第2のインターコネクトが、複数のトランジスタのうちの第3のトランジスタと複数のトランジスタのうちの第4のトランジスタとを電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、小型化を図ることが可能になると共に、絶縁リングで囲まれた貫通電極を狭ピッチで配置することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】回路素子層5が形成される表面1a、及び裏面1bを有する半導体基板1と、半導体基板1を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が広くなる貫通電極7と、貫通電極7を囲むように半導体基板を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が狭くなる第1の絶縁リング3と、を有し、半導体基板1の厚さ方向Aにおいて、第1の絶縁リング3の少なくとも一部と対向するように貫通電極7を配置する。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体ウェハ及びその製造方法

【課題】スクライブ線領域におけるダミーパターンが影響して配線形成の際に露光時のアライメント波形検出精度を低下させるおそれがあった。

【解決手段】複数の素子形成領域と、素子形成領域を相互に区画するスクライブ線領域と、素子形成領域において半導体基板上に配置された複数のパターンと、スクライブ線領域において半導体基板上に配置されるとともに、パターンと同様な構成の複数のダミーパターンと、パターン及びダミーパターンを含む半導体基板上に形成されるとともに、上面が平坦化された層間絶縁膜と、スクライブ線領域における層間絶縁膜に形成されるとともに、ダミーパターンと重ならない領域にて半導体基板に通じないように形成された穴状のアクセサリパターンと、を備える。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を製造することはできないから、高抵抗の拡散抵抗は実現できなかった。

【解決手段】一組の薄膜構造体の対向する間隔に、サイドウォール形成用の絶縁膜を形成する際に生じる空隙を利用して露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を形成する。薄膜構造体を配線抵抗として利用すれば、これらを接続して設けることにより温度特性に優れる抵抗素子を構成することもできる。

(もっと読む)

半導体装置

【課題】パワー半導体素子において、周辺の電界強度を緩和する構造を小さな面積で実現する。

【解決手段】周辺領域Qにおいては、半導体層との間に周辺層間絶縁層(絶縁層)を介して複数の多結晶シリコン層70が、ソース電極30から端部ドレイン電極41の間にかけて設けられる。多結晶シリコン層70には、その長手方向が水平方向から傾斜した(傾斜角θ、0<θ<90°)傾斜部が設けられている。多結晶シリコン層70の傾斜部においては、p型領域71と、n型領域72とが長手方向に交互に多数形成されている。

(もっと読む)

成膜方法、これを含む半導体装置の製造方法、成膜装置、及び半導体装置

【課題】柱状形状を有し密に配列される電極の倒壊を防ぐことが可能な半導体装置を提供する。

【解決手段】電界効果トランジスタと、柱状形状を有するキャパシタとを有する半導体装置であって、前記電界トランジスタの不純物拡散領域と電気的に接続し、柱状形状を有する第1の電極と、前記第1の電極の少なくとも側面に形成される誘電体膜と、前記誘電体膜上に形成される第2の電極と、前記柱状形状を有する前記第1の電極の長手方向と交差する方向に延び、前記第2の電極の少なくとも一部を貫通して前記第1の電極を連結するホウ素添加窒化シリコン膜により形成される支持膜とを備える半導体装置により、上記の課題が達成される。

(もっと読む)

半導体ウェハ及び半導体装置の製造方法

【課題】第1の溝への絶縁膜の埋設性が向上させて、埋設不良を軽減する。アライメントマークにおける埋設不良個所での応力集中がもたらす基板へのクラックを軽減する。

【解決手段】基板の第1の主面に、第1の溝、および前記第1の主面に対向して見た形状が環状となりかつ前記第1の溝よりも深い第2の溝を形成する工程と、第1の溝と第2の溝とを埋め込むように絶縁膜を形成する工程と、絶縁膜を形成する工程の後、基板の第1の主面にフォトレジスト膜を形成する工程と、絶縁膜で埋め込まれた第1の溝の基板上での位置を基準として位置合わせした第1のパターンをフォトレジスト膜に転写する工程と、絶縁膜で埋め込まれた環状の第2の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】同一平面上に形成された2つの配線が互いにショートするのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置する縦型のゲート電極用ダミーピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央に位置するゲート電極用ダミーピラー(1a)へ給電するために第1の方向(X)へ延在して配置されたゲート給電配線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつゲート給電配線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

集積回路装置の作製方法

【課題】薄膜回路の下方に外部と接続するための電極を容易に形成できる薄膜回路部品の

構造及び薄膜回路部品の作製方法を提供することを課題とする。

【解決手段】第1の絶縁膜と、第1の絶縁膜の一方の面上に形成された薄膜回路と、薄膜

回路上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された電極と、電極上に形成

された樹脂膜とを有する積層物を形成し、積層物の第1の絶縁膜の他方の面側に、電極と

重なるように導電膜を形成し、導電膜にレーザーを照射する。

(もっと読む)

半導体装置

【課題】パッド下のクラックによるショート不良が抑制された半導体装置を提供する。

【解決手段】パッド開口部18aの下の層間絶縁膜16はコンタクト17で囲われているので、ワイヤボンディング時に生じたパッド開口部18aの下の層間絶縁膜16のクラックはコンタクト17の外周縁17aよりも外側に入らない。よって、クラックを通し、パッド開口部18aは、外周縁17aよりも外側のアルミやポリシリコンなどの金属膜や拡散層とショートしない。

(もっと読む)

窒化物半導体装置

【課題】ドレイン電極配線によって形成されるフィールドプレートに起因する電流コラプス現象への影響が抑制された窒化物半導体装置を提供する。

【解決手段】窒化物半導体からなる機能層20と、機能層20上に離間して配置されたソース電極3及びドレイン電極4と、ソース電極3とドレイン電極4間で機能層20上に配置されたゲート電極5と、機能層20上に配置された層間絶縁膜7と、層間絶縁膜7上に配置され、ドレイン電極4と電気的に接続されたドレイン電極配線41とを備える窒化物半導体装置であって、ゲート電極5とドレイン電極4間において、層間絶縁膜7を介してドレイン電極配線41が機能層20と対向する領域を有さない。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】超音波振動を利用したワイヤーボンディングの際に、p型オーミック電極がp型不純物拡散領域の面上から剥離することを防止する。

【解決手段】パッド電極7にボンディングワイヤー8を接合する際に、ボンディングツール100を用いて、ボンディングワイヤー8をパッド電極7に接触させた状態で、ボンディングワイヤー8に荷重を加えながら、p型オーミック電極5の長手方向に沿って超音波振動を印加する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、コンタクトプラグが形成されるセル部と、前記コンタクトプラグが形成されない周辺回路部とを平坦化できる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に最上部が第1の絶縁膜からなる配線層を形成する工程と、

前記半導体基板と前記配線層とを被う第2の絶縁膜を形成する工程と、前記第2の絶縁膜の所定の領域をエッチングし、前記配線層と前記半導体基板とを露出させる開口部を形成する工程と、前記開口部内と前記第2の絶縁膜上とに導電膜を形成する工程と、前記第1の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有し、前記第2の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有する条件で、前記第2の絶縁膜と前記導電膜とを前記第1の絶縁膜が露出するようCMP法で除去し、コンタクトプラグを形成する工程を有する半導体装置の製造方法。

(もっと読む)

半導体発光素子

【課題】メタル電極に設けられた延伸部の表面を覆う絶縁膜の剥離が抑制された半導体素子を提供する。

【解決手段】半導体からなる活性層に積層されたn型またはp型の半導体層と、該半導体層の上に配置され接続部および延伸部を有するメタル電極と、該メタル電極の該延伸部の上面および側面を少なくとも覆う絶縁膜と、を備え、該延伸部はメタル多層膜で形成され、該メタル多層膜は少なくとも2層の第1メタル層と、該第1メタル層と交互に積層された第2メタル層とを含み、かつ、その最上層は該第2メタル層のひとつであり、該メタル多層膜に含まれる該最上層の第2メタル層以外の第2メタル層の各々の端面が該延伸部の側面に露出して該絶縁膜と接しており、該第2メタル層を構成する第2メタル材料は該第1メタル層を構成する第1メタル材料よりも導電率は低いが該第1メタル材料よりも該絶縁膜との密着強度に優れている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】2枚の基板の貼り合わせによって電極間接合がなされた構成において、電極材料の拡散を防止しつつも貼り合わせ強度が確保され、これによって信頼性の向上が図られた三次元構造の半導体装置を提供する。

【解決手段】第1電極33、および第1電極33の拡散防止材料で構成され第1電極33の周囲を覆う第1絶縁膜35を含むと共に、第1電極33と第1絶縁膜35とで貼合せ面41が構成された第1基板2と、第1基板2に貼り合わせて設けられ、第1電極33に接合された第2電極67、および第2電極67の拡散防止材料で構成され第2電極67の周囲を覆う第2絶縁膜69を含むと共に、第2電極67と第2絶縁膜69とで第1基板2に対する貼合せ面71が構成された第2基板7とを備えた。

(もっと読む)

半導体装置

【課題】半導体チップのバンプ電極と実装基板の配線との接続信頼性を向上できる技術を提供する。特に、バンプ電極下の最上層配線層に配線を配置しても、バンプ電極の平坦性を確保してバンプ電極とガラス基板に形成されている配線との接続信頼性を向上できる技術を提供する。

【解決手段】バンプ電極BP1の非重複領域Y直下にある最上層配線層に電源配線や信号配線からなる配線L1と、ダミーパターンDPを形成する。ダミーパターンDPは、配線L1間のスペースを埋めるように配置され、配線L1とスペースによって最上層配線層に生じる凹凸を緩和する。さらに、最上層配線層を覆うように形成される表面保護膜に対してCMP法による平坦化処理を実施する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1のnMIS形成領域1Aにnチャネル型MISFETQnを、半導体基板1のpMIS形成領域1Bにpチャネル型MISFETQpを、それぞれ形成してから、nチャネル型MISFETQnおよびpチャネル型MISFETQpを覆うように引張応力の窒化シリコン膜5を形成し、nMIS形成領域1AおよびpMIS形成領域1Bの窒化シリコン膜5に紫外線照射処理を施す。その後、nMIS形成領域1Aの窒化シリコン膜5を覆いかつpMIS形成領域1Bの窒化シリコン膜5を露出するマスク層6aを形成してから、pMIS形成領域1Bの窒化シリコン膜5をプラズマ処理することで、pMIS形成領域1Bの窒化シリコン膜5の引張応力を緩和させる。

(もっと読む)

タングステン膜の成膜方法

【課題】工程が煩雑になることなく、埋め込み部分のボイドやシームを解消することができるタングステン膜の成膜方法を提供すること。

【解決手段】処理容器内において、ホールを有する基板にCVDによりタングステン膜を成膜してホール内にタングステンの埋め込み部を形成する工程と、同じ処理容器内にエッチングガスとしてClF3ガスまたはF2ガスを供給して埋め込み部の上部をエッチングし、開口を形成する工程と、開口が形成された埋め込み部を有する基板に対して同じ処理容器内において、CVDによりタングステン膜を成膜する工程とを有する。

(もっと読む)

61 - 80 / 2,232

[ Back to top ]