Fターム[5F033KK04]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 半導体(基板を除く) (1,188) | 多結晶Si (835)

Fターム[5F033KK04]に分類される特許

821 - 835 / 835

半導体装置

【課題】 バイポーラトランジスタにおける高利得化および低雑音化を同時に実現できる技術を提供する。

【解決手段】 ベースパッド31およびコレクタパッド32の下部にエミッタ(基準(接地)電位)と電気的に接続された配線24が設けられた基板シールド構造とすることにより、ベースパッド31およびコレクタパッド32と配線24との間では容量が設けられた構造として電力消費をなくし、基板1からの熱雑音は、配線24を介して基準(接地)電位へと逃がし、ベースパッド31およびコレクタパッド32へは届かないようにする。

(もっと読む)

半導体デバイスにおけるレベル内またはレベル間誘電体としての超低誘電率材料を製造するための改良した方法およびこれによって作成される電子デバイス

【課題】 誘電率が低く、熱安定性を有する誘電材料を提供する。

【解決手段】 プラズマ化学気相成長(PECVD)プロセスを利用して、平行板化学気相成長プロセスにおいて、Si、C、O、およびH原子を含む熱的に安定した超低誘電率膜を製造するための方法を開示する。更に、この方法によって作成された熱的に安定した超低誘電率材料の絶縁層を含む電子デバイスを開示する。熱的に安定した超低誘電率膜の製造を可能とするため、例えばジエトキシメチルシラン(DEMS)のようなシラン誘導体、および、例えばビシクロヘプタジエンおよび酸化シクロペンテンのような有機分子等、特定の前駆物質材料を用いる。

(もっと読む)

電気的接続部を形成する半導体処理方法及び半導体構造

無電解メッキを利用して、半導体基板に関連する電気的相互接続部を形成することができる。例えば、半導体基板は、その上に無電解メッキに適する表面を持つダミー構造を有するように、且つその上にダミー構造とほぼ同じ高さを有するディジット線を有するように形成することができる。層はダミー構造及びディジット線上に形成され、開口はその層を通ってダミー構造及びディジット線の上部表面まで形成される。続いて、導電性材料が開口内に無電解メッキされて、開口内に電気的接続部を形成することができる。ダミー構造まで延びる開口はキャパシタ電極を通ることができ、したがって、そのような開口内に形成される導電性材料を利用して、キャパシタ電極への電気的接続部を形成することができる。  (もっと読む)

(もっと読む)

低KのCVD材料の勾配堆積

【課題】 全体として低いkをもつILDを提供し、ILDに内在する接着性の欠陥に対する抵抗性だけでなく、ILDと基板との間の良好な接着性を提供する構造体と方法を提供すること。

【解決手段】 全般的に低い誘電率、半導体基板への良好な接着、及び熱循環によるクラッキングへの良好な抵抗性を有する、半導体デバイスのための誘電体層(12)である。誘電体層(12)は、誘電率の勾配をもつ誘電体層を提供するために、誘電体材料の堆積条件の連続的変化を含むプロセスによって生成される。

(もっと読む)

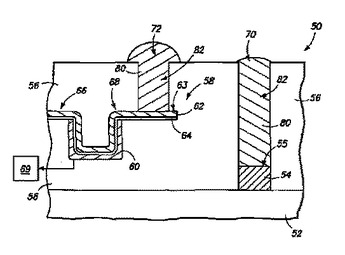

パッド下に素子を備える手法によるウェハの有効利用

半導体構造(20)のパッドエリア(21)下に能動素子(25)を組み込むことにより、シリコンエリアのより効率的な利用を可能とする。パッドエリア(21)は、上方に第1の金属層(23)を備えた基板(22)を含む。第2の金属層(26)は第1の金属層(23)の下とする。能動素子(25)は基板内であって、第2の金属層(26)の下に備えられる。誘導体層(24)は第1の金属層(26)と第2の金属層(23)とを分離する。誘導体層(24)内のビア(27)は第1の金属層(23)と第2の金属層(26)とを電気的に接続する。ビア(27)は能動素子(25)と接続する。隣接金属層(424、425、426)を第1の金属層(23)と第2の金属層(26)の間に配置してもよい。  (もっと読む)

(もっと読む)

減少されたコンタクト高さでのバイポーラ及びCMOSの集積回路構造体

【課題】 複数の高さのデバイスを含む集積回路構造体であって、このようなデバイスに形成されたコンタクトの高さを減少させるために保護層の高さを減少させた、改善された構造体を提供すること。

【解決手段】 単一の基板上に配置された複数の相補型金属酸化膜半導体(CMOS)トランジスタ及び複数の垂直バイポーラ・トランジスタを含む集積回路構造体のための方法及び構造体が開示される。垂直バイポーラ・トランジスタは、CMOSトランジスタより高さのあるデバイスである。この構造体においては、保護層が、基板の上に、及び、垂直バイポーラ・トランジスタとCMOSトランジスタとの間に配置される。配線層は保護層の上にある。垂直バイポーラ・トランジスタは、配線層と直接接触しており、CMOSトランジスタは保護層を通って延びるコンタクトによって配線層に接続されている。

(もっと読む)

低K誘電体を半導体製造プロセスにおいて形成する方法

低K誘電体複合層(26,28)は、低kバリア層(26)及びバリア層(26)上の低K誘電体層(28)により形成される。結果的に疎水性の上部表面を有するように堆積するバリア層(26)を酸素プラズマで処理して表面を疎水性から親水性に改質する。後続の水を用いた洗浄は、バリア層(26)の表面の改質に起因して歩留まりを低下させるバリア層(26)上の欠陥を取り除くために非常に効果的である。水を用いた洗浄の後、低K誘電体層(28)をバリア層(26)の表面上に形成して低K誘電体である複合層(26,28)を完成させる。  (もっと読む)

(もっと読む)

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

集積回路技術における超均一シリサイド

集積回路(100)の形成方法(900)およびその構造体が提供される。半導体基板(102)上にゲート誘電体(104)が形成され、半導体基板(102)上のゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(504/506)が形成される。ソース/ドレイン接合部(504/506)上に超均一シリサイド(604/608)が形成され、半導体基板(102)の上方に誘電体層(702)が堆積される。次いで、誘電体層(702)に、超均一シリサイド(604/608/606)へのコンタクトが形成される。  (もっと読む)

(もっと読む)

半導体装置

【課題】ESD 保護回路のサージ電流経路に使用される配線層に生じる熱を効率よく放熱でき、サージ電流経路に使用される配線層も保護する。

【解決手段】外部端子と内部回路との間の配線に接続され、外部端子に印加された過大な静電サージ入力から内部回路を保護する保護素子を有する入力保護回路と、入力保護回路に接続され、そのサージ電流経路に含まれる第1のメタル配線層25と、第1のメタル配線層に連なり、熱伝導性が良好な材質の配線を用いてなる放熱器20とを具備する。

(もっと読む)

表示装置及びその作製方法

【課題】 配線抵抗による電圧降下の影響や画素への信号の書き込み不良や階調不良などを防止し、より高画質のEL表示装置や液晶表示装置を代表とする表示装置を提供することを課題とする。

【解決手段】 本発明はEL表示装置や液晶表示装置を代表とする表示装置に用いられる電極や配線として、Cuを有する配線を設ける。また、該配線のCuを主成分とする導電膜は、マスクを用いたスパッタ法により形成する。このような構成により、電圧降下や信号のなまりを低減することができる。

(もっと読む)

配線構造

【課題】 高い周波数が印加され、数cm〜数10cmの長さを有する配線の抵抗を低減し、伝送される信号波形のなまりを低減する。

【解決手段】 高周波が印加される配線111は、層間絶縁膜107を介して、配線111の線方向にそって複数設けられたコンタクトホールにより配線106と電気的に並列接続している配線構造を採用する。その配線構造を周辺回路一体型アクティブマトリクス型液晶表示装置の周辺回路に用いることで、高周波信号が印加される配線において信号波形のなまりを低減できる。

(もっと読む)

配線構造、その製造方法、および表示装置

【課題】 配線構造と他の電極間のショートを防ぐ。

【解決手段】 SiO2により構成されたゲート絶縁膜12およびその上に積層され、SiNにより構成された層間絶縁膜13に、緩衝フッ酸を用いたエッチングによりコンタクトホールを形成する。このコンタクトホールに、高融点金属により構成された第1の保護金属層170と、高融点金属よりも抵抗の低い金属により構成された配線層172と、および高融点金属により構成され、ゲート絶縁膜12よりも厚く形成された第2の保護金属層174とがこの順で積層された電極53を形成する。

(もっと読む)

配線構造

【課題】 銅を配線材として用いても、微細な配線構造の形成が可能で、製造の工程数が少なく、低コスト化が可能な配線構造を提供する。

【解決手段】 半導体素子が形成された基板上に絶縁膜103が多層形成され、絶縁膜103に形成された配線溝およびビアホールに金属配線剤が充填されて、配線および接続プラグが形成された配線構造において、絶縁膜103のうち少なくとも一層が対電子線感光性を有する材料から形成されており、絶縁膜103の層間にはバリア絶縁膜104を有し、前記金属配線剤は銅を含むものである。

(もっと読む)

配線構造の製造方法

【課題】 銅を配線材として用いても、微細な配線構造の形成が可能で、製造の工程数が少なく、低コスト化が可能な配線構造の製造方法を提供する。

【解決手段】 配線構造の製造方法が、半導体素子201の上にWプラグ203(下層配線)が形成された基板上に、対電子線感光性を有する材料を含む第二層間絶縁膜204(絶縁膜)を形成する工程と、第二層間絶縁膜204に電子線を照射して、第二層間絶縁膜204を露光する工程と、第二層間絶縁膜204を現像して未露光部を除去し、配線溝および/またはビアホールおよび/またはコンタクトホールを形成する工程とを有する。

(もっと読む)

821 - 835 / 835

[ Back to top ]