Fターム[5F033KK11]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | Cu (2,449)

Fターム[5F033KK11]の下位に属するFターム

Cu合金 (304)

Fターム[5F033KK11]に分類される特許

61 - 80 / 2,145

半導体装置

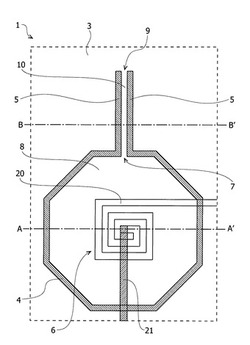

【課題】インダクタの下方の層間絶縁膜への水の浸入を抑制し、かつ、インダクタ性能の低下を抑制する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に設けられた層間絶縁膜と、前記層間絶縁膜の上部に設けられたインダクタと、前記半導体基板上に設けられ、前記インダクタの下方の前記層間絶縁膜を前記半導体基板の平面方向で囲む第一の金属壁と、前記半導体基板上に設けられ、前記第一の金属壁で囲まれた領域の外側の前記層間絶縁膜を前記半導体基板の平面方向で挟む一対の第二の金属壁と、を備え、前記第一の金属壁は、前記第一の金属壁の両端部を非接触の状態とする開口を有し、前記第二の金属壁は、前記第一の金属壁の両端部にそれぞれの一端を連結するとともに、前記第一の金属壁で囲まれた領域の外側の位置に開口を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体層を用いた素子を配線層間に形成し、かつ、ゲート電極の材料を、配線の材料以外の導電体にする。

【解決手段】第1配線層150の表層には、第1配線210が埋め込まれている。第1配線210上には、ゲート電極218が形成されている。ゲート電極218は、第1配線210に接続している。ゲート電極218は、第1配線210とは別工程で形成されている。このため、ゲート電極218を第1配線210とは別の材料で形成することができる。そしてゲート電極218上には、ゲート絶縁膜219及び半導体層220が形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】溝配線に生じるディッシングやエロージョンが配線構造に及ぼす影響を簡便に評価できるような半導体装置を提供する。

【解決手段】TEG200は、多層配線層中に設けられている。また、多層配線層中の第1絶縁膜に埋め込まれた下層溝配線1を備えている。TEG200は、第1絶縁膜80(図示せず)の表層に埋め込まれた下層導体パターン1と、第1絶縁膜80上及び下層導体パターン1上に形成された第2絶縁膜20と、それぞれが同一の下層導体パターン1に対向する複数の上層導体パターン10と、を有している。なお、上層導体パターン10は、第2絶縁膜20の表層に埋め込まれていても良いし、第2絶縁膜20上に形成されていても良い。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】酸化物半導体を使用する薄膜トランジスタの特性を向上させることができる薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】薄膜トランジスタ表示板を提供する。本発明の一実施形態に係る薄膜トランジスタ表示板は、基板の上に配置するゲート配線層、前記ゲート配線層の上に配置する酸化物半導体層、及び前記酸化物半導体層の上に配置して、前記ゲート配線層と交差するデータ配線層を含み、前記データ配線層は銅を含む主配線層、及び前記主配線層の上に配置して、銅合金を含むキャッピング層を含む。

(もっと読む)

回路基板、回路基板の製造方法、表示装置および電子機器

【課題】被蒸着膜を高精細なパターンで形成することが可能な蒸着用マスクを提供する。

【解決手段】蒸着用マスクは、1または複数の第1開口部を有する基板と、この基板の一主面側に設けられると共に、各第1開口部と対向して1または複数の第2開口部を有する高分子膜とを備える。蒸着の際には、蒸着材料が第1開口部および第2開口部を順に通過することにより、第2開口部に対応した所定のパターンで被蒸着膜が形成される。基板と高分子膜とを組み合わせて用いることにより、機械的強度を保持しつつも、金属膜のみで構成されている場合に比べ、第2開口部において微細かつ高精度な開口形状を実現できる。

(もっと読む)

金属付着物の除去方法、基板処理装置、および記録媒体

【課題】有機化合物ガスによる基板処理を清浄に行うことが可能となる金属付着物の除去方法および基板処理装置を提供する。

【解決手段】金属付着物の除去方法は、金属層が形成された被処理基板を処理する処理空間を内部に有する処理容器の内部に付着した金属付着物を昇華させるように、前記処理容器内部の温度と、前記処理空間の圧力とを、制御する。

(もっと読む)

エッチング方法及びこれに用いられるエッチング液、これを用いた半導体基板製品の製造方法

【課題】Tiを含む層を優先的に溶解する選択的なウエットエッチングを可能とし、しかもエッチング・アッシング等により生じる残渣をも効果的に洗浄除去することができるエッチング方法及びこれに用いるエッチング液、これを用いた半導体基板製品の製造方法を提供する。

【解決手段】

Tiを含む第1層と、Cu、SiO、SiN、SiOC、及びSiONの少なくとも1種を含む第2層とを有する半導体基板に特定のエッチング液を適用し、前記第1層を選択的にエッチングする方法であり、前記特定のエッチング液が、有機アミン化合物からなる塩基性化合物と酸化剤とを水性媒体中に含み、そのpHが7〜14であるエッチング方法。

(もっと読む)

半導体装置、電子機器、及び、半導体装置の製造方法

【課題】 より信頼性の高い接合界面を有する半導体装置を提供する。

【解決手段】 半導体装置1を、接合界面Sj側の表面に形成された第1金属膜16を有する第1半導体部10と、接合界面Sjで第1金属膜16と接合された第2金属膜26を有する第2半導体部20と、界面バリア部28とを備える構成とする。第2金属膜26の接合界面Sj側の表面面積は第1金属膜16の接合界面Sj側の表面面積より小さくする。そして、第1金属膜16の接合界面Sj側の面領域のうち第2金属膜26と接合しない面領域を含む領域に界面バリア部28を設ける。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】2枚の基板の貼り合わせによって電極間接合がなされた構成において、電極材料の拡散を防止しつつも貼り合わせ強度が確保され、これによって信頼性の向上が図られた三次元構造の半導体装置を提供する。

【解決手段】第1電極33、および第1電極33の拡散防止材料で構成され第1電極33の周囲を覆う第1絶縁膜35を含むと共に、第1電極33と第1絶縁膜35とで貼合せ面41が構成された第1基板2と、第1基板2に貼り合わせて設けられ、第1電極33に接合された第2電極67、および第2電極67の拡散防止材料で構成され第2電極67の周囲を覆う第2絶縁膜69を含むと共に、第2電極67と第2絶縁膜69とで第1基板2に対する貼合せ面71が構成された第2基板7とを備えた。

(もっと読む)

半導体装置の製造方法

【課題】生産性および信頼性を向上することができる半導体装置の製造方法を提供すること。

【解決手段】第一の接合工程では、半導体チップ10、第一樹脂層11、半導体チップ12、第二樹脂層13、半導体チップ14を積層することにより得られ、半導体チップ10,12同士、半導体チップ12,14同士が半田接合されていない状態の積層体2を加熱して、半導体チップ10,12間、半導体チップ12,14間の半田接合を行う。その後、半田接合した積層体2を基材18上に設置する。積層体2の基材18への接続用端子162と、基材18の積層体2への接続用端子181とが当接するように、積層体2を基材18上に設置する。

(もっと読む)

半導体装置の製造方法及び処理装置

【課題】薬液の除去性能を高く維持することができる半導体装置の製造方法及び処理装置を提供する。

【解決手段】レジストパターン3をマスクとして絶縁膜2をドライエッチングすることにより開口部4を形成する。絶縁膜2のドライエッチングの際に開口部4の内面に付着した反応生成物5に波長が200nm以下の紫外線を照射して、反応生成物5に含まれる有機成分を分解する。薬液を用いて、有機成分の分解後に開口部4の内面に残存している付着物6を除去する。付着物6が除去された開口部4内に導電膜7を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】前記半導体装置をスクライブ工程により切り離す際に、クラックが歪みを蓄積した保護膜を伝播して半導体装置内部に侵入するのを抑制し、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体装置は、活性素子が形成された素子領域を有する基板と、前記基板上に形成され、多層配線構造を含む積層体と、前記積層体中に、前記素子領域を囲んで連続的に延在する耐湿リングと、前記積層体中、前記耐湿リングの外側に、前記耐湿リングに沿って連続的に、前記基板の表面に達して形成された保護溝部と、前記保護溝部の底面の一部及び前記保護溝部の内側の側壁面に連続して形成された保護膜と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】高アスペクト比の溝内にカバレッジ性良く絶縁膜を埋め込むと表面にスリット状の空孔が形成され、CMPで平坦化すると、CMPで用いた組成物や、研磨された除去物、その他の残渣が空孔内に残り易く、この残渣は後の工程での発塵の一原因となり得る。

【解決手段】基板1の第1の主面に、俯瞰形状が環状となる第1の溝部2Tを形成し、第1の主面全面に第1の絶縁膜2aを形成し、第1の絶縁膜2aの表面から前記第1の溝部の内部まで達する深さの空孔を残しつつ、前記第1の絶縁膜を第1の溝部に埋め込み、空孔内を埋め込むように第1の絶縁膜上に第2の絶縁膜を形成し、第1の溝部内に第1の絶縁膜および第2の絶縁膜を残しつつ、基板表面高さまで化学機械研磨法により平坦化する。

(もっと読む)

半導体ダイ上にフィーチャをめっきするためのヒューズバス

【課題】半導体ダイ上に相互接続部又はボンドパッドなどのフィーチャ構造を電気めっきする方法を提供する。

【解決手段】方法は半導体基板の上方に複数のヒューズ(208)を形成する工程と、半導体基板の上方の複数の相互接続層(400〜408)と、該複数の相互接続層の上面の複数の相互接続パッド(502)とを形成する工程と、を含む。シールリング(202)が、半導体基板(302)と、前記複数の相互接続パッド(502)と、前記複数のヒューズ(208,320)とに形成された能動回路を包囲する。各ヒューズ(208,320)は、対応する相互接続パッド(502)とシールリング(202)とに電気的に接続される。各ヒューズ(208)が導通状態にあるとき、該ヒューズは対応する相互接続パッド(502)をシールリング(202)に電気的に接続する。

(もっと読む)

半導体装置および試験方法

【課題】より小さな単位に切り離しも可能なマルチコア半導装置において、前記より小さな単位に切り離した場合に相互接続配線を伝って生じる可能性のある水の侵入を阻止する。

【解決手段】半導体装置は、素子領域を有する半導体基板と、前記素子領域に形成され、第1の開口部を有する内側シールリングと、前記素子領域に形成され、第2の開口部を有する外側シールリングと、前記半導体基板上に形成された、各々配線層を含む複数の層間絶縁膜を積層した積層体よりなる多層配線構造と、前記多層配線構造に含まれる第1の層間絶縁膜とその上の第2の層間絶縁膜の間に形成された耐湿膜と、前記耐湿膜の下側および上側のいずれか一方である第1の側を延在し、前記第1の開口部を通過する第1の部分と、前記耐湿膜の下側および上側の他方である第2の側を延在し、前記第2の開口部を通過する第2の部分と、前記第1の部分と前記第2の部分とを、前記耐湿膜を貫通して接続するビアプラグとを含む配線パターンと、を有する。

(もっと読む)

ボンディングパッド構造を有する裏面照射型センサーとその製造方法

【課題】ボンディングパッド構造を有する裏面照射型センサーとその製造方法を提供する。

【解決手段】本発明は半導体構造を提供する。半導体構造は、正面と背面を有する装置基板;装置基板の正面上に設置される相互接続構造;および、相互接続構造に接続されるボンディングパッドを含む。ボンディングパッドは、誘電材料層中の凹部領域;凹部領域間に挿入される誘電材料層の誘電体メサ; および、凹部領域中と誘電体メサ上に設置される金属層を含む。

(もっと読む)

半導体装置

【課題】多層配線内の信号線とそれに接続されるビアとを共に同軸構造にする。

【解決手段】多層配線には、例えば、異なる層に設けられる信号線10,20と、これらの信号線10,20間を接続する接続部30(ビア)が設けられる。信号線10,20は、配線層及び配線層間を接続する接続層で囲み、同軸構造とする。更に、信号線10,20間を接続する接続部30も、配線層及び配線層間を接続する接続層で囲み、同軸構造とする。信号線10,20のほか接続部30も同軸構造とすることで、信号線10,20及び接続部30を伝送される信号の、周囲からの、又は周囲への、電磁気的な影響が効果的に抑制されるようになる。

(もっと読む)

電子デバイス及びその製造方法

【課題】貫通電極の基板等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通電極の側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い電子デバイスを提供する。

【解決手段】基板1と、基板1の表面上方に形成された配線18と、基板1の裏面から基板1を貫通しており、基板1の深さ方向において、第1の開孔1Aaと、第1の開孔1Aaよりも開口総面積が小さい第2の開孔1Abとが接続された貫通孔1Aに形成されてなる貫通ビア30とを含み、貫通ビア30は、第1の開孔1Aaに形成された第1の電極部30aと、第2の開孔1Abに形成された第2の電極部30bとが、最外側面が一体形成される。

(もっと読む)

半導体装置の作製方法

【課題】信頼性が高く、ソースとドレインの間にリーク電流が生じにくく、コンタクト抵抗が小さい半導体装置を提供する。

【解決手段】酸化物半導体膜により形成されるトランジスタの電極膜上に酸化物半導体膜に接して設けられた第1の絶縁膜、及び第2の絶縁膜を積層して形成し、第2の絶縁膜上にエッチングマスクを形成し、エッチングマスクの開口部と重畳する部分の第1の絶縁膜及び第2の絶縁膜をエッチングして電極膜を露出する開口部を形成し、第1の絶縁膜及び第2の絶縁膜の開口部をアルゴンプラズマに曝し、エッチングマスクを除去し、第1の絶縁膜及び第2の絶縁膜の開口部に導電膜を形成し、第1の絶縁膜は加熱により酸素の一部が脱離する絶縁膜であり、第2の絶縁膜は第1の絶縁膜よりもエッチングされにくく、第1の絶縁膜よりもガス透過性が低い。または逆スパッタリングを行ってもよい。

(もっと読む)

半導体装置

【課題】配線におけるエレクトロマイグレーション耐性を向上させる。

【解決手段】ソース領域42、ソース領域44およびドレイン領域46を有するP型MOSFET40と、ソース領域52、ソース領域54およびドレイン領域56を有し、かつP型MOSFET40と隣接するN型MOSFET50と、ドレイン領域46およびドレイン領域56に接続するドレイン電極と、ドレイン電極と接続し、かつドレイン電極上に設けられた複数のビア10と、を備え、P型MOSFET40とN型MOSFET50は、インバータ回路を構成しており、ドレイン電極は、ビア10を介しては、インバータ回路の出力信号配線30と接続し、他には接続していない。

(もっと読む)

61 - 80 / 2,145

[ Back to top ]