Fターム[5F033MM05]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | 積層 (3,773)

Fターム[5F033MM05]の下位に属するFターム

ポリサイド (516)

3層以上 (1,359)

界面が水平でないもの (14)

Fターム[5F033MM05]に分類される特許

41 - 60 / 1,884

エッチング液

【課題】 銅及びモリブデン積層膜を一液でエッチングでき、しかも工業的に好ましい形状にエッチングできるエッチング液を提供する。

【解決手段】 過酸化水素、グリシン、燐酸及び水を含むエッチング液を、銅及びモリブデン積層膜のエッチングに用いる。

(もっと読む)

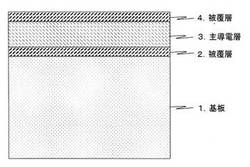

電子部品用積層配線膜および被覆層形成用スパッタリングターゲット材

【課題】 耐湿性や耐酸化性を改善し、さらに低抵抗な主導電層であるCuと積層した際に、加熱工程を経ても低い電気抵抗値を維持できる、Mo合金からなら被覆層を用いた電子部品用積層配線膜および被覆層を形成するためのスパッタリングターゲット材を提供する。

【解決手段】 基板上に金属膜を形成した電子部品用積層配線膜において、Cuを主成分とする主導電層と該導電層の一方の面および/または他方の面を覆う被覆層からなり、該被覆層は原子比における組成式がMo100−x−y−Nix−Tiy、10≦x≦50、3≦y≦30、x+y≦53で表され、残部が不可避的不純物からなる電子部品用積層配線膜。

(もっと読む)

銅および銅合金のエッチング液

【課題】

本発明の課題は、銅層と銅酸化物層および/または銅合金層とを含む金属積層膜パターンを精度良くエッチング加工し、優れた断面形状を形成し、かつ実用性に優れた安定で液寿命の長いエッチング液組成物、およびかかるエッチング液組成物を用いたエッチング方法を提供することにある。

【解決手段】

本発明は銅層と銅酸化物層および/または銅合金層とを有する金属積層膜を、過硫酸塩および/または過硫酸溶液0.1〜80重量%と、りん酸0.1〜80重量%と、硝酸および/または硫酸0.1〜50重量%とを含有するエッチング液組成物であり、さらに塩化物イオンやアンモニウムイオンを加えることで、エッチングレートや断面形状を容易に制御することが可能となるエッチング液組成物またはエッチング方法に関する。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いた表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供する。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させること

ができる。

(もっと読む)

半導体装置、半導体パッケージ、半導体装置の製造方法及び半導体パッケージの製造方法

【課題】電気的接続信頼性を向上させることができる半導体装置を提供する。

【解決手段】半導体チップ3は、第1主面30Aと第2主面30Bとの間を貫通する貫通孔30Xを有する半導体基板30と、半導体基板30の第2主面30Bを覆うように形成され、貫通孔30Xと対向する位置に開口部31Xが形成された絶縁層31と、絶縁膜33によって覆われた貫通孔30X及び開口部31Xに形成された貫通電極32とを有する。絶縁層31から露出される貫通電極32の上端面は、当該半導体チップ3に他の半導体チップ4が積層される際のパッドになる。また、貫通電極32の上端面は、絶縁層31の半導体基板30と接する面と反対側の面と面一になるように形成されている。

(もっと読む)

電界効果トランジスタ

【課題】ゲート電極とソース電極との間に印加される電圧がソース電極パッドの電気抵抗による電圧降下で低下することを防止でき、安定した動作を実現できる電界効果トランジスタを提供する。

【解決手段】このGaN HFETによれば、ボンディング部16Bの第2のパッド部16B‐2は、電極接続部16Aが含有する複数の接続部分19のうちの第2の方向(ソース電極12とドレイン電極11が対向している方向)の一端に配置された接続部分19の上記第2の方向の外端を電極延在方向へ延長した仮想延長線L1に関して第1のパッド部16B‐1とは反対側に位置している。第2のパッド部16B‐2に接続された第2のソース配線24のボンディング箇所の第2の方向の位置を電極接続部16Aのソース電極12との接続部分19の第2の方向の位置と重ならないようにして、ソース電極12からの電流が第2のソース配線24に流れにくくできる。

(もっと読む)

配線膜およびそれを用いたアクティブマトリクス基板、並びに配線膜の製造方法

【課題】テーパー形状のAl配線膜を容易かつ安定的に得る。

【解決手段】Al配線膜101は、AlもしくはAl合金から成る第1のAl合金層101aと、その上に配設され、Ni、PdおよびPtのいずれか1以上の元素を含み第1のAl合金層101aとは異なる組成のAl合金から成る第2のAl合金層101bとから成る二層構造を有する。フォトレジスト102の現像処理に用いるアルカリ性薬液により、第2のAl合金層101bはエッチングされ、その端部はフォトレジスト102の端部よりも後退する。その後、フォトレジスト102をマスクとするウェットエッチングを行うことにより、Al配線膜101の断面はテーパー形状となる。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、製造コストを低減し、さらにゲート電極およびゲートコンタクトの抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、ゲート電極7の少なくとも上層は、第2金属シリサイド膜としてのWSix膜72からなり、第1金属シリサイド膜としてのNiSi2膜18に含まれる第1金属(Ni)とシリコンとの結合エネルギーが、WSix膜72に含まれる第2金属(W)とのシリコンとの結合エネルギーよりも小さく、WSix膜72の組成MSix(Mは第2金属を示す)において、xが1.5以上2.0未満であることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波特性の悪化を防ぎ、耐湿性を向上させる。

【解決手段】半導体基板1の主表面上の素子領域内に、ドレイン電極2が設けられている。一端がドレイン電極2に接続されたドレイン配線5が主表面上に設けられている。主表面上の素子領域外に、ドレイン配線5とは離間したドレイン電極パッド12が設けられている。Auメッキ層9が主表面上に設けられ、主表面との間に空隙10が形成されている。空隙10はドレイン配線5の一端とドレイン電極2を内包する。硬化されたポリイミド膜14が空隙10の開口部11を閉塞し、ドレイン電極パッド12を覆うことなく、ドレイン配線5の他端を覆っている。空隙10の内面に撥液膜15が設けられている。硬化されたポリイミド膜14に設けられた開口16を介してAuメッキ層18により、ドレイン配線5の他端とドレイン電極パッド12が接続されている。ドレイン配線5の他端はポリイミド膜14から出ていない。

(もっと読む)

貫通配線の検査方法、貫通配線基板の製造方法

【課題】1つの貫通配線のみの抵抗を測定できる貫通配線の検査方法、及び該貫通配線の検査方法を行う工程を含む貫通配線基板の製造方法の提供。

【解決手段】基板1の一方の面1aに配された導電部2と、基板1を貫通し、導電部2と接続される第一貫通配線3、第二貫通配線4および第三貫通配線5とを少なくとも備えた貫通配線基板10を用い、基板1の他方の面1b側から第一貫通配線3及び第二貫通配線4に、定電流源6の一組の端子6a,6bを電気的に接続して、第一貫通配線3、導電部2、第二貫通配線4の経路に電流を流すと同時に、基板1の他方の面1b側から第一貫通配線3及び第三貫通配線5に、電圧計7の一組の端子7a,7bを電気的に接続して、第一貫通配線3における電圧降下を測定することを特徴とする貫通配線の検査方法。

(もっと読む)

貫通配線基板および貫通配線基板の製造方法

【課題】貫通孔内に形成された導電層に加わる応力を抑制できるとともに、導電層からの効果的な放熱も促すことができる貫通配線基板、及びこの貫通配線基板の製造方法を提供する。

【解決手段】半導体基板11(基板)の一方の面11aに配された電極層12と、電極層12の少なくとも一部が露呈するように半導体基板11内に開けられた貫通孔20と、貫通孔20の内側面20aを覆い、電極層12の少なくとも一部が露呈するように配された第一絶縁層15と、第一絶縁層15を介して、貫通孔20の内側面20a及び電極層12の露呈部を覆うように配され、電極層12と電気的に接続された導電層5と、導電層5を覆うように配された第二絶縁層16と、を少なくとも備えてなる貫通配線基板10であって、第二絶縁層16は、導電層5の表面形状に沿って形成されていることを特徴とする。

(もっと読む)

電極構造、半導体素子、半導体装置、サーマルヘッドおよびサーマルプリンタ

【課題】シェア強度の向上した電極構造を提供する。

【解決手段】電極構造C1は、基体2と、基体2上に設けられた電極4と、電極4上に設けられためっき層14とを備え、めっき層14は、第1部位14aと、第1部位14a上に位置する第2部位14bとを有しており、平面視して、第1部位14aの面積が第2部位14bの面積よりも大きいことから、電極構造C1のシェア強度を向上させることができ、シェア強度の向上した電極構造を提供することができる。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】メモリセルトランジスタのゲート電極間の空隙の形状を最適化し、高性能、高信頼性を実現する不揮発性半導体記憶装置の製造方法。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板上に、第1のゲート絶縁膜、第1のフローティングゲート電極、第1のゲート間絶縁膜、第1のコントロールゲート電極、第1のゲートマスク絶縁膜の積層構造を有する複数のメモリセルゲート電極を形成する。メモリセルゲート電極の側壁部に保護膜を形成し、その一部を第1のコントロールゲート電極の側壁部の一部が露出するよう除去する。金属膜を形成し、熱処理により、金属膜と第1のコントロールゲート電極を反応させ第1の金属半導体化合物層を形成する。メモリセルゲート電極間を埋め込み、内部に空隙を有する層間絶縁膜であって、第1のコントロールゲート電極の上面よりも半導体基板から離れた位置に空隙の上端が位置する層間絶縁膜を形成する。

(もっと読む)

半導体ウェハ及び半導体装置の製造方法

【課題】第1の溝への絶縁膜の埋設性が向上させて、埋設不良を軽減する。アライメントマークにおける埋設不良個所での応力集中がもたらす基板へのクラックを軽減する。

【解決手段】基板の第1の主面に、第1の溝、および前記第1の主面に対向して見た形状が環状となりかつ前記第1の溝よりも深い第2の溝を形成する工程と、第1の溝と第2の溝とを埋め込むように絶縁膜を形成する工程と、絶縁膜を形成する工程の後、基板の第1の主面にフォトレジスト膜を形成する工程と、絶縁膜で埋め込まれた第1の溝の基板上での位置を基準として位置合わせした第1のパターンをフォトレジスト膜に転写する工程と、絶縁膜で埋め込まれた環状の第2の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】超音波振動を利用したワイヤーボンディングの際に、p型オーミック電極がp型不純物拡散領域の面上から剥離することを防止する。

【解決手段】パッド電極7にボンディングワイヤー8を接合する際に、ボンディングツール100を用いて、ボンディングワイヤー8をパッド電極7に接触させた状態で、ボンディングワイヤー8に荷重を加えながら、p型オーミック電極5の長手方向に沿って超音波振動を印加する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、コンタクトプラグが形成されるセル部と、前記コンタクトプラグが形成されない周辺回路部とを平坦化できる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に最上部が第1の絶縁膜からなる配線層を形成する工程と、

前記半導体基板と前記配線層とを被う第2の絶縁膜を形成する工程と、前記第2の絶縁膜の所定の領域をエッチングし、前記配線層と前記半導体基板とを露出させる開口部を形成する工程と、前記開口部内と前記第2の絶縁膜上とに導電膜を形成する工程と、前記第1の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有し、前記第2の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有する条件で、前記第2の絶縁膜と前記導電膜とを前記第1の絶縁膜が露出するようCMP法で除去し、コンタクトプラグを形成する工程を有する半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】回路素子の素子特性の変動を抑制すること。

【解決手段】半導体基板110には、拡散領域111を有する抵抗素子(回路素子)R1が形成されている。拡散領域111を含む半導体基板110の上には、層間絶縁膜161が形成される。拡散領域111のシリサイド層(コンタクト部)111aは、コンタクトプラグ162を介して層間絶縁膜161上の配線と接続される。拡散領域111の上には、コンタクトホール163を形成するためのエッチングストッパ膜152が形成されている。このエッチングストッパ膜152は、拡散領域111上の保護絶縁膜131に対応する部分が除去され、開口が形成されている。

(もっと読む)

表示装置

【課題】配線等のパターンを、材料の利用効率を向上させ、かつ、作製工程を簡略化して得られた表示装置である。また配線等のパターンを所望の形状で制御性よく形成された導電膜を有する表示装置である。

【解決手段】トランジスタ上の第1の導電膜と、第2の導電膜とは、複数の屈曲点を有するコの字状に設けられる。本形状であっても、第1の導電膜と、第2の導電膜とはパターンを所望の形状で制御性よく形成される。なお、第1の導電膜と第2の導電膜は、共通電極層と、画素電極層となることができる。

(もっと読む)

金属パターンの製造方法

【課題】簡易なプロセスでパターン欠陥を抑制することが可能な金属パターンの製造方法を提供する。

【解決手段】アルミニウムを含む金属パターン20を製造する際に、真空雰囲気下にて、気相法により、基板上にアルミニウムを含む金属膜21を成膜する工程(1)と、金属膜21の表面に酸化処理により酸化膜22を形成する工程(2)と、酸化膜22上に金属パターンに対応したレジストパターン30を形成する工程(3)と、レジストパターン30をマスクとして、金属膜21をエッチングする工程(4)とを順次実施する。工程(1)と工程(2)との間において、少なくとも工程(2)の実施直前には、基板の雰囲気を真空雰囲気とする。

(もっと読む)

41 - 60 / 1,884

[ Back to top ]