Fターム[5F033MM05]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | 積層 (3,773)

Fターム[5F033MM05]の下位に属するFターム

ポリサイド (516)

3層以上 (1,359)

界面が水平でないもの (14)

Fターム[5F033MM05]に分類される特許

101 - 120 / 1,884

半導体チップ

【課題】金属原子の拡散に起因する素子特性の劣化を抑制する。

【解決手段】半導体チップは、半導体基板10と、半導体基板10を貫通する貫通電極20と、半導体基板10を貫通する金属柱40と、アライメントマーク47と、絶縁性を有する筒状の絶縁膜50とを有する。アライメントマーク40は、半導体基板10の外部に露出した金属柱40の端部によって形成されている。筒状の絶縁膜50は、半導体基板10に形成されており、金属柱40を取り囲んでいる。

(もっと読む)

半導体装置、および、その製造方法

【課題】製造効率の向上、コストダウン、信頼性の向上を実現する。

【解決手段】第1導電型の第1電界効果トランジスタを第1基板に設ける。そして、第1導電型と異なる第2導電型の第2電界効果トランジスタを第2基板に設ける。そして、第1基板と第2基板とのそれぞれを対面させて貼り合わせる。そして、第1電界効果トランジスタと第2電界効果トランジスタとの間を電気的に接続させる。

(もっと読む)

半導体チップとその製造方法、半導体装置

【課題】立体的な集積に適した、電磁妨害耐性に優れる半導体チップを提供する。また、その半導体チップを用いた、高い電磁妨害耐性と高い処理能力を両立する半導体装置を提供する。

【解決手段】能動素子もしくは受動素子と、それらの素子を電気的に接続する配線部を備えた半導体チップについて、配線部を被覆するように導電性薄膜を設ける。この導電性薄膜は配線部に対して、不要電磁波を遮蔽するシールドとして働くので、半導体チップの電磁妨害耐性が向上する。また、この半導体チップを三次元集積半導体装置に組み込むことで、隣接するチップをフェイス・トゥ・フェイス接続した場合でも、チップ間のクロストークを遮断できる。

(もっと読む)

半導体素子

【課題】熱(工程)に耐性のある配線構造を採用し、配線上の析出物の発生を抑制できる半導体素子を実現する。

【解決手段】半導体素子本体に接続する金材を含む配線パターンと、この配線パターンに一端側が接続され金材を含む接続端子と、前記半導体素子本体と前記配線パターンと前記接続端子とを覆う絶縁体と、を具備する半導体素子において、前記配線パターンあるいは接続端子の一方の面に一面が接し他面が前記絶縁体に接する面状のシリサイド体を具備したことを特徴とする半導体素子である。

(もっと読む)

半導体装置

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

Cu合金膜、及びそれを備えた表示装置または電子装置

【課題】基板及び/又は絶縁膜との高い密着性を有し、且つ、液晶表示装置などの製造過程で施される熱処理後も低い電気抵抗率を有する新規なCu合金膜を提供する。

【解決手段】基板上にて、基板及び/又は絶縁膜と直接接触するCu合金膜であって、前記Cu合金膜は基板側から順に、合金成分としてX(Xは、Ag、Au、C、W、Ca、Mg、Al、Sn、BおよびNiよりなる群から選択される少なくとも一種の元素)を含有するCu−Mn−X合金層(第一層)と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる層(第二層)で構成されたCu合金膜である。

(もっと読む)

半導体素子

【課題】不良品の発生を容易に防止出来て歩留まりの向上と製造条件の確認の容易な半導体素子を実現する。

【解決手段】半導体素子本体の外表面を覆って設けられた絶縁膜と、この絶縁膜に設けられ前記半導体素子本体に一端側が接する外部接続用端子と、前記絶縁膜に穿設され一端側が前記外部接続用端子に接する配線取出し孔と、を具備する半導体素子において、前記外部接続用端子の前記配線取出し孔に接する面全体に一面が接し他面が前記絶縁膜に接して設けられ前記外部接続用端子の色と前記絶縁膜の色と異なる色を有し前記配線取出し孔の穿設時に除去されることにより前記配線取出し孔の穿設完了を識別する識別膜とを具備したことを特徴とする半導体素子である。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

電極構造及びその製造方法

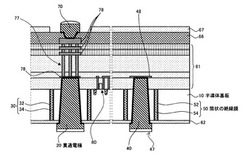

【課題】ウェハハンドリングが容易であり、高精度の位置合わせを必要とせず、ビアホールとして機能する開口部を浅く形成でき、さらに開口部を埋め込む第1電極と基板との界面の割れを防止できる電極構造、及びその製造方法を提供することにある。

【解決手段】基板に、第1主表面側から、深さが基板の厚さよりも小さい開口部33を形成する。次に、開口部を埋め込む第1電極35を形成する。次に、第1主表面と対向する基板を第2主表面側から薄層化して、開口部の深さよりも大きい厚さとする。次に、第2主表面側111bから開口部の底面33bへ向けて、基板111に切り込みを入れる39ことによって、第2主表面側から第1電極を露出させる。次に、切り込みを埋め込む第2電極44を形成する。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

半導体基板、その製造方法、および電子装置

【課題】カーボンナノチューブを用いた特性が良好な半導体基板、その製造方法、および電子装置を提供することにある。

【解決手段】

本発明の一態様による半導体基板は、一主面に下部電極を有する基板と、前記基板上の前記下部電極以外の部分に設けられた層間絶縁膜と、前記下部電極の上に設けられた触媒層と、前記触媒層上に設けられ、前記下部電極の一主面に垂直な方向に延伸する複数のカーボンナノチューブと、前記カーボンナノチューブ上に設けられ、前記下部電極と対向する上部電極と、前記触媒層および前記カーボンナノチューブの前記触媒層側の端部を覆う第1の埋め込み膜と、前記カーボンナノチューブの他端部の間に満たされ、前記第1の埋め込み膜よりも高密度のである第2の埋め込み膜と、を有する。

(もっと読む)

無電解メッキパターン形成用組成物、塗布液、及び無電解メッキパターン形成方法

【課題】無電解メッキパターンを正確に形成できる無電解メッキパターン形成用組成物、塗布液、及び無電解メッキパターン形成方法を提供すること。

【解決手段】表面を有機物103で修飾されるとともに、前記表面103に触媒金属微粒子105を担持した金属化合物粒子101を含む無電解メッキパターン形成用組成物。前記有機物103としては、3-ヒドロキシ-4-ピロン誘導体、又は1,2-ジオールが挙げられる。前記触媒金属微粒子105としては、パラジウム、銀、白金、ニッケル、及び銅からなる群から選ばれる1種以上の微粒子が挙げられる。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

半導体装置の製造方法

【課題】 金属部材の表面に、再現性よくバリア膜を形成する技術が望まれている。

【解決手段】 基板の上に、下部バリア膜を形成する。下部バリア膜の上にシード膜を形成する。シード膜の一部の領域上に、導電部材を形成する。導電部材をエッチングマスクとして、シード膜をエッチングし、導電部材の形成されていない領域において、下部バリア膜を露出させる。下部バリア膜の表面には堆積しない条件で、導電部材の表面に選択的に上部バリア膜を成長させる。上部バリア膜をエッチングマスクとして、下部バリア膜をエッチングする。

(もっと読む)

金属薄膜パターンの製造方法

【課題】高温にも耐え得る矩形断面の正確な金属薄膜パターンを、簡単な工程によって製造可能とすること。

【解決手段】下記に示す感光性金属錯体を含む塗布液1を基板10に塗布し(A)マスク20を介して所定の部分のみを露光した(B)。露光によりエステル結合が切れて易溶化した可溶部1Aを(C)、TMAH水溶液により除去し(D)、不溶部1Bを金属化するまで加熱し(E)、Cu等の金属30でメッキする(F)。

【化9】 (もっと読む)

(もっと読む)

パターン修正方法

【課題】配線パターンの修正において、修正抵抗を低減することが可能となる、パターン修正方法を提供する。

【解決手段】パターン修正方法は、導電性パターン20の欠陥部21を修正するパターン修正方法であって、導電性インクを塗布することにより第1のインク層31を形成する工程と、第1のインク層31を焼成することにより第1の修正層32を形成する工程と、少なくとも一部が第1の修正層32に重なるように導電性インクを塗布することにより、第2のインク層33を形成する工程と、第2のインク層33を焼成することにより第2の修正層34を形成する工程とを備え、第1の修正層32および第2の修正層34により欠陥部21を挟んで配置される導電性パターン20間の電気的接続が確保される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

101 - 120 / 1,884

[ Back to top ]