Fターム[5F033MM05]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | 積層 (3,773)

Fターム[5F033MM05]の下位に属するFターム

ポリサイド (516)

3層以上 (1,359)

界面が水平でないもの (14)

Fターム[5F033MM05]に分類される特許

161 - 180 / 1,884

半導体装置

【課題】基板の大型化に対応し得る金属配線を作製する。

【解決手段】絶縁表面上に少なくとも一層の導電膜12,13を形成し、前記導電膜12,13上にレジストパターンを形成し、前記レジストパターンを有する導電膜にエッチングを行い、バイアス電力密度、ICP電力密度、下部電極の温度、圧力、エッチングガスの総流量、エッチングガスにおける酸素または塩素の割合に応じてテーパー角αが制御された金属配線を形成する。このようにして形成された金属配線は、幅や長さのばらつきが低減されており、基板10の大型化にも十分対応し得る。

(もっと読む)

開口部の形成方法及び半導体装置の作製方法

【課題】少なくともフォトマスクの枚数を増加させることなく、積層構造の下部の導電層が露出するように該導電層上の絶縁膜に対する開口部の形成方法を提供する。

【解決手段】開口部が設けられる部分の積層構造の下部の導電層を、該開口部を形成するフォトマスクと同一のフォトマスクを用いて形成されたエッチングマスクにより予め露出させ、その後保護絶縁膜を形成し、前記積層構造の上部の導電層が開口部において露出されないように、保護絶縁膜に開口部を形成する。このような開口部の形成方法は、半導体装置の作製方法に適用することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】スルーホールの微細化による半導体装置の高集積化と、スルーホール内に埋め込まれる導体のカバレッジ性と、を両立させる。

【解決手段】半導体装置は、下層配線2と、下層配線2上に形成され、下層配線2の上面を露出させる開口31を有する第1絶縁膜(例えば、有機絶縁膜3)と、第1絶縁膜上に形成され、スルーホール5が形成された第2絶縁膜(例えば、無機絶縁膜4)とを有する。半導体装置は、更に、スルーホール5に埋め込まれ、下層配線2と電気的に接続された導体9を有する。開口31は、上側に向けて拡径するテーパー形状に形成されている。スルーホール5の側壁5aの少なくとも下端は、開口31の側壁31aを構成する傾斜面の上に位置している。

(もっと読む)

バリア層の形成方法

【課題】 本発明は、以上の点に鑑み、異種金属からなる導電層間に介在されるような場合でも十分なバリア性能を発揮し得るバリア層を生産性よく形成することができるバリア層の形成方法を提供する。

【解決手段】 バリア層BMは、処理対象物Wを一方の導電層CL1を有するものとし、この処理対象物と、例えばTi製のターゲット2とを真空処理室1a内に配置し、真空処理室内に希ガスを導入してプラズマ雰囲気を形成し、ターゲットをスパッタリングして一方の導電層表面に第1金属層を形成し、真空処理室内に酸素ガス及び窒素ガスを含むガスを導入してプラズマ雰囲気を形成し、第1金属層の表面を酸窒化処理すると共に、ターゲットをもプラズマ雰囲気に曝して当該ターゲット表面を酸窒化し、真空処理室内に希ガスを更に導入してプラズマ雰囲気を形成し、ターゲットをスパッタリングして酸窒化処理された表面に第2金属層を形成してなる。

(もっと読む)

半導体装置

【課題】3次元的に積層された複数の半導体チップを有する半導体装置の製造歩留まりを向上できる技術を提供する。

【解決手段】半導体基板1の第2面1bからパッド3に達する貫通電極17が形成されている。貫通電極17の内部にある貫通空間は、第1孔7および第1孔7よりも孔径の小さい第2孔11によって構成されている。半導体基板1の第2面1bから半導体基板1を貫通して層間絶縁膜2の途中まで第1孔7が形成されている。そして、第1孔7の底部から層間絶縁膜2を貫通してパッド3に達する第2孔11が形成されている。このとき、半導体基板1の第1面1aに形成されている層間絶縁膜2は、第1孔7の底面と半導体基板1の第1面1aとの段差を反映して段差形状になっている。すなわち、第1孔7の底面とパッド3間に存在する層間絶縁膜2の膜厚がその他の場所の層間絶縁膜2の膜厚よりも薄くなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、アルミ配線パターンに含まれるアルミニウムと銅配線に含まれる銅とが反応して高抵抗の合金が生成されることを防止した上で、導電膜である窒化チタン膜に起因する半導体基板の反りを低減することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】第2の層間絶縁膜18に形成されたコンタクト孔27により露出された銅配線16の上面16aを覆うように、窒化チタン膜を含む第1の導電膜21を設けると共に、アルミ配線パターン23と第1の導電膜21及び第2の層間絶縁膜18との間に、窒化チタン膜を含まない第2の導電膜22を設ける。

(もっと読む)

半導体装置、液晶モジュール、電子機器及び配線

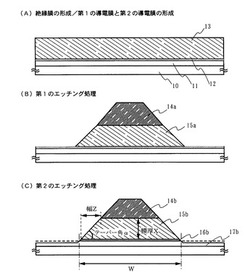

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

導電膜用エッチング液組成物

【課題】基板上に形成されたモリブデン系導電性薄膜、または、モリブデン系導電性薄膜とアルミニウム系導電性薄膜とが積層された積層導電性薄膜を、効率よく、側面が良好な順テーパー形状となるようなエッチングを行うことが可能なエッチング液、および、該エッチング液を用いたエッチング方法を提供することを目的とする。

【解決手段】(a)リン酸30〜80重量%と、(b)硝酸0.1〜20重量%と、(c)有機酸塩0.1〜20重量%と、(d)水とを含有するエッチング液を用いてエッチングを行う。

また、上記エッチング液を用いて、アルミニウム系導電性薄膜と、モリブデン系導電性薄膜とを備えてなる2層構造の積層導電性薄膜、または、アルミニウム系導電性薄膜と、アルミニウム系導電性薄膜を挟み込むようにその両主面側に配設された第1のモリブデン系導電性薄膜および第2のモリブデン系導電性薄膜を備えてなる3層構造の積層導電性薄膜をエッチングする。

(もっと読む)

半導体装置

【課題】高周波特性を低下させることなくLDMOSFETを有するチップの面積を縮小する。

【解決手段】LDMOSFETのソース領域と基板1の裏面に形成されたソース裏面電極36とを電気的に接続するp型打ち抜き層4を不純物を高濃度でドープした低抵抗のp型多結晶シリコン膜もしくは低抵抗の金属膜から形成する。そして、LDMOSFETの基本セルのソース同士を電気的に接続するソース配線は配線24Aのみとし、ソース配線を形成する配線層数は、ドレイン配線(配線24B、29B、33)を形成する配線層数より少なくする。

(もっと読む)

メッキ金属膜基板とその製造方法、及び半導体装置

【課題】一度の成膜で、所望の平面パターンと膜厚分布を有するメッキ金属膜を成膜することが可能なメッキ金属膜基板とその製造方法を提供する。

【解決手段】メッキ金属膜基板1は、基板上に少なくとも1層の給電金属膜20と少なくとも1層のメッキ金属膜30とを順次有し、少なくとも1層の給電金属膜20は、少なくとも1層のメッキ金属膜30の下地が相対的に高抵抗な高抵抗部20Hと、メッキ金属膜30の下地が相対的に低抵抗な低抵抗部20Lとを有するものである。

(もっと読む)

固定用構造および嵌合構造

【課題】チップの縁領域は、膨張係数が異なることによって、温度サイクル中に、TC応力とも称される特定の負荷を受けることが多い。これらの縁領域は特にTC応力を受け易いため、同領域内において様々な不良が生じる可能性がある。これによって、実際のデバイスにおける信頼性のリスクが増大する可能性がある。

【解決手段】半導体デバイスの金属構造210のための固定用構造200は、オーバーハング形状の側壁230を少なくとも1つ含んだ固定用凹部構造220を含んでいる。上記金属構造210は、少なくとも部分的に上記固定用凹部構造220内に配置されている。

(もっと読む)

半導体装置

【課題】工程数の増大を抑制しつつ、チップ上に形成された再配線または突出電極の信頼性を向上させる。

【解決手段】配線2bおよびパッド電極2aが形成された半導体基板と、半導体基板上に形成された応力緩和層4と、応力緩和層4上に合金シード膜5を形成した後、応力緩和層4と合金シード膜5とを熱処理にて反応させることで、応力緩和層4と合金シード膜5との間に反応性バリア絶縁膜6を形成する。再配線8または突出電極は合金シード膜5上に形成する。

(もっと読む)

バンプオンリード相互接続を形成する半導体素子および方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】半導体ダイの表面上に形成された複数の複合バンプを有する、半導体ダイを提供するステップであって、前記複合バンプは、可融性部分および非可融性部分を有する、ステップと、基板を提供するステップと、エスケープルーティング密度を増加させるための平面図から、伝導性トレースと平行な縁を有する相互接続部位を伴って前記基板上に複数の伝導性トレースを形成するステップであって、前記複合バンプは、前記相互接続部位よりも幅広い、ステップと、前記可融性部分が前記相互接続部位の頂面および側面を覆うように、前記複合バンプの前記可融性部分を前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記複合バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

パターン化金属膜及びその形成方法

【課題】ドライエッチングが困難な遷移金属の膜を、サイドエッチングが極力生じないようにパターニングする。

【解決手段】絶縁膜の上にバリア層・密着層を形成し(S1)、その上に遷移金属からなるシード層を形成する(S2)。シード層の上にSiO2膜及びフォトレジスト膜を順次形成し(S3、S4)、フォトレジスト膜、SiO2膜をパターニングして開口を形成し(S5,S6)、開口内にCu膜及びマスクAl膜を積層する(S7、S8)。次に、SiO2膜をエッチング(S9)、露出したシード層をその膜厚方向に異方的に改質し(S10)、改質されたシード層、露出したバリア・密着層、及びマスクAl膜を順次エッチングにより除去することにより(S10〜S13)、パターン化金属膜を得る。

(もっと読む)

マザー基板、電子部品の検査方法、電子部品、及び電子部品の製造方法、並びに電子機器

【課題】電子部品の貫通電極において、基板の両面から貫通電極に接触することが必要であることに起因して高度な検査技術が必要である貫通電極の検査を容易にすることができる、マザー基板、電子部品の検査方法、電子部品、及び電子部品の製造方法、並びに電子機器を提供する。

【解決手段】電子部品の製造方法は、マザー基板に区画形成された電子部品の製造方法であって、基板の第1面における複数の区画領域に回路を形成する回路形成工程と、区画領域にて、第1面と第1面の反対面である第2面とを電気的に接続する貫通電極を形成する貫通電極形成工程と、互いに異なる区画領域に位置する貫通電極を第1面にて連結配線で電気的に接続する連結配線形成工程と、第2面にて、連結配線形成工程で電気的に接続された複数の貫通電極に検査プローブを電気的に接続させることによって、貫通電極の機能を検査する機能検査工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】水素又はカルボン酸を用いたリフロー時の導電部と絶縁層の密着力低下を抑制する。

【解決手段】半導体基板の上に設けられた第1導電部上に絶縁層を形成し(ステップS1)、その絶縁層を被覆するようにバリア層を形成した後(ステップS2)、そのバリア層の上に第2導電部を形成する(ステップS3)。そして、第1導電部上の絶縁層がバリア層で被覆されている状態で、第2導電部を水素又はカルボン酸を含む雰囲気中で溶融し(ステップS4)、その後、その第2導電部をマスクにして、絶縁層の上からバリア層を除去する(ステップS5)。

(もっと読む)

表示装置用金属配線膜

【課題】Si半導体層および/または透明導電膜との間のバリアメタル層を省略しても、低抵抗のオーミック特性を有する電気的接触を確保でき、更に十分な耐熱性を有する表示装置用金属配線膜を提供する。

【解決手段】Moを20原子%以上含有しており、且つ、Si、Nd、Ni、Mn、Mg、Fe、及びZnよりなる群から選択される少なくとも一種を5原子%以上含有しているAl合金膜53と、純CuまたはCu合金膜28,29とからなる積層膜であって、前記Al合金膜が、半導体層33と直接接続していると共に、前記CuまたはCu合金膜が透明導電膜55と直接接続している表示装置用金属配線膜。

(もっと読む)

カーボンナノチューブ配線の製造方法

【課題】カーボンナノチューブを有するプラグ配線において良好な電気的接続を得ることができるカーボンナノチューブ配線の製造方法を提供する。

【解決手段】第1配線層12上に層間絶縁膜13を形成する工程と、第1配線層上の層間絶縁膜内にコンタクト孔15を形成する工程と、コンタクト孔内の第1配線層上にカーボンナノチューブ16を成長させ、コンタクト孔から先端が突き出た複数のカーボンナノチューブを形成する工程と、層間絶縁膜上及び複数のカーボンナノチューブ間に、ストッパ膜17を形成する工程と、ストッパ膜上及び複数のカーボンナノチューブ上に絶縁膜を形成する工程と、ストッパ膜をストッパとして用い、ストッパ膜上の絶縁膜と共に、コンタクト孔上の複数のカーボンナノチューブを除去する工程と、複数のカーボンナノチューブ上に第2配線層14を形成する工程とを備える。

(もっと読む)

半導体装置

【課題】並列駆動構成のI/Oバッファから出力される信号を安定化し、信頼性を向上する。

【解決手段】I/Oセル2は、1つの出力信号を正転信号と反転信号からなる相補信号として出力する相補型I/Oセルからなり、2つのI/Oセル2が並列接続された構成からなる。2つのI/Oセル2の出力部となるインバータ6の出力部は、配線17によってそれぞれ接続されており、2つのI/Oセル2の出力部となるインバータ7の出力部は、配線18によってそれぞれ接続されている。配線17は、I/Oセル2の下辺側に2つのI/Oセル2を横断するように形成され。配線18は、該配線17の上方に形成されており、2つのI/Oセル2を横断するように形成されている。また、配線17の配線長と配線18の配線長は、略同等となるようにレイアウトされている。

(もっと読む)

半導体装置、半導体装置の製造方法、及び半導体装置の検査方法

【課題】層間絶縁膜に生じたボイドを高感度に検出する。

【解決手段】この半導体装置は、多層配線層(非図示、以下略)と、多層配線層中に形成された第一TEGパターン(非図示)を備える。第一TEGパターンは、互いに平行に延伸した複数の第一下層配線402と、層間絶縁膜(非図示)を貫通し、平面視で第一下層配線402間に位置する第一ビア602と、多層配線層の最上層(非図示)に形成され、第一ビア602に接続している第一端子762と、上記した同一の最上層に形成され、第一下層配線402に接続している第二端子764と、を備える。

(もっと読む)

161 - 180 / 1,884

[ Back to top ]