Fターム[5F033MM05]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | 積層 (3,773)

Fターム[5F033MM05]の下位に属するFターム

ポリサイド (516)

3層以上 (1,359)

界面が水平でないもの (14)

Fターム[5F033MM05]に分類される特許

201 - 220 / 1,884

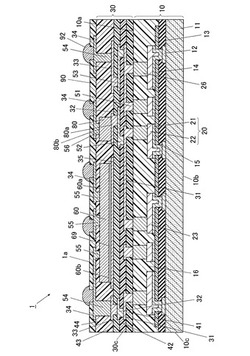

半導体装置及びその製造方法

【課題】薄型化及び小型化を図る半導体装置を提供する。

【解決手段】半導体装置1は、半導体チップ10と、半導体チップ10の上に積層された多層配線構造30と、多層配線構造30内に埋設された電子部品60,80と、を備える。半導体チップは、半導体基板11と、半導体基板上に形成された内部配線20と、内部配線を被覆するようにして半導体基板上に形成された封止層16と、を有し、多層配線構造が封止層上に形成されている。

(もっと読む)

電子機器

【課題】配線の凹凸差を緩和することが可能な構造の半導体装置を提供することを課題と

する。

【解決手段】第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層の間に形

成されると共に、接続孔を有する絶縁層と、第1の導電層及び第2の導電層に接続すると

共に、少なくとも端部の一部が接続孔の内側に形成される第3の導電層と、を有する半導

体装置である。第2の導電層及び第3の導電層が接続する接続孔付近において、第3の導

電層が第1の絶縁層を介して第2の導電層に重畳せず、第3の導電層の端部が第1の絶縁

層上に形成されない。このため、第3の導電層の凹凸を低減することが可能である。

(もっと読む)

グラフェン配線およびその製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】グラフェン配線の製造方法は、絶縁膜13内に、配線溝30を形成し、前記配線溝内の全面に、触媒膜14を形成し、前記配線溝内の前記触媒膜上に、前記配線溝の底面に対して垂直方向に積層された複数のグラフェンシート16a〜16eで構成されるグラフェン層16を形成することを具備する。

(もっと読む)

配線パターンの形成方法

【課題】触媒層の凝集を抑制し、また炭素の拡散性を制御して、欠陥の無いグラファイト膜を形成することができるグラフェン構造を含むグラファイト膜による配線パターンの形成方法の提供。

【解決手段】触媒層の凝集を抑制し、また炭素の拡散速度を適切に速度に調節することができる合金層又は積層体からなる触媒層を利用して、グラフェン構造を有するグラファイト膜で構成された配線パターンの形成方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】レーザー光の強度を弱めずに、スルーホールの形成に要する時間を短縮できるようにする。

【解決手段】半導体ダイ1が、半導体基板11と、半導体基板11上に設けられた配線23と、配線23上に設けられたレーザー光防護電極27と、を備える。半導体装置40が、半導体ダイ1と、半導体ダイ1を覆い、レーザー光防護電極27に対応する部分に設けられたスルーホール43aを有する封止層43と、封止層43のスルーホール43a内に設けられた導体44と、を備える。レーザー光防護電極27の上面は、導体44と接触する第一領域27dと、導体44と接触していない第二領域27cと、を有する。

(もっと読む)

半導体装置、及び、その製造方法

【課題】微細配線を有する半導体装置の信頼性を向上させる。

【解決手段】本発明に係る半導体装置は、第1のCu配線102と、第1のCu配線102の上に設けられ、第1のCu配線102からCuの拡散を防ぐ第1のバリア絶縁膜103とを備える。また、第1のバリア絶縁膜103の上には、第2のCu配線105と、第1のCu配線105の上に設けられ、第2のCu配線105からCuの拡散を防ぐ第2のバリア絶縁膜106と、を備える。第1、第2のバリア絶縁膜103、106は、分枝アルキル基、及び、炭素−炭素二重結合を有するシリコン系絶縁膜からなる。

(もっと読む)

配線基板の製造方法、発光装置及び電子機器

【課題】多層配線構造を有する配線基板において、上層配線の断線等による歩留まりの低下を抑制し、信頼性を向上させることのできる配線基板の製造方法、発光装置及び電子機器を提供する。

【解決手段】配線基板の製造方法は、基板100上に形成されたAl−Ni合金膜102上に保護膜としてMo合金膜104を形成する工程と、Mo合金膜104上にレジスト105を形成する工程と、Al−Ni合金膜102をエッチングして、基板100側の幅がその反対側の幅よりも大きい順テーパ形状を有する信号線Ldを形成する工程と、を備える。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

半導体装置とその製造方法

【課題】銅のワイヤを用いたボンディングに関し、効率の良い製造が可能な半導体装置とその製造方法を提供する。

【解決手段】基材2上に形成されている銅の電極パッド3と、前記電極パッド3を覆うように設けられている金の金属層4と、前記金属層4上にボンディングされている銅のワイヤ5とを有することを特徴としている。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセル領域の周辺に金属電極を有するアンチフューズを製造歩留り良く形成する。

【解決手段】MOSトランジスタを備えたメモリセルを有するメモリセル領域と、アンチフューズを備えた周辺回路領域とを有する半導体装置において、メモリセルを構成するコンタクトプラグ又はビット配線と同層に形成される周辺回路のコンタクトプラグ又は配線を用いて、アンチフューズの電極を形成する。

(もっと読む)

化合物半導体デバイス

【課題】高温にさらされても、Au配線表面に析出物が発生することを抑制できる半導体デバイスの製造方法を提供する。

【解決手段】化合物半導体基板1上の、Auからなる下部配線層3aと上部配線層3bの上部を覆って、Auより薄膜応力が小さく高融点を有する金属であるタンタルあるいはチタンからなる配線被覆層5と5’をスパッタにより形成する。

(もっと読む)

配線の形成方法及びその配線を有する表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】配線の形成方法及び配線を有する表示装置の形成方法は、基板上若しくは回路素子上に設けられた第1の金属拡散防止膜上に、金属シード層をCVD法により形成し、フォトレジストマスクを用いて選択的に無電解メッキ法、又は電解メッキ法により、金属配線層を形成し、金属シード層及び第1の金属拡散防止膜の不要領域除去と、金属シード層及び金属配線層及び第1の金属拡散防止膜の側面を含む表面を覆うように無電解メッキ法による第2の金属拡散防止膜の選択的な形成とにより配線及び電極を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】低伝導度領域ができるだけ少なくなるグラフェン配線構造が可能な半導体装置を提供する。

【解決手段】半導体装置は、触媒金属膜220と、グラフェン膜230と、コンタクトプラグ240と、調整膜250と、を備える。触媒金属膜は、基板上に形成される。グラフェン膜は、触媒金属膜上に形成される。コンタクトプラグは、グラフェン膜と接続する。調整膜は、前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に形成され、ディラック点位置をフェルミ準位に対してコンタクトプラグと接続する領域と同方向に調整する。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で横方向に成長するシリコン膜が連結されることを防ぎつつ、活性領域上に十分な厚みのシリコン膜を形成可能とした半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上に第1のシリコン膜12aを選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に第1のシリコン膜12aを覆うのに十分な厚みでマスク絶縁膜を埋め込んだ後、このマスク絶縁膜を第1のシリコン膜12aの表面が露出するまでエッチングにより除去する工程と、第1のシリコン膜12a上に第2のシリコン膜12bを選択的にエピタキシャル成長させる工程とを含む。

(もっと読む)

ウエハレベルパッケージ構造およびその製造方法

【課題】切削刃の磨耗を抑制して切削刃の寿命を延ばすことが可能なウエハレベルパッケージ製造方法を提供する。

【解決手段】ウエハレベルパッケージ製造方法は、例えば、基板450の表面に、配線が形成される溝462を含む絶縁性の第1の樹脂460を形成する樹脂形成工程400と、第1の樹脂460の表面に、配線の一部となる第1の金属470を、物理気相成長によって成膜する第1の成膜工程410と、第1の金属470の表面に、配線の一部となる、第1の金属470より硬度が低い第2の金属480を、更に成膜する第2の成膜工程420と、溝462の側面において第1の金属470が成膜されていない場所または薄くなっている場所に該当する高さH0、H1に切削刃490を設置する設置工程430と、切削刃490を走査することにより、少なくとも第1の樹脂460を切削する切削工程440とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】グラフェン層に対して良好なコンタクトを形成しうる配線構造体を有する半導体装置及びその製造方法を提供する。

【解決手段】グラフェン層と、グラフェン層の第1の領域に形成され、グラフェン層と、グラフェン層に積層された第1のネットワーク・ナノグラファイト層とを含む第1の配線部と、グラフェン層の第2の領域に形成され、グラフェン層と、グラフェン層に積層された第2のネットワーク・ナノグラファイト層とを含む第2の配線部と、グラフェン層の、第1の領域と第2の領域との間の第3の領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線の検査効率を向上させる。

【解決手段】複数の接続パッド12が設けられた半導体デバイスウエハ10と、半導体デバイスウエハ10の接続パッド12が設けられた面を被覆するとともに、接続パッド12を露出させる開口14aが設けられた絶縁膜14Aと、開口14aから露出された接続パッド12及び絶縁膜14Aの上部に設けられた配線15Aと、を備える半導体装置である。配線15Aは、無電解めっき用シード層16Aと、無電解めっき用シード層16Aを核とする無電解めっきにより形成される配線層19Aと、を含む。

(もっと読む)

電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造

【課題】酸化物反応層の寄生抵抗の低減を図り、動作特性の向上を図った電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造を提供する。

【解決手段】TFT素子1は、a−Si膜5上に形成されたPドープn+a−Si膜6と、Pドープn+a−Si膜6上に形成された1nm以下のSi酸化膜7を有している。電極配線膜となるCu合金膜8が、Si酸化膜7上にスパッタリングにより形成されている。Cu合金膜8は、0.3〜2.0原子%のSn、In、Gaの金属のうち1種以上を含有する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を簡略化することの可能な半導体装置の製造方法を提供する。

【解決手段】第2の層間絶縁膜14に、配線の上面を露出するように、第1の開口径とされた第1の開口部16、及び第1の開口径よりも小さい第2の開口径とされた第2の開口部17を一括形成し、次いで、第1及び第2の開口部の内面を覆う高誘電率絶縁膜19を成膜し、次いで、斜めイオン注入法により、第2の開口部の底面に形成された高誘電率絶縁膜にイオンが注入されないように、少なくとも第1の開口部の底面の外周に形成された高誘電率絶縁膜にイオンを注入し、その後、ウエットエッチングにより、イオンが注入された高誘電率絶縁膜を除去し、次いで、第1及び第2の開口部内を導電膜21で埋め込むことで、第1の開口部内にコンタクトプラグ22を形成すると共に、前記第2の開口部内に、第2の開口部に高誘電率絶縁膜及び導電膜よりなるアンチヒューズ素子23を形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】容量増加による高周波特性の劣化及び裏面電極に起因する絶縁破壊を抑止し、チップ面積を増加させることなく、インパクトイオン化により生成したホールを容易且つ確実に引き抜いて排出することを可能として、高耐圧性及び高信頼性を実現する化合物半導体装置及びその製造方法を提供する。

【解決手段】絶縁性又は半絶縁性の基板1の表面に電子走行層3、電子供給層4が形成され、電子供給層4内には局所的なp型領域7が形成されており、基板1の裏面にp型領域7の一部を露出させる開口1aが形成され、開口1aを導電材料で埋め込みp型領域7とオーミック接続された裏面電極8を備え、AlGaN/GaN・HEMTが構成される。

(もっと読む)

201 - 220 / 1,884

[ Back to top ]