Fターム[5F033MM05]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | 積層 (3,773)

Fターム[5F033MM05]の下位に属するFターム

ポリサイド (516)

3層以上 (1,359)

界面が水平でないもの (14)

Fターム[5F033MM05]に分類される特許

121 - 140 / 1,884

表示装置及びマスク

【課題】マスクの枚数を増やすことなく、ストレージキャパシタの電極間から半導体パターンを除去して高画質化を実現させる表示装置及びその製造方法を提供する。

【解決手段】本発明によるTFTパネルの製造では、半導体パターンとTFTのドレイン電極とを、同じマスクを利用したエッチングで同時にパターニングする。一方、画素電極の直下に形成される絶縁膜のパターニングには別のマスクを利用する。ドレイン電極を覆う絶縁膜の領域では、中央部の全体を感光させ、周辺部を半分の厚みまで感光させる。ストレージ電極の上方を覆う絶縁膜の領域は薄い一部を残して感光させる。ドレイン電極を覆う誘電膜をエッチングしてドレイン電極を露出させるとき、絶縁膜のその薄い一部がその下地の誘電膜を保護する。その後、絶縁膜のその薄い一部を画素電極の一部に置換し、保護された誘電膜を隔ててストレージ電極と対向させる。

(もっと読む)

半導体装置の製造方法

【課題】配線を設計通りの形状に形成することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板と、前記半導体基板の第1の面に位置する電極と、前記第1の面に設けられ、前記電極とオーバーラップする位置に開口部を有する絶縁膜と、を有する構造体を用意する工程と、前記絶縁膜の前記第1の面側の面とは反対側の第2の面に、樹脂突起を形成する工程と、前記電極および前記樹脂突起を覆う第1導電膜を前記第2の面に形成する工程と、前記第1導電膜の前記第2の面側の面とは反対側の第3の面に、前記第1導電膜の前記第3の面より反射率の低い第2導電膜を形成する工程と、前記第2導電膜の前記第3の面側の面とは反対側の第4の面に、フォトレジスト層を形成する工程と、前記フォトレジスト層の一部をマスク層で覆った状態で、前記フォトレジスト層を露光する工程と、前記フォトレジスト層を現像し、フォトレジストパターンを形成する工程と、前記フォトレジストパターンをマスクとして前記第1導電膜および前記第2導電膜をエッチングすることにより、前記第1導電膜から形成された配線であって、前記樹脂突起の少なくとも一部を覆い、かつ、前記電極と接続する前記配線を形成する工程と、を有する。

(もっと読む)

半導体装置

【課題】大面積化しても低消費電力を実現した半導体装置の構造およびその作製方法を提供する。

【解決手段】画面で使われる画素の薄膜トランジスタを作製する。その薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上に作製する。また、ソース配線と薄膜トランジスタをつなぐ配線と、画素電極と薄膜トランジスタをつなぐ配線を同一工程で作製する。

(もっと読む)

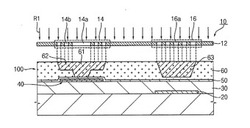

半導体集積回路装置およびその製造方法ならびにそれを用いた電子システム

【課題】再配線のランド部にバンプ電極が接続された半導体集積回路装置において、再配線と半田バンプとの接着強度を向上させる。

【解決手段】再配線20のランド部20Aは、再配線20を構成する5層の金属膜(バリアメタル膜13、シード膜14、Cu膜15、第1Ni膜16および第2Ni膜17)のうち、最上層の第2Ni膜17の面積が他の金属膜(バリアメタル膜13、シード膜14、Cu膜15、第1Ni膜16)の面積よりも大きくなるように構成され、この第2Ni膜17の表面に半田バンプ21が接続されている。そして、半田バンプ21の端部では、第2Ni膜17の直下にポリイミド樹脂膜22が形成されている。

(もっと読む)

半導体装置、製造方法、および電子機器

【課題】製造コストの低減を図ることができる。

【解決手段】シリコンウェハ31の上面側の内部にメタルパッド32が形成され、シリコンウェハ31の上面にガラスシール材33が積層され、メタルパッド32がシリコンウェハ31の上面に露出するようにシリコンウェハ31およびガラスシール材33に加工された開口部にストッパ層34が形成される。そして、シリコンウェハ31の下面からストッパ層34まで開口するように縦孔35が形成され、縦孔35の先端部においてストッパ層34を介してメタルパッド32に電気的に接続され、シリコンウェハ31の下面まで延在するようにメタルシード層37が形成される。本発明は、例えば、固体撮像装置に適用できる。

(もっと読む)

Ti合金バリアメタルを用いた配線膜および電極、並びにTi合金スパッタリングターゲット

【課題】ウエットエッチングによる加工性に優れた特性を有する新規な配線用膜を提供する。

【解決手段】表示装置またはタッチパネルセンサーの配線用膜であって、合金成分としてX群元素(Xは、希土類元素、Ge、Si、Sn、Hf、Zr、Mg、Ca、Sr、Al、Zn、Mn、Co、Fe、及びNiよりなる群から選択される少なくとも一種の元素)を3〜50原子%、および/または酸素を0.2〜3.0質量%含有し、残部Tiおよび不可避不純物からなるTi合金層と、純CuまたはCu合金からなる層とを含む2層以上の積層構造を有することに要旨を有する配線用膜。

(もっと読む)

光電変換装置、撮像システム及びその製造方法

【課題】 フローティングディフュージョン部の容量の増大を抑制することが可能な光電変換装置を提供する。

【解決手段】 光電変換素子と、フローティングディフュージョン部と、転送トランジスタと、増幅トランジスタとが配された半導体基板と、第1の配線層と、第2の配線層とを含む複数の配線層と、を有する光電変換装置において、転送トランジスタのゲート電極と、前記第2の配線層とがスタックコンタクト構造で接続されている。

(もっと読む)

半導体装置

【課題】小型化、薄型化、軽量化を実現した半導体装置の提供を課題とする。また、作製時間を短縮し、歩留まりを向上することができる半導体装置の作製方法の提供を課題とする。

【解決手段】トランジスタと、トランジスタ上に設けられた絶縁層と、絶縁層に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に電気的に接続された第1の導電層(ソース配線又はドレイン配線に相当)と、絶縁層及び第1の導電層上に設けられた第1の樹脂層と、第1の樹脂層に設けられた開口部を介して、第1の導電層に電気的に接続された導電性粒子を含む層と、第2の樹脂層及びアンテナとして機能する第2の導電層が設けられた基板とを有する。上記構成の半導体装置において、第2の導電層は、導電性粒子を含む層を介して、第1の導電層に電気的に接続されている。また、第2の樹脂層は、第1の樹脂層上に設けられている。

(もっと読む)

室温金属直接ボンディング

【課題】外からの圧力を用いることなく、低温または室温でウエーハーを貼り合わせる。

【解決手段】貼り合わされたデバイス構造であって、デバイスまたは回路に接続された第1の組の金属ボンディングパッドおよび第1の基板10上の金属ボンディングパッドに隣接する第1の非金属領域を有する第1の基板、デバイスまたは回路に接続された第1の組の金属ボンディングパッドに隣接する第2の組の金属ボンディングパッド、および第2の基板13上の金属ボンディングパッドに隣接する第2の非金属領域を有する第2の基板、および第2の非金属領域に対して第1の非金属領域を接触ボンディングさせることにより形成される第1と第2の組の金属ボンディングパッドの間の接触ボンディングされた界面を含むボンディングされたデバイス構造。第1と第2の基板の少なくとも一方は弾性的に変形され得る。

(もっと読む)

半導体装置及びその製造方法

【課題】再配線構造を有する半導体装置において、外部接続電極の接合性の低下、層間剥離、クラックの発生等を抑制して信頼性を向上する。

【解決手段】半導体装置50は、配線層絶縁膜3内に形成された信号配線1と、配線層絶縁膜3上に形成された絶縁膜6及び7と、絶縁膜6及び7内で且つ信号配線1上に形成された配線電極4と、絶縁膜6及び7内で且つ配線電極4上に形成された第1の金属層10aと、絶縁膜6及び7上に形成され、第1の金属層10aの上面に接続された金属配線10cと、金属配線10c上に形成された外部接続電極13aとを備える。更に、絶縁膜6及び7内で且つ外部接続電極13aの下方に形成され、金属配線10cの下面に接続された第2の金属層10bを備える。

(もっと読む)

配線形成方法、及び配線形成装置

【課題】絶縁層が積層された導電層に該絶縁層を貫通するカーボンナノチューブが接続される配線構造にて電気的特性を向上することのできる配線形成方法、及び該方法を用いる配線形成装置を提供する。

【解決手段】

下部配線層32に積層された絶縁層34を貫通するホール35に、その内表面の全体が含まれるように触媒層36,37を形成した後、ホール35の内部にシースShが形成され、且つホール35の内壁面35aに対するシースの厚さがホール35の底壁面35bに対するシースShの厚さよりも小さくなるようにプラズマを生成する。そして、ホール35の内壁面35aに形成された触媒層36,37をプラズマ中のスパッタ粒子Spによって除去した後、ホール35の底壁面35bに残された触媒層36,37を用いて該底壁面35bからカーボンナノチューブ38を形成する。

(もっと読む)

半導体装置、及びその製造方法

【課題】ピラーを確実に配置することが可能な半導体装置、及びその製造方法を提供する。

【解決手段】本発明の一態様にかかる半導体装置30は、内部回路領域20と、内部回路領域20の外側に設けられたI/O領域10と、を備える半導体チップ1と、半導体チップ1とフリップチップ接続されたパッケージ基板6と、半導体チップ1とパッケージ基板6との間に配置され、半導体チップ1の最上層配線層12に含まれる2本以上の接地配線12a上に形成されて、2本以上の接地配線12aを接続する導電性のピラー4と、を備えるものである。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の薄い抵抗体もつ抵抗素子を形成する際に、抵抗体の断線に対して強い抵抗素子を提供する。

【解決手段】バリアメタル膜とアルミ電極膜からなる積層電極の先端領域を単層のバリアメタル電極とし、並列するバリアメタル電極間に電気的に接続する抵抗体をリフトオフ法にて形成する。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

半導体装置の製造方法

【課題】製造工程の効率化とパッシベーション膜の剥離の抑制とが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、金を含む配線30a及び配線30bを形成する工程と、配線30a及び配線30bに接して、窒化シリコン膜32をプラズマ気相成長する工程と、窒化シリコン膜32の製膜レートよりも大きな製膜レートのもと、窒化シリコン膜32に接し、窒化シリコン膜32よりもシリコン組成比が小さい窒化シリコン膜22をプラズマ気相成長する工程と、を有する半導体装置の製造方法である。

(もっと読む)

連結導体及びこれを用いた半導体装置

【課題】トレンチゲートを有する半導体装置に関して、ゲートの取り出し抵抗の低減を図り、動作速度の高速化をはかる。

【解決手段】この半導体装置は、リードフレーム30のリード端子30Rの一端に連結導体15を介して電気的に接続されている。この連結導体は、Cu箔で構成され、本体部15Mと、リード端子30Rに当接し、リード端子30Rに接続されるリード接続部15Rと、トレンチMOSFET(チップ)のソースパッドに当接するフィンガー部15Fと、フィンガー部15Fの先端を空間部で一体化する連結部15Bとで構成されている。この連結導体を用いることで、第1の外部取り出し電極を構成するソース電極35s間に第2の外部取り出し電極としてのゲートパッド35gが伸張して形成されている場合にも、低抵抗で信頼性の高い実装が実現される。

(もっと読む)

半導体装置の製造方法、半導体装置、および電子機器

【課題】配線層の露出面において、ダイシングの工程等で水が接触することにより生じ、配線層の露出面における接合強度の低下や外観不良等の原因となる腐食の発生を抑制する。

【解決手段】半導体基板の一方の面側にて、標準電極電位が互いに異なる2種以上の金属を含む合金により形成された配線層を露出させる工程(パッドを開口する工程(S10))と、前記配線層の露出面を含む範囲に、N2/Arプラズマを照射するプラズマ処理を行う工程(N2/Arプラズマ処理を行う工程(S30))と、を含む方法を用いる。

(もっと読む)

成膜方法および記憶媒体

【課題】成膜原料としてコバルトカルボニルを用いてCo膜を成膜する場合に、下地との密着性を良好にすることができる成膜方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、処理容器1内に気体状のコバルトカルボニルを供給し、基板W上でコバルトカルボニルを熱分解させて基板W上にCo膜を成膜するにあたり、基板WのCo膜の下地が、Co膜との界面近傍に混合層を形成する材料で構成されており、基板Wの加熱温度を190〜300℃とする。

(もっと読む)

半導体装置

【課題】半導体装置におけるSM不良による信頼性や歩留りの低下を抑えることが可能な半導体装置を提供する。

【解決手段】半導体装置においては、第1の配線と、第1の配線と接続され、第1の配線より細幅の第2の配線と、一方の端部が、第1の配線と第2の配線の接続部の近傍で、第1の配線と接続され、他方の端部より局所的に細幅となる中間部を有する犠牲的配線と、を備える。

(もっと読む)

銅の光子誘起除去

【課題】基板から銅含有層の少なくとも一部を除去する方法を提供する。

【解決手段】第1反応チャンバ中で、銅含有表面層4の少なくとも一部を、ハロゲン化銅表面層5に変える工程と、第2反応チャンバ中で、光子含有雰囲気6に晒して、ハロゲン化銅表面層5の少なくとも一部を除去して、揮発性のハロゲン化銅生成物8の形成を始める工程とを含む。光子含有雰囲気6に晒す間に、この方法は、更に、第2反応チャンバから揮発性のハロゲン化銅生成物8を除去し、第2反応チャンバ中で揮発性のハロゲン化銅生成物8の飽和を避ける工程を含む。本発明の具体例にかかる方法は、銅含有層のパターニングに用いられる。例えば、本発明の具体例にかかる方法は、半導体デバイス中に銅含有相互接続構造を形成するのに使用される。

(もっと読む)

121 - 140 / 1,884

[ Back to top ]