Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

1,841 - 1,860 / 2,805

制御された気孔を形成するための材料及び方法

【課題】基材の内部に空隙を形成するための方法を提供する。

【解決手段】基材を用意する工程;少なくとも1つの犠牲材料前駆体の堆積によって犠牲材料を堆積する工程;複合層を堆積する工程;該複合層中のポロゲン材料を除去して多孔質層を形成する工程;及び積層基材を除去媒体と接触させて前記犠牲材料を実質的に除去し、前記基材の内部に空隙を与える工程を含み、前記少なくとも1つの犠牲材料前駆体が、有機ポロゲン、シリコン、極性溶媒に可溶な金属酸化物、及びそれらの混合物からなる群より選択される方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】ボッシュプロセスを利用して形成されたビアホールを有する半導体装置の製造方法において、ビアホール内での均一な成膜を達成することを目的とする。

【解決手段】マスク層2をマスクとし、ボッシュプロセスを利用して半導体基板1の一方の面から他方の面方向へエッチングし、当該半導体基板1の所定領域を貫通するビアホール3を形成する。次に、マスク層2を除去する。次に、ドライエッチング法によりスキャロップ形状4を除去し、ビアホール3の内壁面を平坦化させる。続いて、ビアホール3内に絶縁膜やバリア層などを均一に成膜する。

(もっと読む)

半導体装置の製造方法

【課題】チタン/窒化チタン積層膜上にアルミニウム膜が形成されたアルミニウム配線を有する半導体製品の製造歩留まりを向上させることのできる技術を提供する。

【解決手段】バリアメタル成膜用のチャンバ65において、チャンバ65内に窒素を含まない不活性ガスを導入してスパッタリングを行い、シャッタ上にチタン膜を堆積する工程と、シャッタをチャンバ65内に備わる格納場所へ移動させた後、半導体ウエハSWをチャンバ65内に設置する工程と、チャンバ65内に窒素を含まない不活性ガスを導入して半導体ウエハSWの主面上にチタン膜を堆積する工程と、チャンバ65内に窒素を含む不活性ガスを導入してスパッタリングを行い、チタン膜上に窒化チタン膜を堆積する工程と、アルミニウム成膜用チャンバ66において、チャンバ66内に不活性ガスを導入してスパッタリングを行い、窒化チタン膜上にアルミニウム膜を堆積する工程とを含む。

(もっと読む)

スパッタリング方法

【課題】 アスペクト比4以上のホールの内面にボトムカバレッジ率よく成膜を行えるようにする。

【解決手段】 チタン等の金属製のターゲット2をスパッタして基板50に所定の薄膜を作成するスパッタチャンバー内に所定のガスを導入するガス導入手段4は、ターゲット2から放出されるスパッタ粒子に反応して、ホール500の側面501に対する付着性がスパッタ粒子単体の場合よりもより低く且つホール500の底面502において解離可能な化合物を生成する水素等の反応性ガスを導入することが可能である。狭いホール500の底面502まで効率よくスパッタ粒子が到達できるので、ホール500の底面502での膜堆積が促進され、ボトムカバレッジ率が向上する。

(もっと読む)

フラットパネルディスプレイ装置及びその製造方法

【課題】低い配線抵抗,熱的安定性を有し,画素電極との接触抵抗特性が改善されたフラットパネルディスプレイ装置及びその製造方法を提供する。

【解決手段】フラットパネルディスプレイ装置は、基板100と,該基板100上に順次積層された耐熱性金属膜パターン131a,アルミニウム系金属膜パターン131c,およびキャッピング金属膜パターン131dを備えるソース/ドレイン電極131と,を含み,耐熱性金属膜パターン131aは,500Å以下の厚さを有し,耐熱性金属膜パターン131aとアルミニウム系金属膜パターン131cとの間には,拡散防止膜パターン131bがさらに含まれる

(もっと読む)

半導体装置及びその製造方法

【課題】ビアホールを有する半導体装置及びその製造方法において、ビアホール内におけるバリア層の被覆不足防止とビア抵抗を制御することの両者を同時に達成することを目的とする。

【解決手段】その表面上にパッド電極3を有する半導体基板1を準備する。次に、半導体基板1の裏面から表面方向にエッチングし、パッド電極3を露出させるビアホール8を形成する。次に、スパッタリング法またはPVD法、及び逆スパッタリング(エッチング)によりビアホール8内に第1のバリア層11を形成する。この逆スパッタリングによりビアホール8底部のバリア層が除去され、パッド電極3が露出される。次に、ビアホール内で露出したパッド電極3上に第2のバリア層12を形成する。第2のバリア層12の膜厚のみを調節することでビア抵抗を制御する。

(もっと読む)

半導体装置の製造方法

【課題】半導体ウェハの端部に形成された膜を除去することにより発生した異物を、洗浄工程において、半導体ウェハ上から充分に除去することができる技術を提供する。

【解決手段】半導体ウェハ1上に酸化シリコン膜よりも誘電率の低い疎水性のSiOC膜8を形成する。そして、SiOC膜8上に親水性の酸化シリコン膜9を形成する。酸化シリコン膜9は、TEOSを原料としたCVD法で形成することができる。次に、半導体ウェハ1の端部1Aに形成されている積層膜を、たとえば研磨ドラムを用いた研磨によって除去する。続いて、半導体ウェハ1の端部1Aに形成されている膜を除去することにより発生した異物を洗浄液15で除去する。このとき、異物は、親水性の酸化シリコン膜上に付着しているため、洗浄液15によって充分に除去される。

(もっと読む)

デュアル配線型集積回路チップ

【課題】 デュアル配線型集積回路チップ及びその製造方法を提供する。

【解決手段】 両面に配線レベルを有する半導体デバイス、及び、両面のデバイス及び配線レベルへのコンタクトを有する半導体構造体を製造する方法を提供する。本方法は、シリコン・オン・インシュレータ基板上のデバイスへの第1コンタクトと、第1コンタクトへの第1側面上の配線レベルとを有するデバイスを製造するステップと、下部シリコン層を除去して埋込み酸化物層を露出させるステップと、埋込み酸化物層を貫通してデバイスへの第2コンタクトを形成するステップと、埋込み酸化物層の上に第2コンタクトへの配線レベルを形成するステップとを含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体記憶装置のキャパシタ形成に際して、下部電極に接続するランディングパッドを簡易に形成する半導体装置の製造方法を提供する。

【解決手段】絶縁膜のコンタクト孔内に金属プラグを形成した後に、選択CVD技術を用いて、タングステン膜を金属プラグと自己整合的に成長することにより、金属プラグに対応してランディングパッドを形成する。その上に下部電極、容量絶縁膜、及び、上部電極を順次に形成する。

(もっと読む)

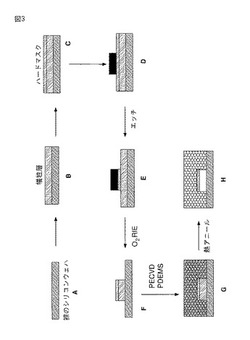

固体及び気体誘電体の組み合わせによって離間された相互接続した導電性配線及びビアを含む多層相互接続構造を形成する方法、及び、空隙を含む複数レベルの相互接続構造(空隙を含む多層相互接続構造及びその製造方法)

【課題】本発明は、空隙を含む複数レベルの相互接続構造及びその製造方法を提供する。

【解決手段】空隙を含む複数レベルの相互接続構造は、散在したライン・レベル及びビア・レベルの集合を含み、ビア・レベルは、1つ以上の誘電体層に埋め込まれた導電性ビアを含み、ビア・レベルの誘電体層は、隣接レベルのライン機構の上下に位置する固体であり、ライン機構の間でミシン目が入れられている。ライン・レベルは導電性ラインと、空隙を含む誘電体とを含む。導電性接点を含み、有孔誘電体層内に充填することによって形成された固体誘電性ブリッジ層は、散在したライン及びビア・レベルの集合上に配置されている。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト抵抗の安定したビット線コンタクトプラグを有するスタックトセルを備えた半導体装置、およびその製造方法を提供することにある。

【解決手段】第1の層間絶縁膜13には、スタックトキャパシタ16のストレージノード19bに接続するストレージノードコンタクトプラグ14b、及びビット線拡散層に接続する第1のビット線コンタクトプラグ15bが形成され、第2の層間絶縁膜18内には、スタックトキャパシタ16、及び第1のビット線コンタクトプラグ15bに接続する第2のビット線コンタクトプラグ20bが形成され、第3の層間絶縁膜24内には、スタックトキャパシタ16のプレート電極22に接続するセルプレートコンタクトプラグ25b、及び第2のビット線コンタクトプラグ20bに接続する第3のビット線コンタクトプラグ26bが形成されている。

(もっと読む)

半導体装置および電気ヒューズの切断方法

【課題】切断された電気ヒューズの切断状態を良好に保つ。

【解決手段】半導体装置100は、半導体基板(不図示)上に形成され、導電体により構成された電気ヒューズ200を含む。電気ヒューズ200は、切断前状態において、それぞれ異なる層に形成された上層配線134と、上層配線134に接続されたビア128と、ビア128に接続された下層配線122とを含み、切断状態において、導電体が上層配線134から外方に流出してなる流出部142が形成されるとともに、下層配線122とビア128との間に空隙部140が形成される。

(もっと読む)

半導体装置の製造方法

【課題】シード膜の消失に起因する埋め込み不良の発生を防止し、高信頼性を確保できる配線を備えた半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜に形成された凹部にシード膜を形成し、当該シード膜を電極とした電解めっきにより当該凹部を埋め込む厚膜を形成する半導体装置の製造方法において、シード膜形成後から電解めっき開始までの間の上限時間を、凹部へのシード膜の形成状態に基づいて制限する。すなわち、凹部のアスペクト比が高い程、上限時間を短く設定する。これにより、めっき処理の過程で凹部内にボイドが形成されることを抑制し、高い信頼性を有する配線を形成することができる。また、シード膜形成後から電解めっき開始までの間、半導体基板を不活性ガス雰囲気に維持してもよい。

(もっと読む)

半導体装置および電気ヒューズの切断方法

【課題】電気ヒューズが中途半端に切断されると、切断動作をリトライできない。

【解決手段】電気ヒューズ200は、半導体基板(不図示)上に形成された第1の配線300および第2の配線302と、半導体基板上に形成されるとともに一端が第1の配線300に接続して設けられ、第2の配線302を第1の配線300から電気的に切断するヒューズリンク304と、半導体基板上に形成され、第1の配線300の一端および他端にそれぞれ設けられたヒューズリンク切断用の電流流入端子306および電流流出端子308と、を含む。

(もっと読む)

半導体基体中に形成されたスパイラル形状インダクタ及びそのインダクタを形成するための方法

【課題】 半導体基体中に高いQ値のスパイラル形状インダクタを形成する。

【解決手段】 能動デバイス領域からなる半導体基体上に形成されたインダクタであって、インダクタは半導体基体に積層される誘電体層上に形成された導電線からなる。導電線は、一つの実施例においては平面スパイラル形状である所望の形状にパターン成形され、エッチング加工される。インダクタの下の基体領域はインダクタのQ値を上げるために除去される。

(もっと読む)

半導体装置の製造方法

【課題】 銅溝配線層とその上に形成されたアルミニウム配線とを含む多層配線を備えた不揮発性半導体メモリのコスト増加を抑制できる半導体装置の製造方法を提供すること。

【解決手段】 半導体装置の製造方法は、銅溝配線層4,5上に銅拡散防止膜6を形成する工程と、銅拡散防止膜6に開口部をレーザーアブレーションにより形成する工程とを含み、前記開口部は、銅溝配線層4,5上にアルミニウム配線を形成するためのリソグラフィ工程で使用される位置合わせ用マークが形成される領域に対応することを特徴とする。

(もっと読む)

100%又はそれより大きい段差被覆性を有する相互接続部金属化プロセス

【課題】 構造底部のバリア材料厚と比べると、構造側壁においてより厚いバリア材料被覆範囲を有する相互接続構造体、及び、そのような相互接続構造体を製造する方法を提供すること。

【解決手段】 構造底部のバリア材料厚と比べると、構造側壁においてより厚いバリア材料被覆範囲を有する相互接続構造体、及び、そのような相互接続構造体を製造する方法が提供される。本発明の相互接続構造体は、従来のPVDプロセス、従来のイオン化プラズマ堆積、CVD、又はALDによってバリア材料が形成される従来技術の相互接続構造体と比べると、半導体業界のための改善された技術拡張性を有する。本発明によると、構造底部のバリア材料厚(ht)より厚い、構造側壁のバリア材料厚(wt)を有する相互接続構造体が提供される。すなわち、本発明の相互接続構造体において、wt/ht比は、100%に等しいか又はそれより大きい。

(もっと読む)

半導体装置

【課題】多層配線部における最も上の層間絶縁膜に形成されたヒューズと、該ヒューズを覆う保護部と、多層配線部上に形成されたMIM素子とを備え、保護部の厚さを制御し易い半導体装置を得ること。

【解決手段】半導体基板10と、この半導体基板に形成された回路素子20,30と、半導体基板上に積層された多層配線部50と、多層配線部における最も上の層間絶縁膜45に設けられたヒューズ55と、ヒューズ上に設けられた保護部60と、多層配線部上に形成されたMIM素子70と、多層配線部上に形成された最外層間絶縁膜80とを備えた半導体装置100を作製するにあたり、多層配線部における最も上の層間絶縁膜に設けられたトレンチT3 にMIM素子の下部電極62を埋め込み、その上に電気絶縁膜64と上部電極66とをこの順番で積層することでMIM素子を構成し、このMIM素子を覆うようにして最外層間絶縁膜を形成する。

(もっと読む)

半導体装置

【課題】埋め込み特性や膜特性に優れたシリコン酸化膜を高アスペクト比を有する凹部に形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法は、半導体基板の主表面側の下地領域 350に形成された凹部351内全体にシリコン窒化膜352を形成する工程と、前記シリコン窒化膜352を酸化して該シリコン窒化膜352をシリコン酸化膜353に変換することにより、前記凹部内全体に絶縁領域を形成する工程とを有することを特徴とする。

(もっと読む)

基板処理方法、半導体装置の製造方法および基板処理装置

【課題】半導体装置の製造工程において、金属配線に形成される酸化膜を、安定に効率的に除去することを可能とする。

【解決手段】絶縁膜と金属層が形成された被処理基板を処理する基板処理装置であって、前記被処理基板を保持すると共に該被処理基板を加熱する保持台と、前記保持台を内部に備えた処理容器と、前記処理容器内に、処理ガスを供給するガス供給部と、前記処理容器内からガスを排気するガス排出部と、を備え、前記処理ガスは、無水カルボン酸を含むことを特徴とする基板処理装置。

(もっと読む)

1,841 - 1,860 / 2,805

[ Back to top ]