Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

1,881 - 1,900 / 2,805

半導体装置

【課題】埋め込み特性や膜特性に優れたシリコン酸化膜を高アスペクト比を有する凹部に形成することが可能な半導体装置を提供すること。

【解決手段】半導体装置は、半導体基板の主表面側に形成された凹部を有する下地領域と、前記下地領域の凹部内全体に埋め込まれた塩素を含有するシリコン酸化膜とを有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】抵抗体とMOSトランジスタを同一基板に備える、半導体装置を製造するにあたり、コンタクトの導通不良を防ぐとともに、シリコン基板への配線金属の溶出を防ぐ。

【解決手段】先ず、下地20を用意する。次に、下地上にシリコン酸化膜30を形成する。次に、シリコン酸化膜30上にシリコン窒化膜50を形成する。次に、シリコン窒化膜上に層間絶縁膜60を形成する。次に、シリコン酸化膜、シリコン窒化膜及び層間絶縁膜の積層体65を貫通するコンタクトホール70を設ける。ここで、シリコン酸化膜の厚みを、32〜48nmの範囲内の値とする。

(もっと読む)

絶縁膜形成用組成物及び半導体装置の製造方法

【課題】誘電率が低く機械的強度が高い多孔質の絶縁膜を有する半導体装置の製造方法、並びにこのような多孔質絶縁膜の形成に好適な絶縁膜形成用組成物を提供する。

【解決手段】基板10上に、多孔質の第1の絶縁膜38を形成する工程と、第1の絶縁膜38上にSi−CH3結合を30〜90%の割合で含有するシリコン化合物を含む第2の絶縁膜40を形成する工程と、第1の絶縁膜38上に第2の絶縁膜40が形成された状態で紫外線を照射し、第1の絶縁膜38を硬化させる工程とを有する。これにより、CH3基を脱離する波長域を有する紫外線が第2の絶縁膜により十分に吸収され、第1の絶縁膜では紫外線キュアによる高強度化が優先的に進行するので、第2の絶縁膜の誘電率を増加することなく膜密度を向上することができる。

(もっと読む)

半導体装置の製造方法

【課題】支持体を用いた半導体装置の製造方法において、製造工程を複雑化させることなく、信頼性及び歩留まりの向上を図る。

【解決手段】支持体8と半導体基板1とを貼りつける工程の前に、半導体基板1の表面を一部除去し、ダイシングラインDLに対応する位置に沿って溝部5を形成する。一連の加工をした後、ダイシングブレードやドライエッチングによって保護層20,第2の絶縁膜11,半導体基板1を順に除去して開口部22(溶解剤供給経路)を形成する。開口部22はその底部で溝部5と連通し、接着層7が当該開口部22内において一部露出される。この時点で多数の半導体装置は個々の半導体チップに分割される。次に、開口部22を介して溶解剤(例えばアルコールやアセトン)を露出された接着層7に対して供給し、接着力を徐々に低下させることで半導体基板1から支持体8を剥離除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の実装時の熱応力による配線層や導電層の剥がれを抑制し、電気的な断線を防止した、高性能かつ信頼性の高い半導体装置及びその効率的な製造方法の提供。

【解決手段】本発明の半導体装置は、半導体基板(例えばシリコンウェハー10)と、該半導体基板10上に形成された配線層14と、該配線層上に形成された第一の導電層15と、該第一の導電層上に形成された層間絶縁膜16と、前記第一の導電層15と導通可能に、前記層間絶縁膜16上に形成された第二の導電層17とを有する。第二の導電層上にはバンプが形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】配線構造をパターン形成した際に発生した不要な残存物を容易且つ確実に除去し、信頼性の高い半導体装置を実現する。

【解決手段】配線膜1上に、Al2O3(アルミナ)、SiON、Al窒素酸化物、Ta酸化物、及びTi酸化物よりなる群から選ばれた少なくとも一種の材料からなる犠牲剥離膜40を形成し、第1の配線45をパターン形成した後、フッ化アンモニウム、アミド、有機酸、有機酸塩類、及び水を含有する薬液を用いて、ウェットエッチングにより残存物50を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】CuとAlが反応することによる配線抵抗の上昇や、Cuの隆起によるCu配線の信頼性の低下を抑制できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板11上に形成される絶縁膜12と、この絶縁膜の表面に形成された溝内に、第1のバリアメタル層を介在して埋め込まれるCu配線M1A,M1Bと、上記絶縁膜、第1のバリアメタル層及びCu配線上に形成され、上記Cu配線上に対応する位置に開口17A,17Bを有する層間絶縁膜16と、上記層間絶縁膜の開口内において上記Cu配線と電気的に接続されるAl配線20と、少なくとも上記Cu配線とAl配線との間に介在され、CuとAlとの反応を防止するための第2のバリアメタル層18と、上記第2のバリアメタル層に対するAlの流動性を上げるための第3のバリアメタル層19とを含む積層膜とを備えている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】孔の中や溝の中などに金属材料を埋め込んだ際のカバレッジ性を向上させること

ができる半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体装置91の製造方法は、まず、基板51上に低透過率のレジスト膜2

2を形成する。次に、ホログラフィック露光装置11を用いてレジスト膜22を露光及び

現像する。これにより、ホログラフィック露光装置11側が広いテーパ状の開口孔62a

を有する第1レジストパターン61aを形成することができる。この第1レジストパター

ン61aをマスクとしてシリコン酸化膜53を異方性にエッチングするとともに、第1レ

ジストパターン61aも異方性にエッチングする。これにより、第1レジストパターン6

1aの形状から第2レジストパターン61bの形状にすることができ、口元が広いテーパ

状のコンタクトホールを形成することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】配線用溝の深さ制御が容易で、誘電率が低く、かつリーク電流が増加しにくい多孔質の絶縁層を有する半導体装置およびその製造方法を提供する。

【解決手段】絶縁層5は、半導体基板1上に形成され、かつビア用貫通孔5aを有している。多孔質シリカ層6は、ビア用貫通孔5aに連通する配線用溝6aを有し、かつ絶縁層5上に接して形成されている。導電層8は、ビア用貫通孔5a内および配線用溝6a内に形成されている。絶縁層5は、炭素と水素と酸素とシリコンとを含み、かつFT−IRにより測定したときに1274nm付近にSi−CH3結合に起因する吸収ピークを有する材質よりなっている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置に記憶された情報のセキュリティ性を向上させる技術を提供する。

【解決手段】半導体基板20上に多層配線層を形成する。そして、多層配線層のうち最上層配線層に配線42を形成する。配線42上に酸化シリコン膜43、有色薄膜44および酸化シリコン膜45を順次形成し、酸化シリコン膜45上に表面保護膜となる窒化シリコン膜46を形成する。すなわち、本発明の特徴は、最上層配線層を構成する配線42と表面保護膜となる窒化シリコン膜46の間に有色薄膜44を形成する。この有色薄膜44は、可視光および特定波長域のレーザ光を減衰させる機能を有し、例えば、酸化コバルトを含有する酸化シリコン膜より形成する。

(もっと読む)

eヒューズおよびeヒューズの製造方法

【課題】eヒューズにおいて、バックフロー効果を回避すること。

【解決手段】斜線で示した部分がシリサイド(領域)1であり、シリサイド領域1は、シリサイド領域1は、第1コンタクト領域7と第1コンタクト領域7よりも長手方向の幅が細いヒューズ領域8と、ヒューズ領域8を挟んで第1コンタクト領域7と対向して設けられた第2コンタクト領域9とから構成され、第2コンタクト領域9のヒューズ領域8と接している側とは反対側に隣接した位置(非ヒューズ接続側)などに非シリサイド領域2を設ける。

(もっと読む)

半導体素子の製造方法

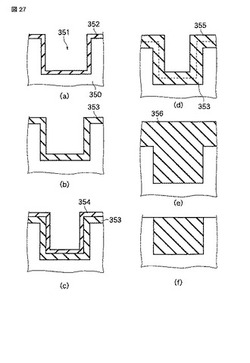

【課題】理想的なトレンチコンタクト形成によってコンタクトの低抵抗化と製造の低コスト化を実現する半導体素子の製造方法を提供する。

【解決手段】半導体装置の製造方法においては、半導体基板上に中間絶縁膜20を形成する工程と;前記中間絶縁膜上に第1の層22を形成する工程と;前記中間絶縁膜及び第1の層にコンタクトホールを形成する工程と;前記第1の層をハードマスクとして用いて、前記半導体基板に前記コンタクトホールと連通するトレンチ40を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】生産性を落とすことなく、上層の配線と下層の導電領域とを接続することができるタングステンプラグ形成工程を有した半導体の製造方法を提供する。

【解決手段】導電性領域が形成された半導体基板上に、層間絶縁膜を形成する層間絶縁膜形成工程と、前記導電性領域に達する接続孔を、前記層間絶縁膜に形成する接続孔形成工程と、前記接続孔に、タングステン膜を埋め込むタングステンプラグ形成工程とを有する半導体装置の製造方法において、タングステンプラグ形成工程は、第1の埋め込みステップと、該第1の埋め込みステップの後の工程で、かつ前記第1の埋め込みステップよりも成膜速度が速い第2の埋め込みステップとを備えていることを特徴とする。

(もっと読む)

表面疎水化用組成物、表面疎水化方法、および半導体装置

【課題】層の表面をより簡便にかつ効果的に疎水化することができ、かつ、層のより深い領域を疎水化することができる表面疎水化用組成物、表面疎水化方法、および該表面疎水化方法が施された半導体装置を提供する。

【解決手段】表面疎水化用組成物は、(A)下記一般式(1)で表される化合物および下記一般式(2)で表される化合物の群から選ばれた少なくとも1種の化合物と、(B)沸点が30〜350℃である溶媒とを含む。

【化1】

・・・・・(1)

【化2】

・・・・・(2)

(もっと読む)

電着されたコンタクトを形成する構造体及び方法

【課題】 既存のCVDタングステン・プラグ金属化技術と比べて減少したプラグ抵抗を示し得る構造体を提供すること。

【解決手段】 基板上に配置されたキャビティを有するパターン形成された誘電体層と、キャビティの底部に配置された、コバルト及び/又はニッケルのようなシリサイド又はゲルニウム化物層と、誘電体層の上部及びキャビティの内部に配置され、前記底部においてシリサイド又はゲルニウム化物層に接触する、Ti又はTi/TiNを含むコンタクト層と、コンタクト層の上部及びキャビティの内部に配置された拡散バリア層と、バリア層の上部に配置された、めっきのための随意的なシード層と、ビア内の金属充填層とを含むコンタクト金属(メタラジ)構造体が、その製造方法と共に提供される。金属充填層は、銅、ロジウム、ルテニウム、イリジウム、モリブデン、金、銀、ニッケル、コバルト、カドミウム、亜鉛、及びこれらの合金から成る群から選択される少なくとも1つの部材を用いて電着される。金属充填層がロジウム、ルテニウム、又はイリジウムである場合、金属充填物と誘電体との間に有効な拡散バリア層を必要としない。バリア層が、ルテニウム、ロジウム、又はイリジウムのようにめっき可能である場合、シード層を必要としない。

(もっと読む)

半導体装置およびその製造方法

【課題】配線を低抵抗化するとともに、配線材料と層間絶縁膜との密着性を向上させる。

【解決手段】半導体装置100は、基板(不図示)上に形成された第1の銅含有導電膜124と、第1の銅含有導電膜124上に形成され、第1の銅含有導電膜124に達する凹部が形成された絶縁膜(108、110、112、114)と、これら絶縁膜の凹部側壁を覆うように形成され、銅の拡散を防止する材料により構成された第2のバリア絶縁膜128と、凹部の底面で第1の銅含有導電膜124に接するとともに凹部の側壁で第2のバリア絶縁膜128に接して凹部内壁を覆うように形成された銅と銅とは異なる異種元素との第2の接着合金膜130と、銅を主成分として含み、第2の接着合金膜130上に第2の接着合金膜130に接して凹部を埋め込んで形成された第2の銅含有導電膜132とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】従来の半導体装置では、微細化したコンタクトホールでの安定したコンタクト抵抗と、信頼性の高いアルミニウム配線とを両立することはできないという課題があった。

【解決手段】本発明の半導体装置は、コンタクトホールの内部と配線形成部とに、配向の異なるバリア層を有する。このバリア層は、チタン膜と窒化チタン膜とチタン膜との3層構造であって、配線形成部に形成するバリア層の(002)配向性がコンタクトホールの内部のバリア層の(002)配向性よりも高い。このような構成とすることによって、安定したコンタクト特性と、高エレクトロマイグレーション耐性とを有する半導体装置を構成することができる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 自己整合的に基板のコンタクト部をユニバーサルコンタクトホール内に形成することができる半導体装置の製造方法及びこの製造方法により形成された半導体装置を提供する。

【解決手段】 層間絶縁膜9にソース領域3が露出されたユニバーサルコンタクトホール7を開口し、ユニバーサルコンタクトホール7から半導体基板100に第1導電型(P型)不純物を注入してユニバーサルコンタクトホール7の底面中央に露出するソース領域3を基板領域と同じ導電型の第1導電型領域5にする。ユニバーサルコンタクト13はユニバーサルコンタクトホール7底面周縁部に露出するソース領域3に電気的に接続されている。基板領域とソース領域のコンタクトの位置関係が一定となりソース領域における電流の不均衡が解消される。

(もっと読む)

金属の還元方法、多層配線及びその製造方法、並びに、半導体装置及びその製造方法

【課題】耐酸化した金属の確実かつ効率的な還元方法、該金属の還元方法を用い、配線間の寄生容量が低減可能で配線抵抗が低い多層配線、及びその製造方法、並びに、半導体装置及びその製造方法の提供。

【解決手段】本発明の金属の還元方法は、カルボン酸エステル化合物を少なくとも含む蒸気を、水蒸気により加水分解させ、酸化金属を還元する。また、本発明の多層配線の製造方法は、被加工表面に、被膜形成工程と、配線形成工程と、本発明の金属の還元方法を用いた還元工程とを少なくとも含む。本発明の多層配線は、本発明の多層配線の製造方法により形成される。本発明の半導体の製造方法は、被膜形成工程と、パターニング工程と、配線形成工程と、本発明の金属の還元方法を用いた還元工程とを少なくとも含む。本発明の半導体は、本発明の多層配線を少なくとも有し、本発明の半導体の製造方法により形成される。

(もっと読む)

電解めっき装置及び電解めっき方法

【課題】銅と同等以上の抵抗率の導電層(シード層)を有した基板に対して、より均一な膜厚で、全面に亘って膜質の良好なめっき膜を成膜できるようにする。

【解決手段】基板保持部で保持した基板表面の周縁部に当接して該周縁部をシールするシール材90と、基板保持部で保持した基板の表面に形成した導電層に接触して通電させるカソード接点88と、内部にめっき液に浸漬させるアノード98を収納し、基板保持部で保持した基板と対向する開口端部に多孔質構造体110を配置してめっき液室100を区画形成したハウジング94を有し、めっき液室100は仕切り板150で複数の部屋154a,154bに仕切られ、アノード98は複数に分割された分割アノード98a,98bから構成されて、各分割アノード98a,98bはめっき液室100の各部屋154a,154bの内部に独立しためっき電流が流せるように配置されている。

(もっと読む)

1,881 - 1,900 / 2,805

[ Back to top ]