Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

1,961 - 1,980 / 2,805

半導体装置の製造方法

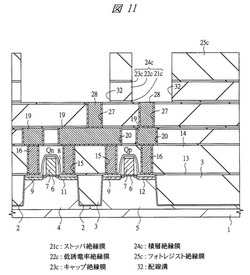

【課題】低誘電率絶縁膜を用いた多層配線構造の配線の特性を向上する。

【解決手段】まず、フォトレジスト膜25cをマスクとしてストッパ絶縁膜21c/低誘電率絶縁膜22c/キャップ絶縁膜23cからなる積層絶縁膜24c中のストッパ絶縁膜21cを含めた状態までドライエッチングすることによって、積層絶縁膜24cに配線溝32を形成する。次いで、還元性プラズマ処理によって、フォトレジスト膜25cを除去した後、配線溝32に配線を形成する。

(もっと読む)

半導体デバイスで用いられるキャパシタとその製造方法

【課題】従来技術にかかる構造、および製造プロセスの欠点を回避するキャパシタ構造と、その製造方法を提供する。

【解決手段】半導体ウェハの基板上に形成された食刻相互接続構造(damascene)を有する半導体デバイスで使用される本発明のキャパシタは、食刻相互接続構造の一部を含む第1キャパシタ電極164と、食刻相互接続構造の上に形成され、パッシベーション層として機能する絶縁層166と、絶縁層の少なくとも一部の上に形成された導電層を含む第2キャパシタ電極168とを有する。

(もっと読む)

露光光遮蔽膜形成用材料、多層配線及びその製造方法、並びに半導体装置

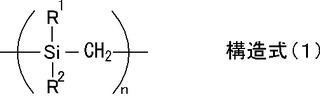

【課題】多層配線、半導体装置等に好適に用いられ、露光光、例えば紫外線の吸収性が高い露光光遮蔽膜形成用材料等の提供。

【解決手段】露光光遮蔽膜形成用材料は、構造式(1)で表されるシリコン化合物及び構造式(2)で表されるシリコン化合物のいずれかを含んでなり、R1及びR2のいずれかが露光光を吸収可能な置換基で置換されている。

(R1、R2及びR3は水素原子並びにアルキル基、アルケニル基、シクロアルキル基及びアリール基のいずれかを表す。nは2以上の整数を表す。)

(もっと読む)

半導体素子及びその製造方法

【課題】電気的な短絡を防止するコンタクトを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板100上に形成された下部導電層124、下部導電層124を覆う層間絶縁膜150、層間絶縁膜150内に形成されるコンタクトホール160〜164、及びコンタクトホール160〜164を埋めるコンタクトプラグ170〜174を備える。コンタクトホール160〜164は、下部導電層124の上面を露出させるとともに、上断面が楕円形である。そして、コンタクトホール160〜164は、上断面の短軸方向に比べて長軸方向を近接して配列される。これにより、ボーイングによるコンタクトホール160〜164間の電気的な短絡を防止でき、素子の誤動作を減少させて性能を向上させて信頼性を高めることができる。

(もっと読む)

微細パターンの形成方法

【課題】 導体回路素子内の微細配線形成方法として使用されているいわゆるダマシン法ないしデュアルダマシン法にも適用し得るナノメータオーダーの微細パターンの形成方法を提供すること。

【解決手段】 本発明の微細パターンの形成方法は、基板上に設けられた絶縁膜に形成された溝及び孔の少なくとも一方を、二酸化炭素及び不活性ガスの少なくとも一方、めっき液及び界面活性剤を含む超臨界流体又は亜臨界流体を用いためっき法により所定の金属で埋めることを特徴とする。この場合、めっき液として従来から使用されている電解めっき液や無電解めっき液を使用することができ、また、本発明の微細パターンの形成方法を実施する際には、脱脂部A、酸洗部B、触媒化部C及びめっき部Dを備える表面処理装置10を使用し得る。

(もっと読む)

成膜方法、プラズマ成膜装置及び記憶媒体

【課題】メッキ処理を用いることなくプラズマスパッタだけで微細な凹部を金属によりボイドを発生させることなく埋め込むことができる成膜方法を提供する。

【解決手段】処理容器24内でプラズマにより金属ターゲット70をイオン化させて金属イオンを含む金属粒子を載置台34上に載置した被処理体Wにバイアス電力により引き込んで凹部4を埋め込むようにした成膜方法において、バイアス電力を、被処理体の金属ターゲットに対する対向面に関して、金属粒子による成膜レートとプラズマガスによるスパッタエッチングのエッチングレートとが略均衡するような状態になるように設定して凹部内に金属膜を形成する成膜工程と、金属粒子の供給を停止した状態で被処理体を金属膜の表面拡散が生ずる所定の温度範囲に加熱維持することにより金属膜の原子を凹部の底部に向けて移動させる拡散工程とを交互に複数回繰り返す。

(もっと読む)

プラズマに面する壁の水蒸気不動態化

水素ラジカルでバイアホールにバリヤ層をコーティングする前に、低k誘電体の水素プラズマ洗浄に特に有用なチャンバ不動態化法が遠隔プラズマ源(60)から提供される。各ウエハについて、水素プラズマの点火前に遠隔プラズマ源を通過した水蒸気(86)(又はプラズマ対向壁上により多く化学吸収された他のガス)でチャンバが不動態化される。遠隔プラズマ源のアルミナや石英部分のような壁(78、79)上に水蒸気が吸収され、水素プラズマの生成で壁を保護するのに充分な長さを耐える保護単層を形成する。それによって、特にアルミナのような誘電体の、プラズマ対向壁がエッチングから保護される (もっと読む)

半導体装置およびその製造方法

【課題】自然酸化膜下に位置する半導体基板や金属膜がオーバエッチングされず、位置によって厚みの異なる自然酸化膜を良好に除去できる半導体装置の提供。

【解決手段】半導体基板1の主表面に、第1導電型の第1不純物を導入して第1不純物領域3、4を形成する工程と、第2導電型の第2不純物を導入して第2不純物領域33、34を形成する工程と、第1不純物領域1上に第1ニッケルシリサイド膜21、22を形成すると共に、第2不純物領域33、34上に第2ニッケルシリサイド膜41、42を形成する工程と、NH3ガスと水素元素を含むガスとが混合された混合ガスを用いて、第1、第2ニッケルシリサイド膜21、22上に形成された酸化膜を除去する工程と、酸化膜を除去した状態で、第1ニッケルシリサイド膜21、22上に第1導電膜6a、7a、を形成すると共に、第2ニッケルシリサイド膜上に第2導電膜36a、37aを形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】配線の接続抵抗を低減し、かつ、接続信頼性の向上を図ることができる半導体装置の製造方法を提供する。

【解決手段】本実施形態に係る半導体装置の製造方法は、第1導電層4が形成された基板1上に、層間絶縁膜6を形成する工程と、層間絶縁膜6に第1導電層4を露出させる接続孔9を形成する工程と、接続孔9に露出した第1導電層4の表面を酸化して、酸化膜10を形成する工程と、酸化膜10を選択的に除去して、第1導電層4の表面を窪ませる工程と、接続孔9内に第2導電層を埋め込む工程とを有する。

(もっと読む)

半導体装置

【課題】多層配線部からAVAI層間絶縁膜に亘る領域にMIM素子およびヒューズを形成し易い構造の半導体装置を得ること。

【解決手段】半導体基板10と、半導体基板に形成された回路素子20,30と、回路素子を覆うようにして半導体基板上に形成された多層配線部50と、多層配線部における最も上の層間絶縁膜45に形成されたヒューズ75と、多層配線部上に形成されたMIM素子70と、多層配線部を覆う最外層間絶縁膜60とを備えた半導体装置100を作製するにあたり、多層配線部における最も上の層間絶縁膜に形成された下部電極62と、下部電極上に形成された電気絶縁膜64と、電気絶縁膜上に形成された上部電極66とによってMIM素子を構成する。

(もっと読む)

半導体装置

【課題】多層配線部上に形成されたMIM素子およびヒューズを具備し、所望性能のものを高い歩留りの下に作製し易い半導体装置を得ること。

【解決手段】半導体基板10と、半導体基板に形成された回路素子20,30と、半導体基板上に形成されて回路素子を覆う多層配線部50と、多層配線部上に形成された最外層間絶縁膜60と、最外層間絶縁膜に形成されたMIM素子70と、最外層間絶縁膜に形成されたヒューズ75とを具備した半導体装置100を作製するにあたり、最外層間絶縁膜に設けられた凹部に埋め込まれて最外層間絶縁膜の上面と共通の面を形成する下部電極62と、下部電極上に形成された電気絶縁膜64と、電気絶縁膜上に形成された上部電極66とによってMIM素子を構成すると共に、最外層間絶縁膜に設けられた凹部に埋め込まれて最外層間絶縁膜の上面と共通の面を形成するようにして該最外層間絶縁膜にヒューズを埋め込み形成する。

(もっと読む)

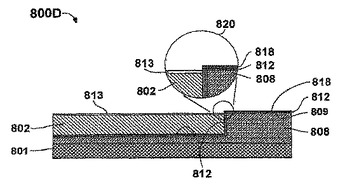

銅相互接続配線、ならびにそれを構成するための方法および機器

ガスクラスターイオンビーム処理プロセスの適用により、集積回路の相互接続構造に使用される、銅の相互接続配線層の表面上で、層をキャップ化する、改良された集積相互接続、集積回路の構造を形成する方法ならびに機器である。銅の拡散が抑制され、電気泳動寿命が向上し、選択金属キャップ化技術の使用、およびそれに付随した問題が解消される。銅のキャップ化処理、清浄化処理、エッチング処理、および膜形成処理用の、ガスクラスターイオンビーム処理モジュールを含む、各種クラスターツール構成について示した。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体基板

【課題】密着性の低い層間絶縁膜を使用する半導体装置の製造過程において、ウエハ端縁部で層間絶縁膜を含む積層膜が剥離することを防止した半導体装置の製造方法および半導体基板を得る。

【解決手段】ベベル部BV1上に形成された層間絶縁膜4を除去する際には、ラインL1で示す部分まで研磨を行い、層間絶縁膜4だけでなく半導体基板1の一部も除去するものとする。ラインL1が半導体基板1の主面となす角度αは0°よりも大きく30°以下に設定され、半導体基板1のベベル部BV1の角度に合わせて適宜設定される。研磨ドラムRDは、円筒状のドラムの側面に研磨布を貼り付けて構成され、ドラムを中心軸の回りに回転させるとともに半導体基板1も面内回転させながら、研磨ドラムRDを半導体基板1の端縁部に押し当てることで研磨を行う。

(もっと読む)

半導体装置とその製造方法

【課題】上下に積み重ねられる半導体チップ間の電気的接続についての信頼性を十分に確保した、半導体装置とその製造方法を提供する。

【解決手段】複数の半導体チップ2が積み重ねられてなる半導体装置である。半導体チップ2には、その第1面3aに電極パッド4が設けられ、かつ第2面3b側から第1面3a側にまで貫通し、電極パッド4の裏面に通じる貫通孔6が形成されるとともに、電極パッド4に導通する導電部7が、貫通孔6を通って第2面3b側にまで引き出されて設けられている。電極パッド4上には、電極パッド4に導通するバンプ10が設けられている。一方の半導体チップ2のバンプ10が、他方の半導体チップの導電部7に接した状態で貫通孔6を気密に塞いでいることにより、貫通孔6内が閉空間11とされているとともに、閉空間11が減圧状態に保持されている。

(もっと読む)

半導体装置とその製造方法、およびそのパターン生成方法

【課題】層間絶縁膜、特にLow−k膜を用いた場合の絶縁膜中の残留ガスによるバリアメタル等の劣化を抑制し、信頼性の高い半導体装置、その製造方法、およびパターン生成方法を提供する。

【解決手段】本発明の実施の形態に係る半導体装置10は、半導体基板上に形成された層間絶縁膜20と、この層間絶縁膜20上に形成された層間絶縁膜20よりも高い密度を有する保護膜21と、これら層間絶縁膜20および保護膜21内に形成された配線14およびダミー配線15の少なくとも一方と、を含む配線層11a〜11cと、前記層間絶縁膜20内で、前記配線14および前記ダミー配線15の被覆密度の合計が所定の規定値よりも低い低密度領域17を取り囲んで他の領域と分離する分離壁(金属壁16)と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu配線をダマシン法で形成する半導体装置及びその製造方法において、いわゆる電池効果による影響を無くし、低抵抗で信頼性の高いCu配線を提供する。

【解決手段】層間絶縁膜は、第1の層間絶縁膜201と、第1の層間絶縁膜201上に形成され銅の拡散を防止する性質を有する第2の層間絶縁膜202とから構成される。配線溝T1の内壁の上端部を除く部分に、Cu配線を形成する銅が層間絶縁膜へ拡散することを防止するバリアメタル膜が形成される。Cu配線は、第2の層間絶縁膜202とその上端部において接し、これよりも下部においてはバリアメタル膜203により覆われている。

(もっと読む)

半導体装置の製造方法

【課題】P型MOSFETの閾値のバラつきを抑制して高品質の半導体装置を形成することができ、また、製品開発のコストを抑制することができる半導体装置の製造方法を提供する。

【解決手段】シリコン基板上100にゲート絶縁膜102を形成する第1の工程と、ゲート絶縁膜102上に、ゲート電極104を構成する導電体膜103を、有機材料を用いた形成法によって形成する第2の工程と、導電体膜103が形成されたシリコン基板100を、酸化性雰囲気である水蒸気と、還元性雰囲気である水素との混合雰囲気中で加熱する第3の工程と、を備えた半導体装置の製造方法であって、第3の工程における水蒸気に対する水素の分圧比が、炭素が酸化され、かつ、導電体膜104を構成する金属材料が還元される分圧であることを特徴とする。

(もっと読む)

シード膜の成膜方法、プラズマ成膜装置及び記憶媒体

【課題】オーバハング部分を生ぜしめることなくシード膜を形成することができるシード膜の成膜方法を提供することにある。

【解決手段】真空引き可能になされた処理容器24内でプラズマにより金属ターゲット70をイオン化させて金属イオンを発生させ、金属イオンを処理容器内の載置台34上に載置した表面に凹部4を有する被処理体へバイアス電力により引き込んで凹部内を含む被処理体の表面に金属膜を形成することによりメッキ用のシード膜を形成するようにしたシード膜の成膜方法において、バイアス電力を、被処理体の表面に一旦形成された金属膜がスパッタされないような大きさに設定して金属膜を形成する成膜工程と、金属イオンを発生させないで金属膜の形成を休止する休止工程とを、交互に複数回繰り返す。

(もっと読む)

導電性ビアの製造と充填のための方法、およびそのように形成された導電性ビア

導電性ビアを形成する方法は、一つ以上のビアホールを基板内に形成するステップを含む。ビアホールは、単一マスク、保護層、ボンドパッド、もしくは、エッチングプロセスの間にフォトマスクが除去される場合にハードマスクとして機能する、基板のその他のフィーチャで形成され得る。ビアホールは、その表面に低誘電率(低K)誘電材料を含む誘電体コーティングの付着を促進するように構成されてもよい。障壁層が各ビアホールの表面の上に形成されてもよい。種材料(seed material)を含み得るベース層は、その後のビアホールの表面上の導電材料の選択的堆積を促進するように形成されてもよい。また、結果として得られる半導体素子、中間体構造、ならびに、これらの方法から得られる半導体素子を含むアセンブリと電子デバイスが開示される。 (もっと読む)

集積回路装置および回路製造方法

【課題】DRAM部とロジック部とが並設されている構造で生産性を向上させることができる集積回路装置を提供する。

【解決手段】複数の容量素子130の上部電極118を従来から必須の上部容量配線122aで接続することにより、複数の容量素子130の上部電極118を接続するために専用の製造工程や専用の製造設備が必要ないので生産性を向上させることができる。

(もっと読む)

1,961 - 1,980 / 2,805

[ Back to top ]