Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

2,001 - 2,020 / 2,805

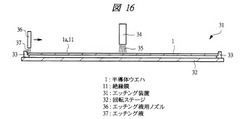

半導体装置の製造方法

【課題】半導体装置の製造歩留まりを向上させる。

【解決手段】ゲート電極の側壁絶縁膜形成用の絶縁膜11を半導体ウエハ1の主面上に堆積した後、絶縁膜11の膜厚分布を均一化する処理を行う。この処理では、エッチング装置31の回転ステージ32に固定されて回転する半導体ウエハ1の上方でエッチング液用ノズル36を半導体ウエハ1の主面の外周部側から中心部側に移動させながら、エッチング液用ノズル36からエッチング液37を半導体ウエハ1の主面に供給する。エッチング液用ノズル36の移動速度は、半導体ウエハ1における絶縁膜11の膜厚分布に応じて制御し、半導体ウエハ1の半径方向における絶縁膜11の膜厚の変化率が大きい領域では、変化率が小さい領域よりも、エッチング液用ノズル36の移動速度を遅くする。

(もっと読む)

半導体ウエハ

【課題】スクライブラインにプロセスモニタ用電極パッドを備えた半導体ウエハにおいて、半導体チップサイズ及びスクライブライン幅を大きくすることなく、メタルバリの発生を低減する。

【解決手段】複数の半導体チップ3がスクライブライン5によって互いに分離されてマトリクス状に配置されている。プロセスモニタ用電極パッド11は、ポリシリコン層18上に形成されたポリ−メタル層間絶縁膜19上に形成された1層目メタル配線層21−1を少なくとも含む3層のメタル配線層からなり、スクライブライン5の切断領域13を含んで切断領域13よりも広い幅をもってスクライブライン5に配置されている。プロセスモニタ用電極パッド11下のポリ−メタル層間絶縁膜19に1層目メタル配線層21−1とポリシリコン層18を接続するための接続孔20が形成されている。

(もっと読む)

イメージセンサの金属配線形成方法

【課題】金属配線の熱安定性を確保し、イメージセンサの暗電流特性を改善させるためのイメージセンサの金属配線形成方法を提供すること。

【解決手段】半導体基板上にコンタクトプラグを備える第1の層間絶縁膜を形成するステップと、該第1の層間絶縁膜上に拡散防止膜を形成するステップと、フォーミングガスアニールを行うステップと、前記拡散防止膜上に第2の層間絶縁膜を形成するステップと、該第2の層間絶縁膜及び拡散防止膜を選択的にエッチングしてトレンチを形成するステップと、該トレンチを埋め込むまで導電物質層を形成するステップと、該導電物質層を平坦化してコンタクトプラグと電気的に接続する金属配線を形成するステップとを含み、上記した本発明は、 金属配線を形成する工程の前に拡散防止膜を形成した後、アニール処理を行って金属配線の熱安定性を確保し、イメージセンサの暗電流特性を改善させて金属配線の信頼性及び素子の信頼性を向上させるという効果がある。

(もっと読む)

プロセス変動に耐性を有するダイオード、同ダイオードを有するスタンダードセル、同ダイオードを含むタグ及びセンサ、並びに同ダイオードを製造する方法

【課題】プロセス変動に耐性を有するダイオード及びダイオード接続薄膜トランジスタ(TFT)を提供する。

【解決手段】ダイオード又はTFTを含む印刷又はパターニング構造(例えば、回路)、これらを製造する方法、並びに、これらの識別タグ及びセンサへの応用を開示する。相補型のダイオード対又はダイオード接続TFTを直列に含む印刷された構造は、印刷又はレーザ描画技術を用いて製造したダイオードの閾値電圧(Vt)を安定化することができる。NMOS TFTのVt(Vtn)とPMOS TFTのVt(Vtp)の間の分離を利用して、印刷又はレーザ描画のダイオードの順方向電圧降下の安定性を確立又は向上する。更なる応用は、参照電圧発生器、電圧クランプ回路、参照又は差動信号伝送ラインにおける電圧を制御する方法、並びにRFID及びEASタグ及びセンサに関する。

(もっと読む)

半導体装置およびその製造方法

【課題】ビア・配線間の重ね合わせがずれた場合にもTDDBを抑制できる半導体装置およびその製造方法を提供する。

【解決手段】順次積層された絶縁膜1,2内に形成された溝11内には、バリアメタル3およびCuからなる配線4が埋め込まれている。配線4上にはメタルキャップ9が配置され、メタルキャップ9上には、絶縁膜5,6が順次積層されている。絶縁膜5,6内に形成された溝14内には、バリアメタル7およびCuからなる配線8が埋め込まれている。この絶縁膜5は、Cuが拡散されないものとする。バリアメタル7は、ビア・配線間の重ね合わせにおいて位置ずれが生じた場合にも、メタルキャップ9には接触するが配線層21の絶縁膜2やバリアメタル3には接触しないように形成される。

(もっと読む)

異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造および方法

【課題】異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造、方法などを提示すること。

【解決手段】このMOSFET回路は、コンタクト線(500、1300)と、コンタクト線(500、1300)の近くに位置するゲート(310、1210)とを含む。コンタクト線(500、1300)は、ゲート(310、1210)の高さよりも低い高さを含む。このMOSFET回路はさらに、ゲート(310、1210)の近くに位置するゲート・スペーサ(710、715、1610、1615)を含み、コンタクト線(500、1300)とゲート(310、1210)との間のコンタクト線(500、1300)の近くに位置するコンタクト線スペーサを含まない。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の低抵抗化を図る。

【解決手段】本発明の半導体装置は、第1金属膜18に当接するように半導体層に形成された貫通孔10と、前記貫通孔10の側壁部に形成された絶縁膜12と、前記絶縁膜12が形成されていない前記貫通孔10の底部の第1金属膜18上と前記半導体層上に形成された第2金属膜13と、前記貫通孔10内の前記絶縁膜12及び第1金属膜18上に形成されたバリアメタル膜14と、前記バリアメタル膜14を介して前記貫通孔内に形成された配線層15とを具備することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】フリップチップ工法等による実装に於いてもSOI構造の支持基板の電位を安定的に固定可能にすると共に、低抵抗な基板コンタクトを形成する。

【解決手段】SOI構造の支持基板1と最上層配線13とを接続する複数の導電層と複数の配線層は、最上層配線13と共にチップ周縁部に沿って形成され、以ってトランジスタTrが形成されるトランジスタ形成領域TRの周囲に形成される。

(もっと読む)

LowK誘電絶縁体及び半導体回路構造の形成方法

【課題】半導体製造用に改善された誘電体及び機械的特性を有する絶縁体材料を供する。

【解決手段】材料は酸素、シリコン及び水素を含み、2g/ccより小さい密度を特徴とする。あるいは多孔質絶縁体材料は633nmないし673nmの波長の光に対する1.45より小さい屈折率又は45GPaより小さいヤングモジュラスを特徴とする。半導体デバイスの作製方法は、デバイス形成のための上部表面を有する半導体層を供すること及び半導体層上に複数のレベルの相互接続を形成し、各レベルは複数の部分を含むことを含む。部分は少なくともいくつかの部分間に多孔質層を形成するため、TEOSを分解することにより、他の部分から電気的に分離される。

(もっと読む)

無電解フェーズと電流供給フェーズとを含むウェット化学堆積によりパターニングされた絶縁体上の金属層

無電解堆積および電気堆積プロセスをインサイチュで実行することによって、非常に信頼性のあるメタライゼーションが供給され、その際に、シード層を形成する、従来の化学気相堆積(CVD)、原子層堆積(ALD)ならびに物理気相堆積(PVD)技術にみられるような、汚染物質ならびにデバイススケーリングに関する欠点を克服することができる。ある実施例では、バリア層はさらに、ウェット堆積プロセスに基づいて堆積される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】歩留り良く製造可能で、かつ高い信頼性を有する半導体装置とその製造方法を提供する。

【解決手段】半導体装置の製造方法は、第1の層間絶縁膜1に形成された第1の配線溝内にバリアメタル3、シード膜4および配線材料膜5からなる第1の配線を形成する工程と、第1の層間絶縁膜1上に第2の層間絶縁膜7を形成した後に第2の層間絶縁膜7内にビアホール8および第2の配線溝9を形成し、配線材料膜5を露出させる工程と、半導体装置上にバリアメタル10aを形成する工程と、リスパッタリングなどにより配線材料膜5上のバリアメタル10aを除去した後、配線材料膜5上にバリアメタル21を形成する工程とを含む。リスパッタリングによって配線材料膜5上に形成されたシード膜4中の不純物金属の酸化膜13を除去することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、配線パターンがプラズマ処理により形成される半導体装置及びその製造方法に関し、プラズマ処理によるゲート酸化膜の破損を防止することを課題とする。

【解決手段】半導体基板11に、回路形成領域Aに対応する半導体層16と、回路形成領域Aを囲むように設けられた非形成領域Bに対応する半導体層16とを電気的に分離する絶縁部材18を設け、絶縁部材18が設けられた半導体基板11の回路形成領域Aに複数の半導体集積回路12を形成した。

(もっと読む)

半導体装置の配線用金属薄膜及び半導体装置用配線、並びにこれらの製造方法

【課題】半導体埋込型配線の製造に用いられる金属薄膜であって、高温高圧処理時に優れた高温流動性を示すと共に、電気抵抗率が低く、高品質を安定して発揮する半導体装置用配線を得ることのできる半導体装置の配線用金属薄膜、およびこれを用いて得られる半導体装置用配線を提供する。

【解決手段】Nを0.4at%以上2.0at%以下含むCu合金からなるものであることを特徴とする半導体装置の配線用金属薄膜、および半導体基板上の凹部を有する絶縁膜上に、上記金属薄膜を形成後、高温高圧処理して該金属薄膜を上記凹部内に埋め込むことにより形成されることを特徴とする半導体装置用配線。

(もっと読む)

半導体装置の製造方法及び磁気ヘッドの製造方法

【課題】高温環境下における配線層内でのボイドの発生を抑制して配線層の導通不良を抑制し、半導体装置の信頼性を向上しうる半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜34に、配線溝38を形成する工程と、配線溝38内に、Cuを主材料とする配線層44を形成する工程と、配線溝38内に埋め込まれた配線層44の表面に対して、アンモニア及び水素が溶解された純水と窒素ガスとを同時に吹き付ける窒素二流体処理を行う工程とを有する。

(もっと読む)

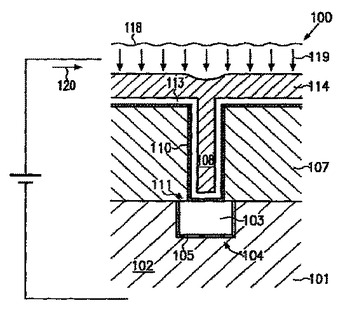

半導体装置および半導体装置の製造方法

【課題】配線やビアの構成材料として銅を含む半導体装置の信頼性を高める。

【解決手段】半導体装置100は、半導体基板(不図示)と、その上に形成された第1の絶縁層102と、第1の絶縁層102上に形成され、銅を主成分として含むビア104(第1の金属膜108)と、第1の絶縁層102上に第1の金属膜108に接して設けられ、Ru、TaまたはTiを含む第4の層118a、Wを含む第5の層118b、およびRu、TaまたはTiを含む第6の層118cがこの順で形成された第2のバリアメタル膜118と、第2のバリアメタル膜118上に第6の層118cに接して設けられ、銅を主成分として含む第2の金属膜120とを含む。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】半導体記憶装置におけるコンタクト抵抗を低減すること。

【解決手段】本発明に係る半導体記憶装置は、基板1上に形成されたメモリセルと、基板1上に形成された周辺トランジスタとを備える。メモリセルは、基板1上に形成された選択トランジスタと、その選択トランジスタに接続されたキャパシタとを備える。周辺トランジスタの拡散層5は第1コンタクトC1を介して上層配線に接続される。ゲート電極3は第2コンタクトC2を介してワード線や上層配線に接続される。選択トランジスタの拡散層4は第3コンタクトC3を介してビット線あるいはキャパシタに接続される。第1〜第3コンタクトC1〜C3のうち、第1コンタクトC1の底部にのみシリサイド21が選択的に形成される。

(もっと読む)

ダマシン配線の形成方法

【課題】基板に形成された溝部に配線材料を埋め込むダマシン配線の形成方法であって、カバレッジの悪いシード層を修理することができ、電解めっき時に配線材料を安定的に成長させ、ボイド等の不具合発生を抑制することのできるダマシン配線の形成方法を提供する。

【解決手段】スパッタ成膜されたシード層5に、分散剤に溶かした配線材料のナノパーティクル含有溶液7を塗布するステップと、前記ナノパーティクル含有溶液7上に有機溶媒を塗布しエッチバックするステップと、前記ナノパーティクルの溶媒と前記有機溶媒とを蒸発させるベーク処理を行うステップと、前記分散剤を蒸発させナノパーティクルを金属膜にするアニール処理を行うステップとを実行する。

(もっと読む)

半導体装置の製造方法

【課題】RC遅延が抑制された半導体装置の製造方法を提供する。

【解決手段】まず、基板上に設けられた層間絶縁膜7に、配線溝8aと接続孔8bとからなるデュアルダマシン開口部8を形成する工程を行う。次に、デュアルダマシン開口部8の内壁を覆う状態で、層間絶縁膜7上にMnからなる金属膜21を形成する工程を行う。次いで、熱処理を行い、金属膜21中の金属を層間絶縁膜7の構成成分と反応させて、金属膜21と層間絶縁膜7との界面に、Mn化合物からなる自己形成バリア膜11を形成する工程を行う。続いて、金属膜21の未反応部分を選択的に除去する工程を行う。その後、デュアルダマシン開口部8に、Cuを含む導電層を埋め込んで、配線溝8aと接続孔8bとに上層配線12とヴィア13とをそれぞれ形成する工程を行うことを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置

【課題】高周波特性を低下させることなくLDMOSFETを有するチップの面積を縮小する。

【解決手段】LDMOSFETのソース領域と基板1の裏面に形成されたソース裏面電極36とを電気的に接続するp型打ち抜き層4を不純物を高濃度でドープした低抵抗のp型多結晶シリコン膜もしくは低抵抗の金属膜から形成する。そして、LDMOSFETの基本セルのソース同士を電気的に接続するソース配線は配線24Aのみとし、ソース配線を形成する配線層数は、ドレイン配線(配線24B、29B、33)を形成する配線層数より少なくする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】C5F8ガスをエッチングガスとして使用するエッチング処理時において、C5F8ガスの使用量を削減できる技術を提供する。

【解決手段】C5F8ガスをエッチングガスとして用いて酸化シリコン系膜をドライエッチングするドライエッチング装置において、実際にエッチング処理を行う処理ステップ(STEP3)の直前の安定化ステップを、C5F8ガスの導入を行わないSTEP1とC5F8ガスの導入を行うSTEP2との2段階に分けて行う。STEP2でのC5F8ガスの流量は、STEP3でのC5F8ガスの流量と同じとする。

(もっと読む)

2,001 - 2,020 / 2,805

[ Back to top ]