Fターム[5F033PP07]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | CVD(化学的気相成長法) (3,065) | 選択CVD (170)

Fターム[5F033PP07]の下位に属するFターム

選択性を向上させておくもの (51)

Fターム[5F033PP07]に分類される特許

61 - 80 / 119

レーザ加工装置、レーザ加工方法、TFT基板、及び、TFT基板の欠陥修正方法

【課題】加工対象においてレーザ加工を精度よく行なうことが可能なレーザ加工方法を提供する。

【解決手段】加工用レーザを照射するためのレーザ光源と、加工用レーザをXY方向に走査させるガルバノミラーと、加工対象物をXY方向に移動させるXYステージとを備えたレーザ加工装置によって、ガルバノミラーの走査可能範囲よりも大きな図形を加工する。加工対象において、ガルバノミラーの走査可能範囲を超える図形を、ガルバノミラーの走査可能範囲内に収まる図形によって複数に分割し、XYステージを移動することにより、ガルバノミラーの走査可能範囲内に複数に分割した図形を移動し、ガルバノミラーにより加工用レーザを走査し、分割した図形に対し加工用レーザを照射することによりレーザ加工を行う。

(もっと読む)

金属含有IV族薄膜の形成方法及び半導体装置の製造方法並びにマイクロデバイス

【課題】金属シリサイドなどの金属とIV族元素との化合物からなる薄膜や実質的に金属膜として機能する高濃度に金属を含有する金属含有薄膜のパターンを成膜することができる金属含有IV族薄膜の形成方法及びこれを適用した半導体装置の製造方法並びにマイクロデバイスを提供する。

【解決手段】基板の表面にIV族元素からなるIV族薄膜を成膜した後、パターニングし、所定領域にIV族薄膜パターンを有する被処理体とする工程と、この被処理体の表面に形成されたIV族薄膜パターンに、ニッケル、鉄、コバルトを含む遷移金属から選択される少なくとも1種である金属とハロゲンとの化合物である前駆体及びハロゲンラジカルを作用させることにより、前記IV族薄膜パターンを空間選択的に金属含有IV族薄膜パターンとする工程とを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】貫通電極に空洞部が形成されることを防止する。

【解決手段】第1半導体基板1の表面および貫通孔2の内壁面を保護膜3で覆った状態で導体にて構成されたパッド8の表面に導体膜11を結晶成長させる。この導体膜11にて、貫通電極4を形成する。このように、パッド8の表面に主に結晶成長させ、保護膜3には結晶成長がほとんど起こらない選択成長によって貫通電極4を形成しているため、空洞の無い、良好な貫通電極4とすることができる。このため、断線・配線抵抗の増加を防止できると共に、EM耐性の低下等も防止することが可能となる。

(もっと読む)

表示装置の製造方法およびTFTアレイ基板の製造方法

【課題】修復用の配線パターンを予め形成することも、画素を常時非点灯化することもなく、欠陥画素を修復可能な表示装置の製造方法およびTFT基板の製造方法を提供する。

【解決手段】駆動トランジスタTr1とスイッチングトランジスタTr3とを有する画素回路を備えた表示装置の製造方法において、スイッチングトランジスタTr3に不良が生じた場合に、スイッチングトランジスタTr3’の不良部分を断線する工程と、基板1の全域上にパッシベーション膜31を形成する工程と、断線したスイッチングトランジスタTr3’のドレイン電極23’上と、隣接画素のスイッチングトランジスタTr3のドレイン電極23上の前記パッシベーション膜31にコンタクトホール31aを形成し、コンタクトホール31aを介してドレイン電極23,23’同士を導電材料により結線する工程とを行うことを特徴とする表示装置およびTFTアレイ基板の製造方法である。

(もっと読む)

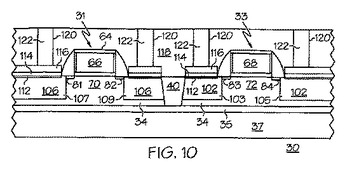

歪みが強化された半導体デバイスとその製造方法

歪みが強化された半導体デバイス30とその製造方法が提供される。1つの方法において、デバイスチャネル70、72に歪みを誘発するために、デバイスのソース領域103、107とドレイン領域105、109とに歪み誘発半導体材料102、106が埋め込まれる。誘発された歪みを緩和しないように、ソースおよびドレイン領域に対して薄い金属シリサイドコンタクト112が形成される。導電性材料114、116の層が薄い金属シリサイドコンタクトに接触して選択的に蒸着され、金属化されたコンタクト122が導電性材料に対して形成される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、コンタクトプラグを用いずに異なるトランジスタのゲート電極とドレイン領域とを電気的に接続することを特徴とする。

【解決手段】トレンチ型の素子分離絶縁膜12によって素子分離された複数の素子領域13と、各素子領域上に形成されると共に各素子領域に隣接する素子分離絶縁膜12上まで延長して形成され、多結晶シリコンからなる側壁膜17を有するゲート電極14と、各素子領域内に形成されたトランジスタのドレイン領域18と、素子分離絶縁膜12上に位置するゲート電極14の上部及び側壁膜17上並びに素子分離絶縁膜12に隣接する異なるトランジスタのドレイン領域18上に渡って連続して形成された金属シリサイド膜20と、金属シリサイド膜20上を含む全面上に形成された層間絶縁膜21を具備している。

(もっと読む)

配線構造及びその形成方法

【課題】コンタクトブロックを用いた炭素元素からなる線状構造体を材料とする配線を、できるだけ工程数を削減して、低コストで容易且つ確実に形成する。

【解決手段】コンタクトブロック1,2の対向面1a,2aを起点として、互いの対向面に向かってそれぞれ複数本のCNT3a,3bを成長させてゆき、CNT3a,3bを交差するように接触させて両者を電気的に接合してCNT束3を形成する。そして、電気的に接合されたCNT束3の間隙を金属材料4で埋め込み、CNT束3と金属材料4との複合状態とされてなる配線5を形成する。

(もっと読む)

半導体装置の製造方法

【課題】被覆率としては従来と変わることなく、かつシリコン酸化膜との間で選択比の取れるシリコン窒化膜を有する半導体装置の製造方法を提供することにある。

【解決手段】半導体基板の主表面上に層間絶縁膜を形成する工程と、前記層間絶縁膜に前記半導体基板の主表面に達するコンタクトホールを形成する工程と、前記側壁にシリコン窒化膜が形成されたコンタクトホール内にTi層およびTiN層を有するバリアメタル層を形成する工程と、前記バリアメタル層が形成されたコンタクトホール内に導電層を形成する工程と、SinCl2n+2とNH3との混合ガス、またはSinCl2n−2−xとNH3との混合ガスを用い(nは2以上の自然数、xは2n+2以下の自然数)、700℃以下の成膜温度で、前記コンタクトホール内の導電層上に塩素を含有するシリコン窒化膜を形成する工程とを備えたことを特徴とする。

(もっと読む)

集積回路の修正配線形成方法

【課題】 カーボンナノチューブ配線を用いた集積回路の修正配線形成方法を提供する。

【解決手段】 電子ビーム化学気相成長法で配線修正が必要なところに成長の触媒となる金属を含む微粒子10を堆積し、炭化水素系ガスやエタノールを原料とした化学気相成長法でカーボンナノチューブ配線11を成長させる。配線修正が必要なところへの触媒金属の供給は走査マイクロピペットプローブ顕微鏡による電気化学反応による析出または集束イオンビーム化学気相成長法でも行うことができる。

(もっと読む)

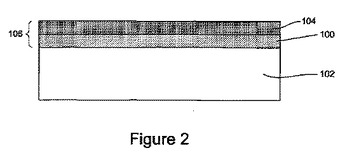

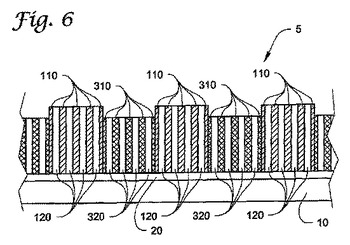

金属シリサイド晶子上にナノ構造物を形成する方法、並びにこの方法により得られる構造物及びデバイス

本発明の種々の実施形態は、非単結晶基板上にナノ構造物を形成する方法、並びにその結果得られるナノ構造物及びナノスケール機能デバイスに関する。本発明の一実施形態では、ナノ構造物を形成する方法は、金属層(100)及びシリコン層(104)を含む多層構造物(106)を形成することを含む。多層構造物(106)は、熱工程にかけられ、それにより金属シリサイド晶子(110)が形成される。金属シリサイド晶子(110)上にはナノ構造物(114)が成長される。本発明の別の実施形態では、構造物は、非単結晶基板(102)及び非単結晶基板(102)上に形成された層(108)を含む。層(108)は、金属シリサイド晶子(110)を含む。金属シリサイド晶子(110)上にいくつかのナノ構造物(114)が形成されてもよい。開示の構造物は、電子デバイス及び/又は光電子デバイスで使用されるいくつかの異なるタイプの機能デバイスを形成するために使用することができる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】多層配線構造の作製において、すべての多層配線用ビア・配線・電極および放熱用ビアなどを、相互の接続特性を良好に保って、カーボンナノチューブ(CNT)束により形成する半導体装置を提供する。

【解決手段】電導素材である、柱状構造をもったカーボンナノチューブ(CNT)束2の少なくとも一つの表面に、Au膜など金属膜を形成後、下地層を積層し、その上に触媒金属層を形成して、CVD法により柱状構造をもったカーボンナノチューブ(CNT)束7を成長することで、二つの柱状構造体カーボンナノチューブ(CNT)束を低抵抗で接続して形成する。この基本構成方法の組合せで、多層配線用の各種電導構成要素を作製する。また、成長条件によりCNTの成長先端部が平坦となることを用いて、Au膜など金属膜を利用せずに、成長方向に多段に、長いカーボンナノチューブ(CNT)束を作製でき、特に放熱用ビアなどへの適用が可能である。

(もっと読む)

サブリソグラフィックパターニングのためにブロック共重合体自己集合を使用する方法

ブロック共重合体は自己集合し、例えば本明細書に記載のサブリソグラフィックパターニングのための方法で使用され得る。ブロック共重合体は、ジブロック共重合体、トリブロック共重合体、マルチブロック共重合体、もしくはそれらの組み合わせであってよい。そのような方法は、例えばサブリソグラフィック導電性ラインを含むデバイスの作成に有用であり得る。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】Cuの拡散を防止することができ、かつ、層間の誘電率が高くなることを抑制することができる半導体装置およびその製造方法を提供すること。

【解決手段】 ウエハWにCu配線層6を形成し、Cu配線層6の上に、炭化水素ガスを含む処理ガスを用いたCVDによりCu拡散バリアとしてアモルファスカーボン膜7を成膜し、その上にLow−k膜8を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の大面積化や配線の微細化に伴って銅のシード層が薄くなると、電解めっきでめっき膜のばらつきが大きくなる。

【解決手段】デュアルダマシン法で埋め込み配線を形成するにあたって、下層配線2上に孔加工や溝加工の加工マスクとなるTiN膜8を用いて、配線埋め込み領域(9,10)を形成する工程と、配線埋め込み領域を除くフィールド部に導電膜11を成膜する工程と、配線埋め込み領域を覆うようにバリアメタル層/シード層12を成膜する工程と、配線埋め込み領域を電解めっき法により銅配線材料13で埋め込む工程とを含むものとする。

(もっと読む)

基板貫通相互接続を形成する方法

少なくとも1つの基板貫通相互接続を形成する方法の一実施形態において、第1の表面202、及び反対側の第2の表面204を有する半導体基板200を提供する。半導体基板に、少なくとも1つの開口210を、半導体基板内で第1の面から中間深さまで延在するように形成する。少なくとも1つの開口は、基部216によって部分的に画定される。基部上に、少なくとも1つの金属触媒ナノ粒子220を提供する。金属触媒ナノ粒子によって導電性材料222の堆積が促進される条件下で、少なくとも1つの開口内に導電性材料を堆積させる。半導体基板の材料を第2の面から除去することにより、少なくとも1つの開口を充填する導電性材料の一部を露出させることができる(図3K)。別の実施形態では、ナノ粒子を使用する代りに、導電性材料を、少なくとも1つの開口を部分的に画定する基部に選択的に堆積するように選択することができる。  (もっと読む)

(もっと読む)

チャンネル膜を有する半導体装置の製造方法

【課題】 結晶欠陥が小さくかつ表面粗さの特性が良好なチャンネル膜を有する半導体装置の製造方法を提供する。

【解決手段】 チャンネル膜を有する半導体装置の製造方法は、チャンネルシリコン膜を形成するために、まず単結晶シリコン基板100上に、上部表面から延長して突出した部位を含む第1単結晶シリコン膜110を形成する。第1単結晶シリコン膜110の上部表面に犠牲膜112を形成する。第1単結晶シリコン膜110の前記突出した部位及び犠牲膜112の一部が除去されるように第1単結晶シリコン膜110及び犠牲膜112を1次研磨して第2単結晶シリコン膜及び犠牲膜パターンを形成する。前記犠牲膜パターンを除去し、前記第2単結晶シリコン膜を研磨してチャンネルシリコン膜を形成する。前記工程によると、単結晶シリコン膜の研磨厚さを減少させることができ、チャンネルシリコン膜は表面粗さの特性が良好であり、厚さが平坦となる。

(もっと読む)

半導体素子の金属配線形成方法

【課題】トレンチ内の障壁金属層の上部にのみ化学気相蒸着方法を用いて選択的に比抵抗が低い金属層を蒸着し、熱処理を実施した後、平坦化して低抵抗金属配線を形成することができる半導体素子の金属配線形成方法を提供する。

【解決手段】RFエッチング方法でトレンチ108の底面と絶縁膜パターンの下部側壁にのみ障壁金属層120を残留させる。MPAソースを前駆体として用いるCVD法を用い、障壁金属層120の上部にのみ選択的に比抵抗が低い金属層130を蒸着し、熱処理を実施した後、平坦化して金属配線140を形成する。熱処理を実施して金属物質でトレンチ108を完全に満たすことで平坦化する。かくして脆性のアルミニウム膜によるディッシングとスクラッチなどは発生せず、金属配線140としての高い信頼性が確保されて、低抵抗金属配線を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】多層配線の容量低減を図る半導体装置の製造方法或いは半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、配線が形成された配線層上に第1の絶縁性材料膜を形成する絶縁膜形成工程(S108)と、前記絶縁性材料膜に前記配線層まで貫通する複数の孔を形成する開口工程(S112)と、前記複数の孔のうち、前記配線上に位置する孔内にヴィアコンタクト膜を選択的に形成するヴィアコンタクト膜形成工程(S116)と、前記複数の孔のうち前記ヴィアコンタクト膜が形成されずに残った孔にふたをするように、第2の絶縁性材料膜を形成する絶縁膜形成工程(S120)と、を備えたことを特徴とする。

(もっと読む)

薄膜の形成方法、成膜装置及び記憶媒体

【課題】原料として有機酸銅を用いることにより、微細な凹部を埋め込みつつ銅の薄膜を膜厚の制御性良く、しかも高い成膜レートで堆積させることができる成膜装置を提供する。

【解決手段】被処理体Wの表面に薄膜を形成する成膜装置20において、排気可能になされた処理容器22と、被処理体を載置するための載置台24と、被処理体を加熱するための加熱手段26と、処理容器に設けられて、処理容器内へガスを導入するためのガス導入部56と、ガス導入部へ気体の有機酸銅を供給する原料ガス供給手段68と、装置全体の動作を制御する装置制御部100とを備え、被処理体の表面に薄膜として銅膜を形成する。

(もっと読む)

導電性パターンの形成方法及び導電性パターン

【課題】p型またはn型に制御された低抵抗のSiGeからなる導電性パターンを基材上に選択的に500℃以下の低温で形成することを可能にする。

【解決手段】ガラス又は酸化ケイ素からなる非晶質基材上にアルミニウム薄膜又はクロム薄膜をパターン状に形成し、フッ化ゲルマニウムとジシランを原料とした熱CVD法によって、前記パターン状に形成されたアルミニウム薄膜又はクロム薄膜上にのみ選択的にSiGeを堆積する。得られた導電性パターンは、SiGe膜が、非晶質基材上にパターン状に形成されたアルミニウム薄膜又はクロム薄膜上にのみ選択的に形成され、非晶質基材上には形成されない。

(もっと読む)

61 - 80 / 119

[ Back to top ]