Fターム[5F033PP07]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | CVD(化学的気相成長法) (3,065) | 選択CVD (170)

Fターム[5F033PP07]の下位に属するFターム

選択性を向上させておくもの (51)

Fターム[5F033PP07]に分類される特許

41 - 60 / 119

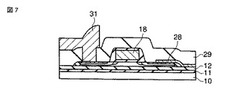

薄膜半導体装置およびその製造方法

【課題】コンタクトおよび配線形成時の合わせマージンがゼロであり、集積度を大幅に向上し、パターンレイアウトの自由度の拡大を可能とする薄膜半導体素子及びその製造方法を提供する。

【解決手段】透明絶縁性基板10上に形成され、第1導電型の不純物を含むソース領域及びドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜及びゲート電極18、前記ソース領域又はドレイン領域の表面に形成された高融点金属と半導体との化合物からなる層、前記島状半導体層及びゲート電極を覆う層間絶縁膜29、及び前記ソース領域又はドレイン領域に接続された局所配線28を具備し、前記局所配線28は、前記ソース領域又はドレイン領域の表面に形成された前記化合物層と高融点金属層との2層構造、及び前記ソース領域又はドレイン領域の外側に形成された前記高融点金属層の延長からなることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】絶縁膜で十分な機械的強度を確立することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置11は基板12を備える。基板12の表面には複数層の絶縁膜15が積層される。絶縁膜15同士の間には導電性の配線層16が挟み込まれる。配線層16から離れつつ絶縁膜15には炭素系材18が埋め込まれる。炭素系材18は高い機械的強度を有する。その結果、絶縁膜15では十分な機械的強度が確立される。同様に、半導体装置11では十分な機械的強度が確立される。絶縁膜15の表面に平坦化処理が施されても、絶縁膜15の破損は回避される。加えて、例えば半導体装置11の実装にあたって半導体装置11の損傷は回避される。

(もっと読む)

半導体装置およびその製造方法

【課題】微細なコンタクト構造であっても、低コンタクト抵抗のコンタクト構造を形成することができる半導体装置およびその製造方法を提供する。

【解決手段】シリコン基板11の表面部に形成された不純物領域15と、不純物領域15の表面から所定深さにわたって形成された金属シリサイド層16とを備える。シリコン基板11上には層間絶縁膜18が形成され、層間絶縁膜18を貫通して底部が金属シリサイド層16に到達するコンタクトホール19が形成されている。コンタクトホール19は、金属シリサイド層16からなる側壁の面積が、金属シリサイド層16からなる底面の面積よりも大きい開口部になっている。さらに、コンタクトホール19の、金属シリサイド層16からなる側壁および底面に接触するコンタクトプラグ21がコンタクトホール19に埋め込まれている。

(もっと読む)

ナノ構造処理のための導電性補助層の形成及び選択的除去

一又は複数のナノ構造の作成方法が開示されており、当該方法は:基板の上部表面上に導電層を形成すること;導電層上に触媒のパターン層を形成すること;触媒層上に一又は複数のナノ構造を成長させること;及び一又は複数のナノ構造の間及び周囲の導電層を選択的に除去することを含んでなる。デバイスもまた開示されており、該デバイスは、基板、ここで基板は一又は複数の絶縁領域によって隔てられた一又は複数の露出金属島を含んでなる;一又は複数の露出金属島又は絶縁領域の少なくともいくつかを覆う基板上に配された導電性補助層;導電性補助層上に配された触媒層;及び触媒層上に配された一又は複数のナノ構造を含んでなる。 (もっと読む)

半導体装置及びその製造方法

【課題】メモリセルトランジスタのコンタクト抵抗を低減する。

【解決手段】半導体装置70には、半導体基板1上に複数の絶縁ゲート型電界効果トランジスタが設けられる。絶縁ゲート型電界効果トランジスタのゲートの間に形成され、側面が側壁絶縁膜8及び絶縁膜9により絶縁ゲート型電界効果トランジスタのゲートと分離された自己整合コンタクト開口部の底部には凹部形状のポリシリコンプラグ11が設けられる。ポリシリコンプラグ11上にはバリアメタル膜12が設けられる。バリアメタル膜12上には、自己整合コンタクト開口部を覆うように金属プラグ13が埋設される。

(もっと読む)

相互接続構造のための貴金属キャップおよびこれを形成する方法(相互接続構造のための貴金属キャップ)

【課題】 誘電率が約3.0以下の誘電材料(52)を含む相互接続構造を提供する。

【解決手段】 この低k誘電材料は、上面が埋め込まれた少なくとも1つの導電材料(60)を有する。また、誘電材料は、貴金属キャップ(62)の形成前に疎水性とされた表面層(52B)を有する。貴金属キャップは、少なくとも1つの導電材料の上面上に直接に配置されている。誘電材料上に疎水性表面層が存在するために、貴金属キャップは、少なくとも1つの導電材料に隣接した誘電材料の疎水性表面層上に実質的に延出せず、この疎水性の誘電表面上に貴金属キャップ堆積からの貴金属残留物は存在しない。

(もっと読む)

集積回路の配線形成方法

【課題】 半導体集積回路等の微細な集積回路の修正等を行う際、配線を低抵抗で形成することができる集積回路の配線形成方法を提供する。

【解決手段】 集積回路2上の配線を必要とする部分2cxを集束イオンビーム10aにより掘出す工程と、掘出し工程によって掘出された部分に対し、銀40をコートした走査トンネル顕微鏡探針21に電圧パルスを印加して該探針から銀原子を移動させる走査トンネル顕微鏡法により、銀配線4cを形成する工程とを有する集積回路の配線形成方法であって、配線を必要とする部分の線幅が1μm以下である場合は走査トンネル顕微鏡法を用い、線幅が1μmを超える場合は、集積回路上の配線を必要とする部分に対し、非サーマル方式のインクジェット装置から銀粒子を含むインクを噴射した後に、レーザー又は加熱した走査プローブ顕微鏡の探針でインクを乾燥させるインクジェット法により銀配線を形成する。

(もっと読む)

平面表示装置、アレイ基板及びその製造方法

【課題】平面表示装置100及びその製造方法において、信号線方向に隣り合う画素電極同士を導通させる方式での補修(タンデムリペア)を、画素ドット欠陥の位置に拘わらず容易に行うことができ、また、画素開口率の低下を最小限としつつ、リペア箇所での補助容量比のズレを防止できるものを提供する。

【解決手段】信号線31方向での画素電極6間の中間領域のうち、信号線方向及び走査線方向のいずれから見ても一つ置きに、導電層フロートパターン12Aと、これに重なり合う補助容量線延在部22Aと、この切り欠きに対応するリペア接続用パターン32Aとを設けておく。タンデムリペアの際、リペア接続用パターン32Aにレーザー光を照射して導電層フロートパターン12Aに達する導通部82を作成する。そして、レーザーCVDによる画素電極6間のブリッジ配線81が、リペア接続用パターン32Aを直接覆うようにする。

(もっと読む)

Cuキャップ層としてCuゲルマナイドおよびCuシリサイドを集積および作製する方法

【課題】周囲の誘電体材料にダメージを与えない銅配線上のキャップ層を形成する方法を提供する。

【解決手段】Cu、N、およびSiおよび/またはGeを含むキャップ層6を、銅の導電構造2の上に形成する方法であって、200℃と400℃との間の温度範囲で、構造をGeH4および/またはSiH4含有雰囲気3に晒すことにより、銅の導電構造2の上に少なくとも1つのキャップ層を形成する工程と、NH3プラズマ処理5を行って、少なくとも部分的に窒化されたキャップ層6を形成する工程と、少なくとも部分的に窒化されたキャップ層6の上に誘電体バリア層7を形成する工程とを含み、少なくとも1つのキャップ層を形成する工程の前に、250℃と450℃との間の温度範囲で、銅の導電構造のプレアニール工程が行われることを特徴とする方法。

(もっと読む)

半導体集積回路装置の製造方法

【課題】デバッグ等のために、完成した半導体集積回路装置の配線をFIB加工を用いて事後的に修正する場合がある。修正配線は配線として最適に材料を使用すべきである。しかし、たとえば、比抵抗の低い金属は、比較的その後の検査・試験環境に弱い等の問題がある。

【解決手段】本願発明は、ほぼ完成した半導体集積回路装置の配線を変更するために、FIB加工を用いて半導体集積回路チップの配線を修正するに当たり、半導体集積回路チップの主面上の絶縁膜に金属修正配線をFIBCVDにより形成後、その上を覆うように、金属修正配線よりも耐酸化性または耐腐食性の高い金属被覆膜を、FIBCVDにより形成するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】抵抗素子として機能する配線を有し、かつ面積の小さな半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板SBと、半導体基板SB上に設けられた第2の配線層L2とを備えている。第2の配線層L2は、通常の配線WRと、高抵抗配線REと、通常の配線WRおよび高抵抗配線REを埋め込む絶縁膜8とを含んでいる。通常の配線WRは、第1の銅部10Wと、第1の銅部10Wの底面側および側面側を覆う第1のバリアメタル膜9Wとを有している。高抵抗配線REは、空洞部CVと、空洞部CVの底面側および側面側を覆う第2のバリアメタル膜19Rとを有している。

(もっと読む)

ルテニウムの選択堆積を半導体デバイスの作製に統合する方法

Ruの選択堆積を半導体デバイスの作製に統合することで、Cuメタライゼーションにおけるエレクトロマイグレーションとストレスマイグレーションを改善する方法。当該方法は、熱化学気相成長法によって、Ru3(CO)12先駆体蒸気及びCOガスを有するプロセスガスを用いて、メタライゼーション層(302)上及びバルクCu(322)上にRu金属膜を選択的に堆積する工程を有する。1つ以上の選択的に堆積されたRu金属膜を有する半導体デバイスが記載されている。  (もっと読む)

(もっと読む)

レーザ加工装置及びレーザ加工方法

【課題】レーザCVD法による加工時間を短縮することができるレーザ加工装置及びレーザ加工方法を提供する。

【解決手段】レーザ光8の光路に沿って、スリットマスク20、リレーレンズ11、対物レンズ12、ガスウインドウ14及び被加工物である基板15をこの順に配置する。スリットマスク20は、例えば直線形状スリット23及び迂回形状スリット24を有する。このようなスリット形状のレーザ光を基板15上に像13として結像させる。また、ガスウインドウ14から原料ガスを基板15に向けて供給する。レーザCVD法を用いて基板15上の配線欠陥(断線部)を接続するように導電膜をスリット形状で一括形成することにより、修正加工を行う。

(もっと読む)

半導体装置の製造方法

【課題】 CSPと呼ばれる半導体装置において、微細な開口部内に柱状電極を良好に形成する。

【解決手段】 まず、半導体ウエハ21上に形成された保護膜5の上面に配線7を形成する。次に、配線7を含む保護膜5の上面に例えば感光性ポジ型のポリイミド系樹脂からなるオーバーコート膜10を形成する。次に、配線7の接続パッド部に対応する部分におけるオーバーコート膜10に、フォトリソグラフィ法により、円形状の開口部11を形成する。ここで、配線7上におけるオーバーコート膜10の厚さは10μm程度であり、開口部11の直径は10μm程度である。次に、オーバーコート膜10の開口部11内の配線7の接続パッド部上面に、塩化金属還元気相成長(MCR−CVD:Metal Clloride Reduction Chemical Vapor Deposition)法と呼ばれる金属成膜法により、銅からなる柱状電極12を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース領域およびドレイン領域をシリサイド化しても、リーク電流を可及的に抑えることを可能にする。

【解決手段】半導体領域7を有するシリコン基板2と、半導体領域に離間して形成されたソース/ドレイン領域11a、15a、11b15bと、ソース領域とドレイン領域との間の半導体領域上に形成された絶縁膜9aと、絶縁膜上に形成されたゲート電極10aと、ゲート電極の側部に形成された側壁絶縁膜13aと、第1ソース/ドレイン領域上に形成され、少なくとも{111}面となる表面を有する単結晶シリコン層17a、17bと、少なくとも単結晶シリコン層の{111}面上に形成され、かつ側壁絶縁膜に接する部分を有し、この部分と単結晶シリコン層との界面が単結晶シリコン層の{111}面であるNiSi層21a、21bと、NiSi層に接する第1のTiN膜23a、23bと、を有する第1のMOSFETと、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】低吸湿性かつ低誘電率のF添加SiO2 膜を形成すること。

【解決手段】導電領域間を電気的に分離し、Si、O、Fを含み、SiO2 の網目構造を有する絶縁膜をプラズマCVD法により形成する際に、原料ガスとして、SiF(OCH2 CF3 )3 、SiF(OCH2 C(OR)3 )3 (Rは官能基)、SiF(OCH2 CF2 R)3 (Rは官能基)、SiF(OCH2 C(OR)2 R′)3 (R,R′は官能基)、SiF(OCH2 C(NR2 )3 )3 (Rは官能基)、SiF(OCH2 C(NR2 )2 R′)3 (R,R′は官能基)、SiF(OCH2 CRO)3 (Rは官能基)、SiF(OCH2 CN)3 、SiF(OCH2 NO2 )3 、SiF(OCH2 COOR)3 (Rは官能基)またはSiFn (OCH2 CF2 R)4-n (n=1〜3、Rは官能基)のガスを用いたときに、前記Siに結合した元素がFと置換する反応確率が、前記SiにFが結合している場合のほうが、前記SiにFが結合していない場合よりも小さくなる成膜温度で、前記絶縁膜を形成することを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】SACプロセスによるコンタクト形成において、ゲート電極とコンタクトとのショートを生じにくくし、歩留まりの向上を図ること。

【解決手段】シリコン基板1に直交する面内において、ゲート電極3,4,5のうちゲートマスク6,7に近い第2電極部(窒化タングステン)4及び第3電極部(タングステン)5をゲートマスク6,7よりも幅小となるようにし、ゲート電極3,4,5とセルコンタクトプラグ15との間のショートマージンを増加させた。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】配線間の容量が低く、歩留りや信頼性が高い半導体装置を提供する。

【解決手段】ギャップ110の形成によりキャップ膜108厚が薄くなったまたは消失したとしても、ギャップ110を形成した後に、下層配線107上にキャップ膜111を選択的に成長させることにより、キャップ膜の厚さを確保することができるため、配線間の容量を十分に低減でき、かつ、歩留りや信頼性を高く維持することができる。

(もっと読む)

半導体装置の作製方法

【課題】コンタクトホールを微細化する。この時、微細化されたコンタクトホールであっても、半導体装置における電極のコンタクトを確実なものとする。

【解決手段】珪化膜と樹脂材料膜とからなる多層の層間絶縁膜を形成する。その後、コンタクトホールを形成する。このとき、珪化膜に設けられるコンタクトホールの大きさを樹脂材料膜に設けられるコンタクトホールの大きさよりも小さくする。このような構成は、パターンが複雑化してもコンタクトのとりやすいものとすることができる。

(もっと読む)

単層カーボンナノチューブ製造方法、半導体配線構造の製造方法、フィールドエミッションディスプレイ用電子部品の製造方法及び探針製造方法

【課題】従来に比して用途の自由度が高い単層カーボンナノチューブを容易に製造でき、生産効率を向上し得る単層カーボンナノチューブ製造方法、半導体配線構造の製造方法、フィールドエミッションディスプレイ用電子部品の製造方法及び探針製造方法を提案する。

【解決手段】初期単層カーボンナノチューブ20に外力を与えるだけで、不連続層21に沿って初期単層カーボンナノチューブ20が剥がれることにより、従来用いられていた薬品を使用することなく先端が均一に揃った欠陥のない単層カーボンナノチューブ1を製造できるので、薬品による官能基の修飾も起こらず、用途の自由度が高い単層カーボンナノチューブ1を容易に製造できる。また先端が均一に揃った欠陥のない単層カーボンナノチューブ1の製造を室温で、かつ短時間で行えると共に、フォトリソグラフィも用いることなく容易に製造できるので、単層カーボンナノチューブ1の生産効率を向上できる。

(もっと読む)

41 - 60 / 119

[ Back to top ]