Fターム[5F033PP33]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | 同一膜を2段階以上で成長させるもの (600)

Fターム[5F033PP33]に分類される特許

581 - 600 / 600

マルチチップパッケージ用集積回路チップの製造方法及びその方法により形成されたウエハ及びチップ

【課題】 製造工程を単純化し、かつ製造コスト及び工程時間を短縮できるマルチチップパッケージ用集積回路チップの製造方法を提供すること。

【解決手段】 外縁まで延びる上下面を有し、前記上面から前記外縁に隣接して少なくとも少なくとも一つの第1接触パッドが形成されている半導体基板と、貫通孔が形成され、前記半導体基板の前記外縁に画成されている電気絶縁領域と、前記貫通孔を貫通し、かつ前記第1接触パッドと電気的に接続する接続電極と、を備える。

(もっと読む)

多層配線構造と多層配線構造を有する半導体装置とこれらの製造方法

【課題】 多層配線構造における上層配線の下層配線に対する接続部の形成にあたり、その接続導体の接続部の清浄化処理において問題となる特性劣化を確実に回避する。

【解決手段】 下層配線溝(第1配線溝)11g内の埋込み配線(第1埋込み配線)11bに上層配線(第2埋込み配線)12bが接続導体12cを介して接続される構成において、接続導体12cの形成時の第1埋込み配線11b表面の水素ラジカルないしは水素ブラズマによる清浄化に耐性を有する保護膜7を、この清浄化の雰囲気にさらされ侵食される第2埋込み配線12bが埋め込まれる配線溝12g、接続導体12cが充填される配線接続孔12hの内表面に形成することによって、上述した清浄化に際して絶縁層が侵食されることを回避し、充分な洗浄を行うことができるようにして特性劣化の改善を図る。

(もっと読む)

半導体装置の製造方法

【目的】 ポーラス状に形成される多孔質低誘電率(p−lowk)膜内へのバリアメタルに用いたメタルの拡散を抑制することを目的とする。

【構成】 p−lowk膜を基体上に形成するp−lowk膜形成工程(S102)と、前記p−lowk膜表面側に形成される空孔が前記p−lowk膜内部側の空孔へ連結する連結位置における開口サイズより大きい分子(Ta−R1)を前記p−lowk膜表面に吸着させるTa[N(C2H5)2]5供給工程(S106)と、前記分子(Ta−R1)と反応するNH3を供給し、TaN膜を形成するNH3供給工程(110)と、前記開口サイズより小さい分子(Ta−R2)を吸着させるTaCl5供給工程(S114)と、前記分子(Ta−R2)と反応するNH3を供給し、TaN膜をさらに形成するNH3供給工程(120)と、を備えたことを特徴とする。

(もっと読む)

表示デバイスおよびその製法

【課題】 アルミニウム合金膜と透明電極が直接コンタクトすることを可能とし、バリアメタルの省略を可能にするアルミニウム合金膜を用いた表示デバイスとその製造技術を提供すること。

【解決手段】 基板上に配置された薄膜トランジスタと、透明電極によって形成された透明導電膜、および、これら薄膜トランジスタと透明導電膜を電気的に接続するアルミニウム合金膜を有し、該アルミニウム合金膜と前記透明導電膜の界面には該アルミニウム合金の酸化皮膜が形成されており、該酸化皮膜の膜厚が1〜10nmで、該酸化皮膜中の酸素含有量が44原子%以下である表示デバイスとその製法を開示する。

(もっと読む)

半導体装置及びその製造方法

【課題】メッキ膜厚のウェハ面内均一性を向上させる。

【解決手段】本発明の例に関わる半導体装置は、メタル配線を用いた多層配線構造を有する半導体集積回路が形成され、各々が独立したチップになる複数のチップ領域11と、メタル配線を用いた多層配線構造を有し、複数のチップ領域の各々を取り囲む複数のチップリング12とを備え、複数のチップリング12は、互いに電気的に接続される。

(もっと読む)

デュアル・ダマシン構造におけるMIMキャパシタの構造および製作方法

【課題】MIM(金属−絶縁体−金属)キャパシタ(242/252)構造およびそれを形成する方法を提供すること。

【解決手段】第1パターン(216)および第2パターン(218)を有するデュアル・ダマシン・パターンで、半導体デバイス(200)の誘電体層(214)をパターニングする。第2パターン(218)は、第1パターン(216)よりも深い。第1パターン中の誘電体層(214)の上に導電層(226)を形成し、第1パターン(216)中のこの導電層の上に導電層を形成する。第2パターン(218)の導電層(226)の上に、誘電体層(232)、導電層(234)、誘電体層(236)、および導電層(238)を配設する。導電層(234)、誘電体層(232)、および導電層(226)が、第1のMIMキャパシタ(252)を形成する。導電層(238)、誘電体層(236)、および導電層(234)が、第1のMIMキャパシタ(252)に並列な第2のMIMキャパシタ(242)を形成する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 アスペクト比の大きいコンタクトプラグにおいて、タングステン層等のプラグ用の下地導電層を形成した場合に、剥離による不良を低減することができる半導体装置の製造方法を提供する。

【解決手段】 導電層2の上に形成された層間絶縁層3を有するシリコン基板1において、層間絶縁層3の上にコンタクトホール5を形成するためのマスクを形成するマスク形成工程と、層間絶縁層3をドライエッチング法によりコンタクトホール5を形成するコンタクトホール形成工程と、コンタクトホール5内に導電層6aを形成する導電層形成工程と、前記コンタクトホール内に導電層6aよりも低応力の低応力導電層6bを形成する低応力導電層形成工程とを有する。

(もっと読む)

多層配線構造

【課題】 導電性のパターンを配置することができない領域があっても、CMP後の表面の平坦度を高めることが可能な多層配線構造を提供する。

【解決手段】 支持基板(20)の表面に、第1の領域(10)、該第1の領域を取り囲む環状の第2の領域(11)、及び該第2の領域を取り囲む第3の領域(12)が画定されている。支持基板の上に第1の配線層(M8L)が配置されている。第1の配線層の第3の領域内に配線が形成され、第2の領域内にダミーパターンが形成され、第1の領域内には導電パターンが形成されていない。第1の配線層の上であって、かつ第1の領域内に機能素子(1)が配置されている。

(もっと読む)

カーボンナノチューブ複合材相互接続ビアを用いた集積回路チップ

【課題】 カーボンナノチューブを用いて集積回路の導電性パスを形成することによって、好結果のデバイスを設計する。

【解決手段】 集積回路の導電体パスが、銅であることが好ましい導電性金属に埋設された複数の画一的なカーボンナノチューブを用いて形成される。導電体パスは、導電体層の間に延びるビアを含むことが好ましい。複合材ビアは、導電体上のビアが作られる位置に金属触媒パッドを形成するステップと、誘電体層を堆積しエッチングして空洞部を形成するステップと、空洞部内の触媒の上に実質的に平行なカーボンナノチューブを成長させるステップと、残された空洞部内の空隙を銅で埋めるステップによって形成されることが好ましい。次に、ビア・ホールの上に導電体層が形成される。

(もっと読む)

集積回路相互接続の製作システム及び方法

ウエハ上の導電性表面を処理するシステム(100)は、前記ウエハの前記正面上に実質的に平面化される導電層を形成するように構成された電気化学機械処理(ECMPR)モジュール(106)と、前記ウエハのエッジ領域から導電物質を除去するように構成された、前記ECMPRモジュール内のチェンバーと、前記ECMPRモジュールから前記ウエハを受取り、平面化された前記導電層を研摩して前記金属の相互接続構造を形成するように構成されたCMPモジュールと、前記ECMPRモジュールから前記CMPモジュールへ前記ウエハを移送するように構成されたロボット(111)とを備える。

発明の1つの側面では、ECMPRモジュールは前記ウエハの前記正面上に物質を成膜させる。ECMPRモジュールは、前記ウエハの前記正面から前記導電層の少なくとも一部を除去する。本発明の利点は、成膜された金属の制御性を改善して素子の信頼性及び生産性を改善することを含む。  (もっと読む)

(もっと読む)

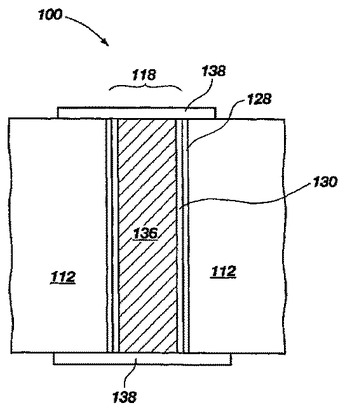

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

半導体構成部品に導電性ビアを形成するための方法が開示される。この方法は、第1の表面及び反対側の第2の表面を有する基板112を設けるステップを含む。この基板に、第1の表面と反対側の第2の表面の間に延びる少なくとも1つの穴118が形成される。基板のこの少なくとも1つの穴を画定している側壁にシード層128が形成され、導電層130でコーティングされ、この少なくとも1つの穴の内部の残りの空間に、導電性材料又は非導電性充てん材料136が導入される。基板を貫通した導電性ビアを、ブラインド・ホールを使用して形成する方法も開示される。本発明の導電性ビアを含む基板を有する半導体構成部品及び電子システムも開示される。  (もっと読む)

(もっと読む)

金属−絶縁物−金属キャパシタおよび配線構造

【課題】 金属−絶縁物−金属キャパシタおよび配線構造を提供する。

【解決手段】 ダマシン工程を利用してMIMキャパシタおよび配線構造を含む半導体装置を製造する。前記MIMキャパシタおよび配線構造は静電容量を増やしつつ同じ深さで形成する。

(もっと読む)

多層配線構造の製造方法

【課題】高集積化、微細化されたパターンにおいて、ビアホール等を良好に埋め込み、かつ電気抵抗率の低い埋め込み型の多層配線構造を提供する。

【解決手段】埋め込み型の多層配線構造の製造方法が、絶縁層に孔部を形成する工程と、孔部の表面に、物理的真空堆積法で、平均膜厚が0.2nm以上で10nm以下である触媒層6、または触媒層の平均膜厚が、触媒層の材料原子の1原子層以上で10nm以下である触媒層6、を形成する工程と、触媒層を触媒に用いた無電解めっき法により、孔部の表面に無電解めっき層7を形成する工程と、無電解めっき層をシード層に用いた電解めっき法で、孔部を電解めっき層8で埋め込む工程とを含む。

(もっと読む)

集積回路デバイス内の相互接続構造体

【課題】 フォトレジスト汚染の問題に悩まされないデュアル・ダマシン構造体を形成する方法を提供すること。

【解決手段】 本発明は、集積回路デバイス内のデュアル・ダマシン相互接続構造体の製造に関する。具体的には、平坦化材料及び拡散障壁材料を用いて、低kの誘電体薄膜内にシングル又はデュアル・ダマシン構造体を形成するための方法が開示される。この方法の好ましいデュアル・ダマシンの実施形態において、最初に誘電体材料にビアを形成し、次にビア内及び誘電体材料上に平坦化材料を付着させ、平坦化材料上に障壁材料を付着させる。次に、リソグラフィにより像形成材料にトレンチが形成され、障壁材料を通して平坦化材料がエッチングされ、トレンチ・パターンが誘電体材料に転写される。これらのエッチング・ステップの過程の間及び該エッチング・ステップの過程に続いて、像形成材料、障壁材料及び平坦化材料が除去される。次に、結果として得られるデュアル・ダマシン構造を金属化することができる。この方法を用いる場合、層間誘電体材料によるフォトレジスト汚染の問題が軽減される。

(もっと読む)

多層配線構造の製造方法

【課題】バリアメタル膜の表面に形成される自然酸化膜の膜厚を薄くし、ボイドの発生を防止した多層配線構造の製造方法を提供する。

【解決手段】埋め込み型の多層配線構造の製造方法において、絶縁層に孔部4を形成する工程と、少なくとも孔部の内壁を覆うように、タンタルと窒素を主成分とするバリアメタル膜5を形成する工程と、バリアメタル膜の表面に形成された酸化膜6を除去する工程と、銅を含むめっき液にバリアメタル膜を浸漬してバリアメタル膜上に無電解銅めっき膜7を形成する工程とを含み、バリアメタル膜に含まれる窒素とタンタルの元素組成比(N/Ta)を、0.3以上で、かつ1.5以下とする。

(もっと読む)

配線構造及びその形成方法

【課題】 Cuを含有する材料に代表されるような層間絶縁膜に対する易拡散性の材料を用いて配線を構成した場合に、前記易拡散性の材料の層間絶縁膜への拡散や材料の剥離を確実に防止するとともに、層間容量を低減させ、しかも高い耐酸化性を保持する。

【解決手段】 Cu配線に対応した保護膜として、当該Cuの拡散防止及びビア孔23形成時のエッチングストッパーとしての機能を有し、しかも低誘電率を示す構造の保護膜16を提案する。この保護膜16は、水素化シリコンカーバイド膜(SiC:H膜)21上にシリコン窒化膜(SiN膜)22が積層されてなる2層構成のものである。

(もっと読む)

銅配線構造およびその製造方法

【課題】銅配線の寿命を増大させ、同時に、密着性を高め、ストレスマイグレーション耐性を向上させる。

【解決手段】Cu16とバリアメタル12、あるいはCu16とキャップ層19との界面近傍に、不純物15を固溶させる、不純物15を析出させる、非晶質Cu14を存在させるまたはCuとの化合物を形成することにより、界面近傍の空孔を減らし、Cuのエレクトロマイグレーション(EM)に対する界面拡散の寄与を減少させ、寿命を増大させ、同時に、密着性を高め、ストレスマイグレーション耐性を向上させた。

(もっと読む)

配線構造の形成方法

【課題】 絶縁膜及びその上のARL膜に埋め込まれた配線同士の間における短絡を防止する。

【解決手段】 基板100上に形成されたFSG膜109及びARL膜110に複数の配線用溝111を形成した後、各配線用溝111が完全に埋まるようにARL膜110上にバリアメタル膜(窒化タンタル膜112)及び配線用導電膜(銅膜113及び114)を順次堆積する。その後、各配線用溝111の外側の銅膜113及び114を研磨により除去した後、各配線用溝111の外側の窒化タンタル膜112を研磨により除去する。その後、研磨時に研磨パッド及び基板100に付着した異物を同時に除去した後、ARL膜110の表面を研磨する。

(もっと読む)

配線構造

【課題】 銅を配線材として用いても、微細な配線構造の形成が可能で、製造の工程数が少なく、低コスト化が可能な配線構造を提供する。

【解決手段】 半導体素子が形成された基板上に絶縁膜103が多層形成され、絶縁膜103に形成された配線溝およびビアホールに金属配線剤が充填されて、配線および接続プラグが形成された配線構造において、絶縁膜103のうち少なくとも一層が対電子線感光性を有する材料から形成されており、絶縁膜103の層間にはバリア絶縁膜104を有し、前記金属配線剤は銅を含むものである。

(もっと読む)

配線構造の製造方法

【課題】 銅を配線材として用いても、微細な配線構造の形成が可能で、製造の工程数が少なく、低コスト化が可能な配線構造の製造方法を提供する。

【解決手段】 配線構造の製造方法が、半導体素子201の上にWプラグ203(下層配線)が形成された基板上に、対電子線感光性を有する材料を含む第二層間絶縁膜204(絶縁膜)を形成する工程と、第二層間絶縁膜204に電子線を照射して、第二層間絶縁膜204を露光する工程と、第二層間絶縁膜204を現像して未露光部を除去し、配線溝および/またはビアホールおよび/またはコンタクトホールを形成する工程とを有する。

(もっと読む)

581 - 600 / 600

[ Back to top ]