Fターム[5F033QQ07]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングの対象 (10,331)

Fターム[5F033QQ07]の下位に属するFターム

Fターム[5F033QQ07]に分類される特許

141 - 160 / 849

異方性エッチング方法、三次元構造体、及び、デバイス

【課題】被対象物を効率よく所望する形状となるようにエッチングすることが可能な異方性エッチング方法、該異方性エッチング方法を用いて形成可能な三次元構造体、及び、該三次元構造体を備えたデバイスを得る。

【解決手段】異方性エッチング方法は、表面に所定形状のマスクを有した基板に対して、SF6とC4F8とを含む混合ガス、又は、SF6とC4F8とO2とを含む混合ガスを用いた反応性イオンエッチングによって、所定条件下で結晶異方性エッチングを行う結晶異方性エッチング工程を有している。本方法と、Bosch法による垂直異方性エッチングを行う垂直異方性エッチング工程とを用いて三次元構造体を製造し、該三次元構造体をデバイスに利用する。

(もっと読む)

半導体装置、スタックドパッケージ型半導体装置および半導体装置の製造方法

【課題】巣及びボイドのないビアを形成する。

【解決手段】半導体基板11を貫通するビアホール51と、ビアホール51の内壁面を被覆する無機絶縁膜13と、無機絶縁膜13の表面に脱水縮合により一端が結合され、他端にメルカプト基又は含硫黄芳香族複素環式基を有するカップリング剤から形成されたカップリング層15と、メルカプト基又は含硫黄芳香族複素環式基に結合された触媒金属16と、触媒金属16上に形成された無電解めっき金属からなるシード層17と、ビアホール51を埋め込みシード層17上に形成された電解めっき金属18からなるビア18aと、を有する半導体装置。

(もっと読む)

半導体装置およびその製造方法ならびに実装体

【課題】 半導体集積回路チップを実装基板に封止樹脂を用いて接合させた時などに、チップを構成する半導体基板に印加される応力を緩和し、応力による半導体素子特性のバラツキを低減させ、また回路動作中に効率的に放熱できるようにする。

【解決手段】 半導体装置は、半導体基板1の表面上に形成された半導体回路形成層2、

半導体回路形成層2内に形成され、半導体回路を構成するトランジスタ、半導体回路形成層2上に形成され、半導体回路と電気的に接続された電極5とを有する。さらにこの半導体装置において、半導体基板1の裏面側には凹部7が形成され、凹部7を含む裏面上に金属膜6が形成される。一例として半導体装置はその電極5と配線基板本体8のパッド電極9とが熱圧着されると共に封止樹脂10で配線基板に接合される。

(もっと読む)

金属充填方法及び金属充填装置

【課題】基板の貫通孔への金属の充填不良を抑制する。

【解決手段】基板100の上面101と下面102との間を貫通する貫通孔110に金属120を充填する方法は、上面101に溶融金属31を供給する工程S40と、下面102における貫通孔110の開口の周囲の圧力を、上面101上に供給された溶融金属31の周囲の圧力よりも相対的に低くすることで、貫通孔110内に溶融金属31を充填する工程S30及びS50と、を備えている。

(もっと読む)

半導体装置及びその製造方法並びにそれを用いた積層型半導体装置

【課題】貫通電極に起因する応力を抑制し、半導体装置の動作を安定化し、半導体装置の信頼性を向上する。

【解決手段】半導体装置は、表面側に活性領域を有する半導体基板1と、半導体基板1の表面から裏面までを貫通するように形成され、導電材からなる貫通電極24と、貫通電極24に囲まれるように形成され、導電材とは異なる応力緩衝部25とを備えている。応力緩衝部25は、貫通電極24の内部であって半導体基板1の表面が横切る位置に形成されている。

(もっと読む)

埋め込みビットラインを備えた半導体装置の製造方法

【課題】埋め込みビットラインの抵抗を減少させることができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板201に活性領域203を分離するトレンチ202をエッチングにより形成するステップと、活性領域203の何れか1つの側壁の一部を露出させた開口部207を有する絶縁膜205を形成するステップと、絶縁膜205上にトレンチ202を部分的に埋め込み、開口部207を埋め込むようにシリコン膜パターン208Aを形成するステップと、シリコン膜パターン208A上に金属膜209を形成するステップと、金属膜209及びシリコン膜パターン208Aを反応させて、埋め込みビットラインとなる金属シリサイド膜211を形成するステップとを含む。

(もっと読む)

半導体装置の作製方法

【課題】コンタクトホールを微細化する。この時、微細化されたコンタクトホールであっ

ても、半導体装置における電極のコンタクトを確実なものとする。

【解決手段】珪化膜と樹脂材料膜とからなる多層の層間絶縁膜を形成する。その後、コン

タクトホールを形成する。このとき、珪化膜に設けられるコンタクトホールの大きさを樹

脂材料膜に設けられるコンタクトホールの大きさよりも小さくする。このような構成は、

パターンが複雑化してもコンタクトのとりやすいものとすることができる。

(もっと読む)

半導体装置

【課題】3次元的に積層された複数の半導体チップを有する半導体装置の製造歩留まりを向上できる技術を提供する。

【解決手段】半導体基板1の第2面1bからパッド3に達する貫通電極17が形成されている。貫通電極17の内部にある貫通空間は、第1孔7および第1孔7よりも孔径の小さい第2孔11によって構成されている。半導体基板1の第2面1bから半導体基板1を貫通して層間絶縁膜2の途中まで第1孔7が形成されている。そして、第1孔7の底部から層間絶縁膜2を貫通してパッド3に達する第2孔11が形成されている。このとき、半導体基板1の第1面1aに形成されている層間絶縁膜2は、第1孔7の底面と半導体基板1の第1面1aとの段差を反映して段差形状になっている。すなわち、第1孔7の底面とパッド3間に存在する層間絶縁膜2の膜厚がその他の場所の層間絶縁膜2の膜厚よりも薄くなっている。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

分離トレンチの形成方法

【課題】隣接デバイスの特性への悪影響を低減するTSV相互接続構造の製造方法を提供する。

【解決手段】第1の主面S1を有する基板を設け、少なくとも一つのTSV穴部と、TSV穴部を囲み残りの基板材料によって分離されるトレンチ状構造3、とをエッチングにより同時に作製する。基板の第1の主面でトレンチ状構造の開口をピンチオフするためと、TSV穴部側壁を平滑にするために、誘電性のライナー2a、2bを堆積し、トレンチ状構造にエアギャップ4を作製する。TSV相互接続10を生成するためにTSV穴部に導体材料を堆積する。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極のための開口部を形成する時に、上部配線層の配線とのミスアラインメント問題が発生しない半導体装置を製造する方法の提供。

【解決手段】第1面及び第1面の反対側に第2面を有する基板を準備する段階と、基板の第1面から基板の厚さ方向に延長して貫通電極が形成される領域に犠牲膜パターンを形成する段階と、基板の第1面上に形成され、犠牲膜パターン上に位置する配線を有する上部配線層を形成する段階と、基板の第2面を部分的に除去して犠牲膜パターンを露出させる段階と、犠牲膜パターンを基板の第2面から除去して配線を露出させる開口部を形成する段階と、開口部内に配線と電気的に接続される貫通電極を形成する段階と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体層の表面から貫通孔絶縁層が後退した場合においても、半導体層と貫通電極との絶縁性を確保する。

【解決手段】貫通孔6には、貫通孔絶縁層7、8を介して貫通電極9が埋め込まれ、貫通孔絶縁層7、8は、半導体層3の表面から後退するようにして形成され、半導体層3と貫通電極9との間には、貫通孔絶縁層7、8の後退部分の対応した凹部10が形成され、貫通電極9の側壁には、凹部10に埋め込まれたサイドウォール絶縁膜12が形成される。

(もっと読む)

半導体装置、その製造方法、および半導体装置を含む半導体パッケージ

【課題】装置特性の低下を防止するとともに、半導体基板と貫通電極の短絡を防止する半導体装置を提供する。

【解決手段】第1面と、第1面と対向してトレンチが形成された第2面とを有する基板と、基板内に形成されたビアホールを充填し、ビアホールの内壁から順にビアホール絶縁膜、障壁膜、および導電性接続部を有してなる貫通ビアと、第2面上に形成されて貫通ビアの一部領域を露出する開口部を有する絶縁膜と、トレンチ内に埋め込まれ、貫通ビアと電気的に接続される再配線と、を有し、絶縁膜は導電性接続部の一部領域と重複する。

(もっと読む)

マザー基板、電子部品の検査方法、電子部品、及び電子部品の製造方法、並びに電子機器

【課題】電子部品の貫通電極において、基板の両面から貫通電極に接触することが必要であることに起因して高度な検査技術が必要である貫通電極の検査を容易にすることができる、マザー基板、電子部品の検査方法、電子部品、及び電子部品の製造方法、並びに電子機器を提供する。

【解決手段】電子部品の製造方法は、マザー基板に区画形成された電子部品の製造方法であって、基板の第1面における複数の区画領域に回路を形成する回路形成工程と、区画領域にて、第1面と第1面の反対面である第2面とを電気的に接続する貫通電極を形成する貫通電極形成工程と、互いに異なる区画領域に位置する貫通電極を第1面にて連結配線で電気的に接続する連結配線形成工程と、第2面にて、連結配線形成工程で電気的に接続された複数の貫通電極に検査プローブを電気的に接続させることによって、貫通電極の機能を検査する機能検査工程と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極の幅を十分に確保して、ゲート電極の抵抗値を小さくすることが可能で、かつゲート電極間の容量を小さくすることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板に設けられ、Y方向に延在する第1の溝15と、半導体基板に設けられ、第1の溝15と交差するXの方向に延在する第2の溝25と、第1及び第2の溝15,25に囲まれ、第2の溝25に露出された対向する第1及び第2の側面26a,26bを有するピラー26と、ゲート絶縁膜28を介して、ピラー26の第2の側面26bに接触するように、第2の溝25の下部に設けられた1つのゲート電極29と、ゲート電極29の側面とピラーの第1の側面26aとの間に配置された空隙と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】パターン疎密差の影響を受けないハードマスク形成法を提供する。

【解決手段】基板101上に、第1から第3の膜111,112,113およびレジスト層114を形成した後、疎部R1と密部R2が存在するパターンを前記レジスト層に形成して前記第3の膜をエッチングする。次に、前記第3の膜及び前記レジスト層をマスクとして、密部R2内では前記第2の膜が残存するが、疎部R1内では前記第1の膜が露出するまで、前記第2の膜を除去する。その後CXFYHZガスを使用して、第5の膜115を、疎部R1内に露出した前記第1の膜上に第1の膜厚T1で形成し、密部R2内に残存する前記第2の膜上には膜厚T1よりも薄い第2の膜厚T2で形成する。膜厚T1の前記第5の膜で疎部R1内に露出した前記第1の膜を保護しながら密部R2内に残存する前記第2の膜を除去し、最後に、前記第3から第5の膜を除去して前記第2の膜をハードマスクとする。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

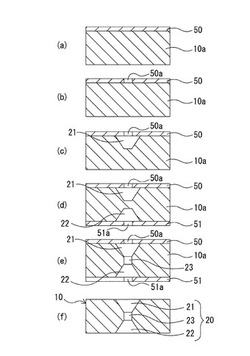

貫通配線基板の製造方法及び貫通配線基板

【課題】貫通孔の底面部付近において、導電層をカバレッジ良く形成し、接触不良がなく、電気的な安定性を向上させた貫通配線を、工程やコストを増加することなく形成する。

【解決手段】半導体基板の一方の面に第一絶縁層を介して導電部を形成する第一工程、ドライエッチング法により半導体基板の他方の面側から第一絶縁層が露呈するように貫通孔を形成する第二工程、貫通孔の内壁面および底面に第二絶縁層を形成する第三工程、第二絶縁層及び第一絶縁層のうち貫通孔の底面に位置する部分を除去し導電部を露呈する第四工程、第二絶縁層上に導電層を形成し該導電層を導電部と電気的に接続する第五工程、を有し、第四工程において、第二絶縁層に続いて導電部の一部をエッチングすると共に、エッチングにより除去された第一金属成分とエッチングガス成分とからなる第一副生成物を、貫通孔の底面部及びその近傍に位置する内壁面部に堆積させ、テーパー部を形成する。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においてインターフェースチップからコアチップへのクロック信号の供給を不要とする。

【解決手段】外部から供給されるコマンド信号CMD及びクロック信号CKを受けて、各々がクロック信号CKに同期し、且つ、互いにタイミングが異なる複数のリード制御信号R1,R2を出力するリードタイミング制御回路100を有するインターフェースチップIFと、インターフェースチップIFに積層され、コマンド信号CMDが示す動作をリード制御信号R1,R2に同期してそれぞれ実行する複数の内部回路を有するコアチップCC0〜CC7とを備える。本発明によれば、コアチップに内でのレイテンシ制御が不要となることから、コアチップにクロック信号を供給する必要がなくなる。

(もっと読む)

141 - 160 / 849

[ Back to top ]