Fターム[5F033QQ07]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングの対象 (10,331)

Fターム[5F033QQ07]の下位に属するFターム

Fターム[5F033QQ07]に分類される特許

101 - 120 / 849

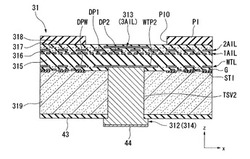

半導体装置

【課題】とりわけ表面マークの下部に配線タングステンパッドがある場合でも、表面マークのコントラスト低下を抑制する。

【解決手段】メモリチップ31は、配線タングステン階層WTL、第1、第2、第3アルミニウム配線階層1AlL,2AlL,3AlLを備える多層配線構造を備える。各配線層の間には、第1、第2、第3層間絶縁膜315,316,317がそれぞれ形成され、第3アルミニウム配線階層3AlLとポリイミド膜PIとの間には、第4層間絶縁膜318が形成されている。第1のダミーパターンDP1は、第1アルミニウム配線階層1AlLに形成され、第2層間絶縁膜316に覆われている。第2のダミーパターンDP2は、第2アルミニウム配線階層2AlLに形成され、第3層間絶縁膜317に覆われている。第2ダミーパターンDP2は、第1ダミーパターンDP1よりも幅が長い。

(もっと読む)

半導体チップ

【課題】金属原子の拡散に起因する素子特性の劣化を抑制する。

【解決手段】半導体チップは、半導体基板10と、半導体基板10を貫通する貫通電極20と、半導体基板10を貫通する金属柱40と、アライメントマーク47と、絶縁性を有する筒状の絶縁膜50とを有する。アライメントマーク40は、半導体基板10の外部に露出した金属柱40の端部によって形成されている。筒状の絶縁膜50は、半導体基板10に形成されており、金属柱40を取り囲んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板を貫通する貫通電極の周囲に形成される環状の絶縁分離部において、絶縁分離部を構成する酸化膜の応力により絶縁分離部周囲の半導体基板が変形する。

【解決手段】絶縁分離部の基板側に深さ方向に圧縮応力を与える第1の膜4を形成し、第1の膜4上に深さ方向に引張応力を与える第2の膜6膜を形成し、その際、第1及び第2の膜の膜厚を圧縮応力と引張応力とがほぼ釣り合うように調整する。

(もっと読む)

半導体装置の製造方法

【課題】

本発明は、簡便に形成できて、チャージアップしにくいハードマスクを用いた半導体装置の製造方法を提供することを目的とする。

【解決手段】

半導体装置の製造方法であって、半導体基板上に形成された被加工膜上に、アミン化合物と水素化アルミニウムとの錯体を含有するアルミニウム膜形成用材料を塗布して、塗布膜を形成する工程と、前記塗布膜に対して、加熱処理および光照射処理から選ばれる少なくとも一種の処理を行いアルミニウム膜を形成する工程と、 該アルミニウム膜をエッチングしてハードマスクを形成する工程と、前記ハードマスクをマスクにして被加工膜をエッチングする工程を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板に形成された開口部の側壁全体を均一に成膜することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一実施形態に係る半導体装置の製造方法は、底壁及び複数の凹部を有する側壁により構成された開口部を素子が形成された半導体基板に形成し、前記開口部側から蒸着又はスパッタリングを行い、前記底壁及び前記側壁の各凹部の前記底壁側に成膜部材を堆積させ、前記半導体基板に所定の電圧を印加しつつスパッタリングを行うことにより前記成膜部材を前記側壁の各凹部の前記開口部側に堆積させることを特徴とする。

(もっと読む)

半導体装置、回路基板および電子機器

【課題】半導体基板と貫通電極との絶縁を確実とする半導体装置を提供する。

【解決手段】半導体装置10の一方の面14から他方の面16に形成された電極パッド24の裏面に到達する貫通電極13を形成した半導体装置10であって、他方の面16側には第1の絶縁膜20を介して電極パッド24が設けられ、貫通電極13を構成する貫通孔21と第1の絶縁膜20との境界面に、一方の面14側の開口よりも大きい開口を有し、貫通電極13を形成する際、他方の面16側の貫通孔21開口部内周に貫通電極13を構成する導電材料と電極パッド24との間に第2の絶縁膜23を備え、貫通孔21内壁面および第2の絶縁膜上に第3の絶縁膜22が設けられる。

(もっと読む)

電極が埋設されたウエーハの加工方法

【課題】電極を被覆している二酸化珪素膜をエッチングすることなく、また電極をエッチングすることなくシリコン基板の裏面から電極を露出させることができる加工方法を提供する。

【解決手段】ウエーハの表面に保護部材を貼着する保護部材貼着工程と、シリコン基板21の裏面を電極214を露出させることなく研削する工程と、シリコン基板の裏面をエッチング液によってエッチングしシリコン基板の裏面に電極を露出させる工程とを含み、エッチング工程は、シリコンに対してエッチングレートが高いエッチング液を用いてシリコン基板をエッチングして二酸化珪素215膜が被覆された電極をシリコン基板の裏面に不完全に露出させる工程と、シリコンをエッチングするとともに二酸化珪素に対してエッチングレートが低いエッチング液を用いてシリコン基板をエッチングして二酸化珪素膜で被覆された電極をシリコン基板の裏面から突出させる工程とを含んでいる。

(もっと読む)

半導体積層体の製造方法

【課題】信頼性の高い半導体積層体を製造することのできる半導体積層体の製造方法を提供する。

【解決手段】貫通電極用溝2が形成されたウエハ1の貫通電極用溝2を有する面に、半導体加工用テープ4を介して支持体5を積層する工程(1)と、ウエハ1を半導体加工用テープ4と反対側の面から研削し、貫通電極用溝2を露出させる工程(2)と、露出した貫通電極用溝2に電極部6を形成する工程(3)と、ウエハ1の半導体加工用テープ4と反対側の面に封止樹脂層7を形成する工程(4A)と、封止樹脂層7を介してウエハ1にダイシング用テープ8を貼り合わせ、半導体加工用テープ4及び支持体5を剥離する工程(4B)と、ウエハ1を個片化して半導体チップを作製する工程(5)と、前記半導体チップを、封止樹脂層7を介して他の半導体チップ又は基板に積層する工程(6)とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】デバイスの損傷を防ぎ、保護することができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】基板1上に配線層3が形成された第1の積層体10と、第1の積層体10の主面上にその主面を重ねて配設され、基板上11に配線層13が形成された第2の積層体20と、第1の積層体10または第2の積層体20の少なくとも一方の基板上に形成された機能素子とによって構成された半導体装置100に対して、第1の積層体10及び第2の積層体20の主面に垂直な方向から見て、機能素子2,12の周囲に配設され、第1の積層体10と第2の積層体20の界面を貫通する貫通金属部材29を設ける。また、この貫通金属部材29は、第1の積層体10と第2の積層体20を接合した後に、第1の積層体10と第2の積層体20を貫通する貫通孔を設け、貫通孔内に金属を埋め込むことで形成できる。

(もっと読む)

自己整合シリサイドの形成方法、半導体デバイスの製造方法、および半導体構造物

【課題】製造工程の増大を抑制し、コンタクト抵抗および界面抵抗の増大を防止する。

【解決手段】実施形態において、シリコン層は、ゲートラストスキームを用いた機能的ゲート電極の製造後に、形成される。初期的な半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域、不純物領域の上に形成された犠牲膜、犠牲膜の上に形成された絶縁層、絶縁層の上に形成された絶縁層を備える。ビアは、初期の半導体構造物の絶縁層へ、および、コンタクト開口部が絶縁層に形成されるように絶縁層の厚さを通り抜けて、パターン化される。次に、絶縁層の下にある犠牲膜は、絶縁層の下に空隙を残して除去される。次に、金属シリサイド前駆体は、空隙スペースに配置され、金属シリサイド前駆体は、アニールプロセスを通じてシリサイド層に変換される。

(もっと読む)

半導体装置の製造方法

【課題】膜の形成によって生じる半導体基板の反りを緩和できる、半導体装置の製造方法を提供する。

【解決手段】SiC半導体基板10の主面上にイオン注入用マスク材18を形成する。マスク材は半導体基板とは異なる熱膨張係数を有する。レジスト膜20をマスクとしてドライエッチングにより複数の装置形成領域の間の領域上(ダイシングライン)14に切欠き部16aを有するマスク用膜16を形成する。イオン注入などの工程を経て半導体装置を形成後、ダイシングラインに沿って各装置形成領域に分離する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、被加工材にパターンを形成するためのマスクの選択比を向上させ、プロセスコストの低減、歩留りの向上を可能とする。

【解決手段】被加工材上に所定パターンの有機膜を形成し、所定パターンの有機膜中に金属元素を導入し、金属元素が導入された所定パターンの有機膜を用いて、被加工材をエッチング処理する。

(もっと読む)

半導体チップ及びその製造方法、並びに半導体装置

【課題】ダイシング工程で発生し得る裏面側のチッピングが、貫通電極が存在するアクティブエリアにまで侵入することを防止する。

【解決手段】メモリチップ1Aは、スクライブセンターSC側から、スクライブエリアSA、ガードリングエリアGA、及びアクティブエリアAAという領域に区分けされる。スクライブエリアSAの層間絶縁膜内には、メモリチップ1Aの表面側のチッピングを防止するための第1、第2クラックストップ3a,3bが設けられている。ガードリングエリアGAの表面側には、ガードリング4が設けられている。一方、ガードリングエリアGAの半導体基板10側(メモリチップ1Aの裏面側)には、裏面側のチッピングを防止するための溝5Aが設けられている。この裏面チッピング防止溝5Aによって、チッピングがサポート貫通電極2a及び信号等用貫通電極が形成されている領域に侵入することを防ぐことができる。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

表示装置及びマスク

【課題】マスクの枚数を増やすことなく、ストレージキャパシタの電極間から半導体パターンを除去して高画質化を実現させる表示装置及びその製造方法を提供する。

【解決手段】本発明によるTFTパネルの製造では、半導体パターンとTFTのドレイン電極とを、同じマスクを利用したエッチングで同時にパターニングする。一方、画素電極の直下に形成される絶縁膜のパターニングには別のマスクを利用する。ドレイン電極を覆う絶縁膜の領域では、中央部の全体を感光させ、周辺部を半分の厚みまで感光させる。ストレージ電極の上方を覆う絶縁膜の領域は薄い一部を残して感光させる。ドレイン電極を覆う誘電膜をエッチングしてドレイン電極を露出させるとき、絶縁膜のその薄い一部がその下地の誘電膜を保護する。その後、絶縁膜のその薄い一部を画素電極の一部に置換し、保護された誘電膜を隔ててストレージ電極と対向させる。

(もっと読む)

素子付き基板、赤外線センサー、および貫通電極形成方法

【課題】マイグレーションの問題を生じることなく、微細でアスペクトの高く絶縁特性に優れた絶縁膜を備えた貫通電極を有する素子付き基板、赤外線センサーおよび貫通電極形成方法を提供する。

【解決手段】予め、素子回路形成前のベース基板にビアホールを形成し、前記ベース基板の素子回路形成面と前記ビアホールの内面に熱酸化により絶縁膜を形成する熱酸化を行なう。前記熱酸化工程後に前記ビアホール形成部に導電部を有する素子回路を形成した後、前記素子回路形成工程後に前記ビアホールに導電体を埋め込み形成するようにしている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造コストの増大を抑制しつつ、簡易な構成で、絶縁膜とさらに上部に形成された絶縁膜との界面の電荷を低減することができる半導体装置の製造方法の提供を目的とする。

【解決手段】本発明にかかる半導体装置の製造方法は、(a)SiC半導体を用いた基板を用意する工程と、(b)前記基板の表層部において、前記基板の素子領域を囲むように、リセス構造と前記リセス構造の下部にガードリング層とを形成する工程と、(c)前記ガードリング層を覆って、第1絶縁膜を形成する工程と、(d)前記第1絶縁膜を覆って、前記第1絶縁膜とは異なる材質の第2絶縁膜を形成する工程と、(e)前記第1絶縁膜上に蓄積する電荷とは逆電荷のイオンを、前記工程(d)の前、又は、前記工程(d)中、又は前記工程(d)の後に照射する工程とを備える。

(もっと読む)

半導体装置、製造方法、および電子機器

【課題】製造コストの低減を図ることができる。

【解決手段】シリコンウェハ31の上面側の内部にメタルパッド32が形成され、シリコンウェハ31の上面にガラスシール材33が積層され、メタルパッド32がシリコンウェハ31の上面に露出するようにシリコンウェハ31およびガラスシール材33に加工された開口部にストッパ層34が形成される。そして、シリコンウェハ31の下面からストッパ層34まで開口するように縦孔35が形成され、縦孔35の先端部においてストッパ層34を介してメタルパッド32に電気的に接続され、シリコンウェハ31の下面まで延在するようにメタルシード層37が形成される。本発明は、例えば、固体撮像装置に適用できる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】貫通孔の側面のスキャロップ形状及びアンダーカットを修復する。

【解決手段】半導体装置は、第1の基板と、第2の基板と、前記第1の基板と前記第2の基板との間に配置され、前記第1の基板と前記第2の基板とを接着する接着層と、を備え、前記第2の基板及び前記接着層には、前記第2の基板及び前記接着層を貫通する貫通孔が形成されており、前記貫通孔の側面には、凹部が形成されており、前記凹部には、少なくとも有機骨格を有する樹脂が埋め込まれており、前記貫通孔の中には、導電体が形成されている。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

101 - 120 / 849

[ Back to top ]