Fターム[5F033QQ07]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングの対象 (10,331)

Fターム[5F033QQ07]の下位に属するFターム

Fターム[5F033QQ07]に分類される特許

121 - 140 / 849

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

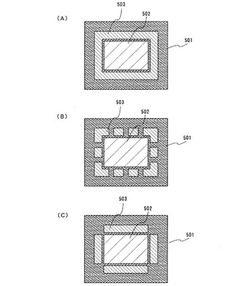

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

【課題】基板を貫通するトレンチによって複数の部分領域に分割されてなる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法であって、部分領域の側壁に導電層を形成するメリットだけを享受して、該導電層の形成に伴う悪影響を排除することのできる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ce,Cea〜Ced,Cek,Celに分割され、前記複数の部分領域のうち、一部の部分領域Cea〜Cedの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、トレンチ31aに絶縁体31bが埋め込まれてなる領域分割基板A20とする。

(もっと読む)

配線形成方法、及び配線形成装置

【課題】絶縁層が積層された導電層に該絶縁層を貫通するカーボンナノチューブが接続される配線構造にて電気的特性を向上することのできる配線形成方法、及び該方法を用いる配線形成装置を提供する。

【解決手段】

下部配線層32に積層された絶縁層34を貫通するホール35に、その内表面の全体が含まれるように触媒層36,37を形成した後、ホール35の内部にシースShが形成され、且つホール35の内壁面35aに対するシースの厚さがホール35の底壁面35bに対するシースShの厚さよりも小さくなるようにプラズマを生成する。そして、ホール35の内壁面35aに形成された触媒層36,37をプラズマ中のスパッタ粒子Spによって除去した後、ホール35の底壁面35bに残された触媒層36,37を用いて該底壁面35bからカーボンナノチューブ38を形成する。

(もっと読む)

半導体装置

【課題】基板を介したクロストークを抑制でき、放熱性が高い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置1は、半導体基板10を備える。前記半導体基板の内部には空洞11が形成されている。また、前記半導体基板の内部には、前記空洞を前記半導体基板の上面に連通させる連通孔12も形成されている。前記半導体装置は、さらに、前記空洞及び前記連通孔の内面上に設けられた絶縁膜13と、前記空洞及び前記連通孔の内部に埋め込まれ、熱伝導率が前記絶縁膜の熱伝導率よりも高い伝熱部材14と、前記半導体基板における前記空洞の直上域に形成された素子21,22と、を備える。

(もっと読む)

ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法

【課題】ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法を提供する。

【解決手段】特に分子の特性評価に適用される本発明によると、以下を備える素子が作られる:ナノ物体(2)に接続される上部接触パッド(8)を備えた上部層(16);外部電気システム(4)に接続される下部接触パッド(12)を備えた下部層(18);前記下部層上にあり、前記下部パッドと接触する電気的貫通ビア(22)を備えた接着層(20);前記接着層と前記上部層の間にあり、前記上部パッドを前記下部パッドに接続するための導電ライン(25)及び電気的ビア(26)を備えた少なくとも2つの層(22、24)。

(もっと読む)

半導体装置及びその製造方法

【課題】凹形状を有するホールの内壁側面上に側壁保護膜の一部を残留させることにより、ホールの内壁側面を平滑化する。後の工程でホール内に材料を埋設する際にも、ボイドを発生させることなく優れた埋設性でホール内を材料で埋設させる。

【解決手段】半導体基板の裏面上にマスクを設ける工程と、マスクを用いて半導体基板を貫通すると共に凹形状の内壁側面を有するホールであって内壁側面が側壁保護膜で覆われたホールを形成する工程と、側壁保護膜の一部を残留させるようにマスクを除去する工程と、を有する半導体装置の製造方法。

(もっと読む)

電子デバイス及びその製造方法

【課題】バンプを排除した積層構造を備える電子デバイス、及びその製造方法を提供する。

【解決手段】本発明に係る電子デバイス1は、積層された複数枚の基板11〜13を含む。複数枚の基板は、それぞれ、板面を重ね合わせて積層され、1以上の貫通電極2を含んでいる。また、1以上の貫通電極2は、複数枚の基板11〜13のうち、2枚以上の基板11〜13にわたって延在する連続導体である。本発明に係る電子デバイス1は、このように、各基板の板面同士が重ね合わせられ、2枚以上の基板11〜13にわたって延在する連続導体である貫通電極2を備えている。したがって、本発明に係る電子デバイスは、複数枚の基板11〜13が、バンプを用いることなく、積層された構造を有している。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

パターンの形成方法

【課題】LELEプロセスよりも少ない工程数で、フォトリソグラフィ技術を2度使用することなく、微細なホール又はトレンチパターンを形成する方法を提供すること。

【解決手段】被処理体の上にレジスト膜を成膜し、成膜した前記レジスト膜をパターニングする、レジスト膜形成工程と、前記被処理体及び前記レジスト膜を被覆するようにスペーサ膜を成膜して、前記スペーサ膜で囲まれた凹部を形成する、スペーサ膜成膜工程と、前記凹部の底面にある前記被処理体及び前記レジスト膜の上面を露出させると共に、前記レジスト膜の側面側に前記スペーサ膜が残るようにエッチングして、前記凹部から第1の開口部を形成する、第1開口部形成工程と、前記レジスト膜を除去することにより第2の開口部を形成する、第2開口部形成工程と、を含むパターンの形成方法。

(もっと読む)

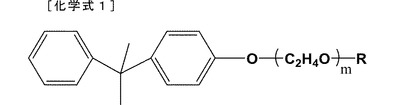

銅めっき溶液およびこれを用いた銅めっき方法

【課題】高縦横比のビアホールを埋め込むのに好適な銅めっき溶液および銅めっき方法を提供する。

【解決手段】シード層を有する基板を浸漬し、水、銅供給源、電解物質、塩素イオン、第1添加剤、第2添加剤、および第3添加剤を含み、前記第1添加剤は、化学式1に示す化合物である銅めっき溶液を用いて銅めっきを行う。

(式中、Rは、水素原子または炭素原子数1〜6のアルキル基であり、mは、平均重合度であり6〜14の実数である。)

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コンタクトとアクティブエリアとの間のショートマージンを確保できる半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板の上層部分に形成され、前記上層部分を第1方向に延びる複数本のアクティブエリアに区画する複数本の素子分離絶縁体と、前記アクティブエリアに接続されたコンタクトと、を備える。そして、各前記アクティブエリアの上面のうち、前記第1方向における一部の領域には、前記第1方向に対して直交する第2方向において前記アクティブエリアの全体にわたって凹部が形成されている。前記第1方向において、隣り合う前記アクティブエリアにそれぞれ接続された2本の前記コンタクトの位置は相互に異なる。前記コンタクトは前記凹部の側面に接し、底面には接していない。

(もっと読む)

半導体装置

【課題】貫通電極の形成に時間を要さず、貫通電極内でのボイドの発生を抑制できる半導体装置、およびこの半導体装置の製造方法を提供すること。

【解決手段】半導体装置1は、孔111が形成された絶縁性あるいは半導体の層11と、層11の孔111内に設けられた貫通電極12と、を備える。貫通電極12は、シード層121と、めっき層122と、を備える。シード層121は、孔111の底面111Aを覆う。また、シード層121は、孔111の側面111Bのうち、孔111の開口から、孔111の開口と孔111の底面111Aとの間の所定の位置までの第1の領域を未被覆とし、この第1の領域(未被覆領域)111B1を除いた第二の領域を被覆している。めっき層122は、シード層121と、未被覆領域111B1の少なくとも一部を覆う。

(もっと読む)

垂直集積システム

【課題】コストのかかる空間をとらずに電子部品内に個別パッシブ部品を組み込むことが可能な垂直集積システムを提供する。

【解決手段】集積回路システム100は、半導体ダイ110の前面上に製造された第一のアクティブ層と、半導体ダイ110の裏面上の第二の予め製造された層とを含み、その第二の予め製造された層は、その中に埋め込まれた電気部品を有し、その電子部品は、少なくとも一つの個別パッシブ部品140を含む。また、集積システム100は、第一のアクティブ層及び第二の予め製造された層を結合する少なくとも一つの電気経路150も含む。

(もっと読む)

ヴィア構造およびその作製方法

【課題】より小さな径の基板貫通ヴィアが形成できるようにする。

【解決手段】基板101の回路が形成されている主表面101a側から所望の孔径の範囲で形成可能な深さに形成された第1孔部102と、基板101の裏面側から形成されて第1孔部102に接続する第2孔部103と、第1孔部102の内部に形成された第1孔部配線104と、第1孔部配線104に接続して基板101の主表面101a側に形成された表面配線層105と、第2孔部103の内部に第1孔部配線104に接続して形成された第2孔部配線106と、第2孔部配線106に接続して基板101の裏面側に形成された裏面配線層107とを備える。

(もっと読む)

半導体装置

【課題】埋め込み電極プラグからの応力伝播による半導体装置の特性変動、および、埋め込み電極プラグからの電気的雑音伝播による、半導体装置の動作不安定化を防止する。

【解決手段】半導体基板と、半導体基板上に形成された半導体素子を有する素子形成領域と、半導体基板を貫通するように設けられた1以上の埋め込み電極プラグと、素子形成領域と埋め込み電極プラグの間の半導体基板内に位置するトレンチ内に埋め込まれた溝型電極と、を有する半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】ヒートシンクに生じる不具合を低減すること。

【解決手段】半導体装置は、第1面及び第2面を有し、第1面と第2面とを貫通するバイアホールを有する半導体基板と、第1面上に、バイアホールの開口と少なくとも部分的に重複するように形成された配線又は電極と、第2面上に形成され、バイアホールの開口と少なくとも部分的に重複する開口を有する応力緩衝層と、応力緩衝層上からバイアホールの内壁面に沿って延在し、配線又は電極と電気的に接続されたヒートシンクと、を備える。バイアホールの第2面における開口の大きさは、第1面における開口の大きさよりも大きい。応力緩衝層の熱膨張係数は、ヒートシンクの熱膨張係数未満である。

(もっと読む)

半導体装置およびその製造方法

【課題】 表面側から特性試験が行える縦型の半導体装置を提供する。

【解決手段】 半導体装置10では、半導体基板11は第1の面と、第1の面に対向する第2の面を有している。半導体素子12は半導体基板11のダイシングライン14、15で囲まれた矩形状格子に形成されるとともに、第1の面に形成された第1電極26と、第2の面に形成された第2電極28とを有している。電流は第1電極26と第2電極28の間に流れる。貫通電極16は半導体基板11のダイシングライン14、15で囲まれていない領域に形成されるとともに、一端が第1の面上に延在し、他端が第2電極28と電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

半導体装置の製造方法

【課題】携帯電話などのフロントエンドモジュールに使用されているハイパワーアンプは、シリコン系CMOS集積回路をベースとするデバイスであるが、その出力段に多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成したLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。このポリシリコンプラグは、熱処理に起因する固相エピタキシャル成長により収縮し、シリコン基板に歪が発生する。

【解決手段】本願発明は、LDMOSFET等の半導体装置の製造方法において、基板の表面からエピタキシャル層を貫通するホールを形成し、ポリシリコンプラグを埋め込むに際して、ホールの内面に薄膜酸化シリコン膜が存在する状態で、ポリシリコン部材の堆積を行うものである。

(もっと読む)

121 - 140 / 849

[ Back to top ]