Fターム[5F033QQ08]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングの対象 (10,331) | 導電膜 (3,144)

Fターム[5F033QQ08]に分類される特許

81 - 100 / 3,144

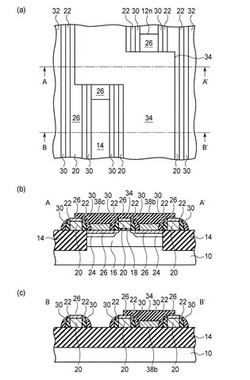

半導体装置の製造方法

【課題】局所配線を有する半導体装置に関し、位置ずれに起因する電気特性や歩留まりの低下を抑制しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に、隣接して配された第1の配線及び第2の配線を形成し、第1の配線の側壁に第1の側壁絶縁膜を、第2の配線の側壁に第2の側壁絶縁膜を形成し、第1及び第2の配線、第1及び第2の側壁絶縁膜が形成された半導体基板上に導電膜を形成し、第1及び第2の配線上の導電膜を選択的に除去し、第1の配線と第2の配線との間の領域に、導電膜により形成され、第1及び第2の側壁絶縁膜によって第1及び第2の配線から隔てられた第3の配線を形成する。

(もっと読む)

エッチング液

【課題】 銅及びモリブデン積層膜を一液でエッチングでき、しかも工業的に好ましい形状にエッチングできるエッチング液を提供する。

【解決手段】 過酸化水素、グリシン、燐酸及び水を含むエッチング液を、銅及びモリブデン積層膜のエッチングに用いる。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いた表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供する。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させること

ができる。

(もっと読む)

半導体装置とその製造方法

【課題】 実施形態は、製造工程が簡便な手法によって製造した半導体装置を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、実施形態にかかる半導体装置は、基板と、基板上に触媒金属膜と、触媒金属膜上にグラフェンと、前記グラフェン上に層間絶縁膜と、前記層間絶縁膜を貫通するコンタクトホールと前記コンタクトホールにカーボンナノチューブを水素、窒素、アンモニアと希ガスの中から選ばれる1種以上のガスのプラズマで処理した前記触媒金属膜上に又は前記層間絶縁膜を貫通するカーボンナノチューブを水素、窒素、アンモニアと希ガスの中から選ばれる1種以上のガスのプラズマで処理した前記触媒金属膜上に備えることを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】銅埋め込み配線を主要な配線層とする半導体集積回路装置に於いても、通常、ワイヤボンディング特性を確保するために、最上層配線層をアルミニウム系パッド層とすることが多い。このアルミニウム系パッド層は、一般に、配線層(電源配線、信号配線等の一般相互接続配線)としても使用されている。しかし、このような一般相互接続配線は、配線長が比較的長いためアンテナ効果により、プラズマ処理時にデバイスにダメージが入り易い等のデメリットがある。

【解決手段】本願発明は、メタル多層配線系が、下層の埋め込み型多層配線層と上層の非埋め込み型アルミニウム系パッドメタル層を有する半導体集積回路装置に於いて、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に電源リング配線を有しないものである。

(もっと読む)

半導体装置及びその製造方法

【課題】配線コーナーでの電子散乱を減らし、配線の抵抗率の増大を抑制する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に形成され、配線溝を有する層間絶縁膜とを備える。さらに、前記装置は、前記配線溝内に形成された配線を備える。さらに、前記配線溝の底面と側面との間の角部の曲率半径は、前記配線の配線幅の1/10以上である。

(もっと読む)

半導体装置

【課題】半導体装置の最上層の保護膜のクラックを防いで、半導体装置の信頼性の向上を図ることのできる技術を提供する。

【解決手段】ボンディングパッドBP1を長方形状とし、ボンディングパッドBP1のワイヤボンディング領域BP1wでの保護膜5の重なり幅を、ボンディングパッドBP1のプローブ領域BP1pでの保護膜5の重なり幅よりも広くなるように、ボンディングパッドBP1上の保護膜5に開口部6を形成する。

(もっと読む)

半導体装置の製造方法

【課題】基板を貫通する電極の形成に適用できる新規な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に半導体素子を形成する工程と、半導体基板に孔を形成する工程と、半導体素子の上方と孔の内壁および底を覆うように絶縁膜を形成する工程と、異方性エッチングにより、半導体素子の上方と孔の底の絶縁膜を除去する工程と、孔の底に金属拡散防止膜を形成する工程と、孔に導電膜を埋める工程とを有する。

(もっと読む)

銅および銅合金のエッチング液

【課題】

本発明の課題は、銅層と銅酸化物層および/または銅合金層とを含む金属積層膜パターンを精度良くエッチング加工し、優れた断面形状を形成し、かつ実用性に優れた安定で液寿命の長いエッチング液組成物、およびかかるエッチング液組成物を用いたエッチング方法を提供することにある。

【解決手段】

本発明は銅層と銅酸化物層および/または銅合金層とを有する金属積層膜を、過硫酸塩および/または過硫酸溶液0.1〜80重量%と、りん酸0.1〜80重量%と、硝酸および/または硫酸0.1〜50重量%とを含有するエッチング液組成物であり、さらに塩化物イオンやアンモニウムイオンを加えることで、エッチングレートや断面形状を容易に制御することが可能となるエッチング液組成物またはエッチング方法に関する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ダマシン構造のCu配線を有する半導体装置の製造において熱処理工程が行われた場合の、層間絶縁膜であるCF膜からのフッ素の拡散を防止し、リーク電流の増加を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】ダマシン配線構造を有する半導体装置であって、フッ素添加カーボン膜からなる層間絶縁膜と、前記層間絶縁膜に埋め込まれた銅配線と、を備え、前記層間絶縁膜と前記銅配線との間には、前記銅配線に近接するバリアメタル層と、前記層間絶縁膜に近接するフッ素バリア膜が形成されている、半導体装置が提供される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子埋設用凹部上端部の肩落ちによるキャパシタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】半導体装置は、保護層80は、凹部(孔23)の上端部の周囲に設けられている。この保護層80は、保護層80と同一層に位置しており、論理回路領域に位置している多層配線層を構成する絶縁層よりも誘電率が高い材料で構成されており、機械強度に優れた部材となる。これにより、凹部(孔23)上端部の肩落ちを抑制し、キャパシタ高さのバラツキを抑制する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の素子形成領域へのクラックなどの伝播を確実に防止する。

【解決手段】ウェハ1上の素子形成領域を覆うガード領域4の外側に、n型拡散層15を形成する。n型拡散層15の上には、導電性リング33,48,58を形成する。最上層の導電性リング48の上に、導電層65を形成する。導電層65の端面65Sは、導電性リング58の端面58Sから距離L1だけ内側に形成し、導電性リング58の上面の一部を露出させる。この後、半導体基板をアミン系薬液に浸すと、n型拡散層15と導電層65の間の導電性プラグ33,48,48の導電性材料を溶出し、スリットが形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波特性の悪化を防ぎ、耐湿性を向上させる。

【解決手段】半導体基板1の主表面上の素子領域内に、ドレイン電極2が設けられている。一端がドレイン電極2に接続されたドレイン配線5が主表面上に設けられている。主表面上の素子領域外に、ドレイン配線5とは離間したドレイン電極パッド12が設けられている。Auメッキ層9が主表面上に設けられ、主表面との間に空隙10が形成されている。空隙10はドレイン配線5の一端とドレイン電極2を内包する。硬化されたポリイミド膜14が空隙10の開口部11を閉塞し、ドレイン電極パッド12を覆うことなく、ドレイン配線5の他端を覆っている。空隙10の内面に撥液膜15が設けられている。硬化されたポリイミド膜14に設けられた開口16を介してAuメッキ層18により、ドレイン配線5の他端とドレイン電極パッド12が接続されている。ドレイン配線5の他端はポリイミド膜14から出ていない。

(もっと読む)

配線膜およびそれを用いたアクティブマトリクス基板、並びに配線膜の製造方法

【課題】テーパー形状のAl配線膜を容易かつ安定的に得る。

【解決手段】Al配線膜101は、AlもしくはAl合金から成る第1のAl合金層101aと、その上に配設され、Ni、PdおよびPtのいずれか1以上の元素を含み第1のAl合金層101aとは異なる組成のAl合金から成る第2のAl合金層101bとから成る二層構造を有する。フォトレジスト102の現像処理に用いるアルカリ性薬液により、第2のAl合金層101bはエッチングされ、その端部はフォトレジスト102の端部よりも後退する。その後、フォトレジスト102をマスクとするウェットエッチングを行うことにより、Al配線膜101の断面はテーパー形状となる。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、製造コストを低減し、さらにゲート電極およびゲートコンタクトの抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、ゲート電極7の少なくとも上層は、第2金属シリサイド膜としてのWSix膜72からなり、第1金属シリサイド膜としてのNiSi2膜18に含まれる第1金属(Ni)とシリコンとの結合エネルギーが、WSix膜72に含まれる第2金属(W)とのシリコンとの結合エネルギーよりも小さく、WSix膜72の組成MSix(Mは第2金属を示す)において、xが1.5以上2.0未満であることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】所定値以上の厚みを有するパッドを少ない工程数で形成することができる半導体装置の製造方法を提供すること。

【解決手段】本発明は、アルミ層22を、半導体基板上に形成された層間絶縁膜1の上方に堆積させる。アルミ層22上には、アルミ層24を堆積させる。パッド領域102のアルミ層24の上方に、フォトレジスト7を形成する。フォトレジスト7を用いてエッチングを行うことにより、パッド領域102にパッド上層52を形成するとともに、配線領域101のアルミ層24を除去する。そして、フォトレジスト8を、パッド領域102のパッド上層52を覆い、かつ、配線領域101で配線パターンを構成するように形成する。フォトレジスト8を用いてエッチングを行うことにより、パッド領域102にパッド下層51を形成するとともに、配線領域101に配線2を形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの制御性を向上した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、構造体と、複数の半導体層と、メモリ膜と、接続部材と、導電部材と、を備える。前記構造体は、メモリ領域と非メモリ領域とを有する基板の前記メモリ領域の上に設けられる。前記構造体は、前記基板の主面に対して垂直な第1軸に沿って積層され複数の電極膜を含む。前記半導体層は、前記構造体を前記第1軸に沿って貫通する。前記メモリ膜は、前記複数の電極膜と前記半導体層との間に設けられる。前記接続部材は、前記基板と前記半導体層との間に設けられる。前記接続部材は、隣り合う2つの前記半導体層のそれぞれの端部と接続される。前記導電部材は、前記基板と前記接続部材との間で、前記メモリ領域から前記非メモリ領域に延在して設けられる。前記導電部材は、前記非メモリ領域の上に設けられた凹部を有する。前記凹部内には、第1シリサイド部が設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

表側および裏側の電気インターコネクトを含む集積回路

【課題】シリコン・オン・インシュレータ(SOI)基板の層内に配置された複数のトランジスタ、および層の第1の側の上に配置されたベース酸化物層を含むSOI基板を備えた集積回路を提供すること。

【解決手段】集積回路はまた、層の第1の側に形成された第1のインターコネクトを含むことができ、第1のインターコネクトが、複数のトランジスタのうちの第1のトランジスタと複数のトランジスタのうちの第2のトランジスタとを電気的に接続することができる。加えて、集積回路は、層の第1の側とは反対の層の第2の側に形成された第2のインターコネクトを含み、第2のインターコネクトが、複数のトランジスタのうちの第3のトランジスタと複数のトランジスタのうちの第4のトランジスタとを電気的に接続する。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

81 - 100 / 3,144

[ Back to top ]