Fターム[5F033QQ08]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングの対象 (10,331) | 導電膜 (3,144)

Fターム[5F033QQ08]に分類される特許

21 - 40 / 3,144

半導体回路装置およびその製造方法

【課題】ビアヒューズ素子の径を小さくし、ビアヒューズ素子を低電流で溶断することが可能な半導体回路装置およびその製造方法を提供する。

【解決手段】一方向に配置された複数の配線層と、前記複数の配線層のうちの少なくとも2つの前記配線層の間に設けられたビアヒューズ素子と、前記複数の配線層の配置方向に直交する平面内において前記ビアヒューズ素子に隣接する穴と、前記穴内に設けられた貫通ビアとを備えた半導体回路装置。

(もっと読む)

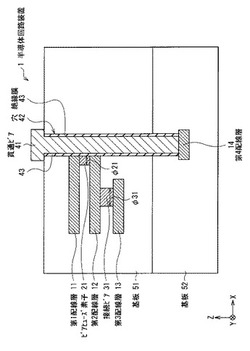

半導体装置およびその製造方法、電子部品

【課題】貫通電極におけるボイドの発生を防止することができ、従来に比べて信頼性の高い半導体装置およびその製造方法、ならびに電子部品を提供すること。

【解決手段】Si基板29上のゲート絶縁膜30上に電極層51を形成する。ゲート絶縁膜30上に層間絶縁膜31を形成した後、ダマシン法により電極層51と同一パターンの下側配線42と、反対パターンの下側絶縁膜43を含む下側パッド40を形成する。次に、貫通孔59を形成し、同時に、貫通孔59内に下側絶縁膜43と同一パターンの突出部60が形成された第1層間絶縁膜32を露出させる。そして、突出部60の一部がエッチング残渣として残るように第1層間絶縁膜32をエッチングした後、ビア絶縁膜38を形成し、貫通孔59の底面のビア絶縁膜38をエッチングする。次に、貫通孔59のビア絶縁膜38の内側に電極材料をめっき成長させることにより、貫通電極17を形成する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

ビットライン接触面積確保のための半導体素子、その半導体素子を有するモジュール及びシステム

【課題】埋め込みゲートを有する半導体素子に関し、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【解決手段】ビットラインコンタクト136が活性領域120の上部面だけではなく側面とも接触されることにより、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

(もっと読む)

半導体装置の製造方法

【課題】電界効果トランジスタを有する半導体装置のトランジスタ性能を向上させることのできる技術を提供する。

【解決手段】ゲート絶縁膜5およびゲート電極6n,6pの側面にサイドウォール9を形成した後、サイドウォール9の両側の半導体基板1に不純物をイオン注入して不純物領域を形成する。続いて、半導体基板1の主面上に第1絶縁膜14、第2絶縁膜15、および第3絶縁膜16を順次形成した後、イオン注入された上記不純物を活性化する熱処理を行う。ここで、第1絶縁膜14は、第2絶縁膜15よりも被覆性のよい膜であり、かつ、第2絶縁膜15とエッチング選択比が異なる膜である。第2絶縁膜15は、第1絶縁膜14よりも水素の拡散を阻止する機能が高い膜である。第3絶縁膜16は、第1絶縁膜14および第2絶縁膜15よりも内部応力の変化が大きい膜である。

(もっと読む)

半導体装置の製造方法および半導体装置

【目的】配線間のコンタクト配置において配線間距離をより小さく形成する。

【構成】実施形態の半導体装置は、第1と第2の配線と、第1の絶縁膜と、第2の絶縁膜と、第1のコンタクトと、第2のコンタクトと、を備えている。第1と第2の配線は、基板上に互いに並行するように形成される。第1の絶縁膜は、第1と第2の配線を覆うように形成される。第2の絶縁膜は、第1と第2の制御ゲート線間の所定位置で第1と第2の配線と並行して延びるように形成され、第1の絶縁膜と材料が異なる。第1のコンタクトは、第1と第2の配線間で、前記第2の絶縁膜に対して前記第1の配線側に位置する前記第1の絶縁膜を通して形成される。第2のコンタクトは、前記第1と第2の配線間で、前記第1と第2の配線が延びる方向に沿って前記第1のコンタクトと互いに位置をずらしつつ、前記第2の絶縁膜に対して前記第2の配線側に位置する前記第1の絶縁膜を通して形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

磁気抵抗素子構造の製造方法

【課題】本発明は、磁気抵抗材料と集積回路とを巧みに統合することのできる、磁気抵抗素子構造の製造方法を提供する。

【解決手段】基板を提供する工程と、上記基板の上に金属ダマシン構造を形成する工程と、該金属ダマシン構造に電気的に接続するように該金属ダマシン構造の上にパターン化磁気抵抗ユニットを形成する工程とを含む、磁気抵抗素子構造の製造方法である。

(もっと読む)

型押し構造体の製造方法、薄膜トランジスター、薄膜キャパシター、アクチュエーター、圧電式インクジェットヘッド及び光学デバイス

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより金属酸化物又は金属となる液体材料を準備する第1工程と、基材上に液体材料を塗布することにより金属酸化物又は金属の前駆体組成物からなる前駆体組成物層を形成する第2工程と、前駆体組成物層に対して凹凸型を用いて型押し加工を施すことにより前駆体組成物層に残膜を含む型押し構造を形成する第3工程と、型押し構造が形成された前駆体組成物層に対して大気圧プラズマ又は減圧プラズマによるアッシング処理を施すことにより残膜を処理する第4工程と、前駆体組成物層を熱処理することにより、前駆体組成物層から金属酸化物又は金属からなる型押し構造体を形成する第5工程とをこの順序で含む型押し構造体の製造方法。

(もっと読む)

配線構造及びそれを備える薄膜トランジスタアレイ基板並びに表示装置

【課題】透明導電膜上における絶縁膜の膜浮きの発生を抑え、且つ、透明導電膜と金属膜との良好な電気的接続性を得ることができる配線構造を提供する。

【解決手段】それぞれ配線として機能する第1の導電膜2と第2の導電膜5と接続する配線変換部45において、第2の導電膜5の内側には刳り抜き部13が形成される。第2の導電膜5の上に設けられる第2の導電膜5は、第2の導電膜5の上面および刳り抜き部13に露出した端面を覆い、且つ、第2の導電膜5の外周の端面を覆わないように形成される。第1の透明導電膜6の上層の第2の透明導電膜7が、第2の導電膜5と第1の導電膜2とに接続することにより、第1の導電膜2と第2の導電膜5とが電気的に接続される。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトプラグに接続される配線間隔の縮小を可能にする半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板に第1の領域と第2の領域とを定義し、第1の領域に第1のサイズを持つ第1の素子を形成し、第2の領域に、第1のサイズとは異なる第2のサイズを持つ第2の素子を形成し、第1の素子及び第2の素子を覆うように半導体基板上に第1の層間絶縁膜を形成し、第1の領域上の第1の層間絶縁膜を貫通し第1の素子の一部を露出させる第1のコンタクトホールを形成し、第2の領域上の第1の層間絶縁膜を貫通し第2の素子の一部を露出させる第2のコンタクトホールを形成し、第1のコンタクトホール及び第2のコンタクトホールをそれぞれ埋める第1のコンタクトプラグ及び第2のコンタクトプラグを同時に形成する。

(もっと読む)

半導体装置の製造方法、半導体装置及び電子機器

【課題】半導体装置に含まれる貫通孔を微細化した場合であっても、メッキで貫通孔の内部に貫通電極を形成する。

【解決手段】半導体装置100の製造方法は、基板10の表面10a側にシード層30を形成するシード層形成工程と、シード層形成工程後、シード層30上に配線層40を形成する配線層形成工程と、配線層形成工程後、基板10の裏面10bからシード層30に達する貫通孔10cを形成する貫通孔形成工程と、貫通孔形成工程後、貫通孔10c内にメッキで貫通電極60を形成する貫通電極形成工程と、貫通電極形成工程後、シード層30を複数に分断する分断工程とを含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、ビットコンタクト用の溝部12を挟んで対向する一対の埋め込みゲート用の溝部8a,8bの底部に不純物が拡散された領域13a,13bと、ビットコンタクト用の溝部12に不純物が拡散された領域13cと、が結合されて設けられた第1の不純物拡散層13と、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通ビアを用いた実装における端子間のショートや実装精度の低下を防止する。

【解決手段】半導体チップ88の貫通ビア86の上に、他の半導体チップ101を実装する。半導体チップ101のバンプ103は、4つの貫通ビア86で囲まれた領域に導かれて接合される。各貫通ビア86は、バンプ103に面する側面及び上面の保護膜31がエッチングによって除去されており、バンプ103のハンダ材料への濡れ性が保護膜31で覆われた領域よりも良好になっている。このために、ハンダ材料のはみ出しによる他の電極との間のショートが防止される。さらに、1つのバンプ103に複数の貫通ビア86からなる接続端子を配置するので、バンプ103に確実に接合できる。

(もっと読む)

基板貫通バイアを有する半導体構造および製造方法

【課題】基板を貫通するバイアホールを与える。

【解決手段】半導体デバイス構造は、第1の濃度および第1の導電型のバックグラウンドドーピングを有する基板を含んでなる。基板貫通バイアは基板を貫通している。デバイスは基板の第1の面上に第2の導電型の第1のドープ領域を有する。第2のドープ領域が基板貫通バイアの周りにある。第2のドープ領域は、第1の濃度よりも大きい第2の濃度にドーピングされており、第1の導電型を有する。

(もっと読む)

半導体装置の製造方法

【課題】エピ抵抗や抵抗チップを用いることなく、奇モードのループ発振を抑えること。

【解決手段】本発明は、金属層60を形成する工程と、複数のFETそれぞれのゲートフィンガー14を共通に接続するゲートバスライン26のパターンのうち一部分を除いたパターンを有するめっき層64と、一部分の領域を被覆する第2マスク層66と、をマスクにして金属層60をパターニングすることで、ゲートバスライン26を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

銅層および/または銅合金層を含む金属膜用エッチング液組成物およびそれを用いたエッチング方法

【課題】 本発明の課題は、銅層および/または銅合金層を有する金属膜や、該層と他の金属からなる層との積層膜を精度良くエッチングでき、液寿命が長いエッチング液組成物を提供することにある。

【解決手段】 本発明は、銅層および/または銅合金層を含む金属膜をエッチングするためのエッチング液組成物であって、銅(II)イオン、β−アラニンおよび水を含む、前記エッチング液組成物、ならびに、該エッチング液組成物を用いたエッチング方法に関する。

(もっと読む)

21 - 40 / 3,144

[ Back to top ]