Fターム[5F033QQ16]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | 異方性エッチング (964)

Fターム[5F033QQ16]の下位に属するFターム

斜めエッチング (8)

Fターム[5F033QQ16]に分類される特許

81 - 100 / 956

パターンの形成方法

【課題】LELEプロセスよりも少ない工程数で、フォトリソグラフィ技術を2度使用することなく、微細なホール又はトレンチパターンを形成する方法を提供すること。

【解決手段】被処理体の上にレジスト膜を成膜し、成膜した前記レジスト膜をパターニングする、レジスト膜形成工程と、前記被処理体及び前記レジスト膜を被覆するようにスペーサ膜を成膜して、前記スペーサ膜で囲まれた凹部を形成する、スペーサ膜成膜工程と、前記凹部の底面にある前記被処理体及び前記レジスト膜の上面を露出させると共に、前記レジスト膜の側面側に前記スペーサ膜が残るようにエッチングして、前記凹部から第1の開口部を形成する、第1開口部形成工程と、前記レジスト膜を除去することにより第2の開口部を形成する、第2開口部形成工程と、を含むパターンの形成方法。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コストが低い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、絶縁膜及び電極膜が交互に積層された積層体を形成する工程と、前記積層体上に、サイズが相互に異なる複数のホールが形成されたハードマスクを形成する工程と、マスク材料を堆積させることにより、最も小さい前記ホールを閉塞させると共に、その他の前記ホールを小さくする工程と、前記マスク材料及び前記ハードマスクをマスクとしてエッチングを施すことにより、前記その他のホールの直下域において、各所定枚数の前記絶縁膜及び前記電極膜を除去して、コンタクトホールを形成する工程と、前記コンタクトホールを介してエッチングを施すことにより、前記電極膜の一部分を除去して隙間を形成する工程と、前記隙間内に絶縁材料を埋め込む工程と、前記コンタクトホール内に導電材料を埋め込む工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】ヒートシンクに生じる不具合を低減すること。

【解決手段】半導体装置は、第1面及び第2面を有し、第1面と第2面とを貫通するバイアホールを有する半導体基板と、第1面上に、バイアホールの開口と少なくとも部分的に重複するように形成された配線又は電極と、第2面上に形成され、バイアホールの開口と少なくとも部分的に重複する開口を有する応力緩衝層と、応力緩衝層上からバイアホールの内壁面に沿って延在し、配線又は電極と電気的に接続されたヒートシンクと、を備える。バイアホールの第2面における開口の大きさは、第1面における開口の大きさよりも大きい。応力緩衝層の熱膨張係数は、ヒートシンクの熱膨張係数未満である。

(もっと読む)

半導体装置の製造方法、及び固体撮像装置の製造方法

【課題】 精度よく開口を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】 第1の絶縁膜となる部材と、第1の絶縁膜となる部材と異なる材料からなる第2の絶縁膜となる部材と、第3の絶縁膜となる部材と、第3の絶縁膜となる部材と異なる材料の第4の絶縁膜となる部材とがこの順に積層された半導体基板の上に、複数の絶縁膜の開口を形成するための開口を有するマスクを形成する工程と、第3の絶縁膜となる部材のマスクの開口に対応する部分と第4の絶縁膜となる部材のマスクの開口に対応する部分を連続して除去する第1の工程と、第1の工程を行った後に、第2の絶縁膜となる部材のマスクの開口と対応する部分を除去する第2の工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能と信頼性を向上させる。

【解決手段】nチャネル型MISFETQn1,Qn2を覆うように半導体基板1上に引張応力膜としての窒化シリコン膜5を形成する。窒化シリコン膜5は窒化シリコン膜5a,5b,5cの積層膜である。窒化シリコン膜5a,5bの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分よりも小さく、窒化シリコン膜5a,5bは、成膜後に紫外線照射処理を行って引張応力を増大させる。窒化シリコン膜5a,5b,5cの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分以上であり、窒化シリコン膜5cに対しては紫外線照射処理を行わない。

(もっと読む)

半導体装置及びその製造方法、並びにSOI基板及びその製造方法

【課題】コンタクトホールの形成領域が素子分離領域と重複しても、素子特性の劣化を抑制できるSOI基板とこのSOI基板を用いた半導体装置とを提供する。

【解決手段】半導体装置1は、半導体基材11と埋め込み絶縁膜12と半導体層16とを有するSOI基板と、このSOI基板上に形成された半導体素子構造とを備える。埋め込み絶縁膜12は、半導体基材11から半導体層16を電気的に絶縁分離する機能を有し、窒化膜14を有する。

(もっと読む)

半導体装置の製造方法

【課題】デュアルダマシン法による銅配線接続において、コンタクト抵抗の上昇を抑制する半導体装置の製造方法を提供する。

【解決手段】第1の配線25上に積層された第1の拡散防止膜27及び層間絶縁膜のうち、第1の層間絶縁膜28をエッチングすることで第1のホールを形成する。第1の拡散防止膜がエッチングされにくい条件で、第1のホールの下方に位置する第1の層間絶縁膜をエッチングして第2のホールを形成する。第2のホールを埋め込むように、第1の層間絶縁膜よりもエッチング速度の速い第2の層間絶縁膜を形成する。第1の層間絶縁膜の上面が露出するまで第2の層間絶縁膜をエッチングすることで、第2のホールと一体とされた配線形成用溝を形成する。第2のホール内に残存する第2の層間絶縁膜を選択的に除去し、第2のホールの下方に位置する第1の拡散防止膜を選択的に除去する。

(もっと読む)

半導体装置の製造方法及びハードマスクの形成方法

【課題】アモルファスカーボン膜のパターン寸法ばらつきが低減した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に下地膜を形成する工程と、下地膜上にアモルファスカーボン膜を成膜する工程と、アモルファスカーボン膜のパターンを形成する工程と、アモルファスカーボン膜をマスクにして下地膜をエッチングする工程を有する。アモルファスカーボン膜は、アモルファスカーボン膜の表面から下地膜に接する面に向かってその厚み方向を進むにつれて、アモルファスカーボン膜の膜密度を小さくする。

(もっと読む)

半導体装置の作製方法

【課題】コンタクトホールを微細化する。この時、微細化されたコンタクトホールであっても、半導体装置における電極のコンタクトを確実なものとする。

【解決手段】珪化膜と樹脂材料膜とからなる多層の層間絶縁膜を形成する。その後、コンタクトホールを形成する。このとき、珪化膜に設けられるコンタクトホールの大きさを樹脂材料膜に設けられるコンタクトホールの大きさよりも小さくする。このような構成は、パターンが複雑化してもコンタクトのとりやすいものとすることができる。

(もっと読む)

半導体装置の製造方法

【課題】携帯電話などのフロントエンドモジュールに使用されているハイパワーアンプは、シリコン系CMOS集積回路をベースとするデバイスであるが、その出力段に多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成したLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。このポリシリコンプラグは、熱処理に起因する固相エピタキシャル成長により収縮し、シリコン基板に歪が発生する。

【解決手段】本願発明は、LDMOSFET等の半導体装置の製造方法において、基板の表面からエピタキシャル層を貫通するホールを形成し、ポリシリコンプラグを埋め込むに際して、ホールの内面に薄膜酸化シリコン膜が存在する状態で、ポリシリコン部材の堆積を行うものである。

(もっと読む)

半導体装置の製造方法

【課題】制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

(もっと読む)

組成物

【課題】低い誘電率及び改良された機械的性質、熱的安定性及び化学的耐性を有する多孔質有機シリカガラス膜を提供する。

【解決手段】式SivOwCxHyFz(ここで、v+w+x+y+z=100%、vは10〜35原子%、wは10〜65原子%、xは5〜30原子%、yは10〜50原子%、及びzは0〜15原子%)で表わされる多孔質有機シリカガラス膜を製造する。オルガノシラン及びオルガノシロキサンからなる群より選ばれる前駆体並びにポロゲンを含むガス状試薬を真空チャンバに導入し、ガス状試薬にエネルギーを加え、ガス状試薬の反応を生じさせて基体上に予備的な膜を堆積させる。その予備的な膜は細孔を持ち、誘電率が2.6未満である多孔質膜を得るために、実質的にすべてのポロゲンを除去される。

(もっと読む)

異方性エッチング方法、三次元構造体、及び、デバイス

【課題】被対象物を効率よく所望する形状となるようにエッチングすることが可能な異方性エッチング方法、該異方性エッチング方法を用いて形成可能な三次元構造体、及び、該三次元構造体を備えたデバイスを得る。

【解決手段】異方性エッチング方法は、表面に所定形状のマスクを有した基板に対して、SF6とC4F8とを含む混合ガス、又は、SF6とC4F8とO2とを含む混合ガスを用いた反応性イオンエッチングによって、所定条件下で結晶異方性エッチングを行う結晶異方性エッチング工程を有している。本方法と、Bosch法による垂直異方性エッチングを行う垂直異方性エッチング工程とを用いて三次元構造体を製造し、該三次元構造体をデバイスに利用する。

(もっと読む)

埋め込みビットラインを備えた半導体装置の製造方法

【課題】埋め込みビットラインの抵抗を減少させることができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板201に活性領域203を分離するトレンチ202をエッチングにより形成するステップと、活性領域203の何れか1つの側壁の一部を露出させた開口部207を有する絶縁膜205を形成するステップと、絶縁膜205上にトレンチ202を部分的に埋め込み、開口部207を埋め込むようにシリコン膜パターン208Aを形成するステップと、シリコン膜パターン208A上に金属膜209を形成するステップと、金属膜209及びシリコン膜パターン208Aを反応させて、埋め込みビットラインとなる金属シリサイド膜211を形成するステップとを含む。

(もっと読む)

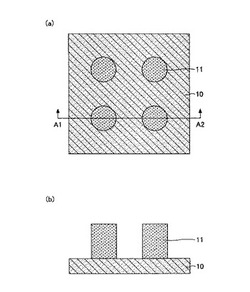

半導体装置及び半導体装置の製造方法

【課題】スルーホールの微細化による半導体装置の高集積化と、スルーホール内に埋め込まれる導体のカバレッジ性と、を両立させる。

【解決手段】半導体装置は、下層配線2と、下層配線2上に形成され、下層配線2の上面を露出させる開口31を有する第1絶縁膜(例えば、有機絶縁膜3)と、第1絶縁膜上に形成され、スルーホール5が形成された第2絶縁膜(例えば、無機絶縁膜4)とを有する。半導体装置は、更に、スルーホール5に埋め込まれ、下層配線2と電気的に接続された導体9を有する。開口31は、上側に向けて拡径するテーパー形状に形成されている。スルーホール5の側壁5aの少なくとも下端は、開口31の側壁31aを構成する傾斜面の上に位置している。

(もっと読む)

側壁イメージ転写からパターンを作る改善された方法

【課題】実施の容易な、側壁イメージ転写により部分的に定義されるパターンを生成する方法を提供する。

【解決手段】基板1には、第1の材料2の層と、第1のエッチングマスク4と、カバリング層3と、第2のエッチングマスクとが設けられている。カバリング層3は、覆われた主領域と、覆われていない副領域とを有する。カバリング層3の副領域は、第2のエッチングマスクを介して部分的にエッチングされ、突出パターンが形成される。第3のエッチングマスクを定義する突出パターンの周囲に、横スペーサが形成される。第2のエッチングマスクは除去される。カバリング層3は、第3のエッチングマスクを用いてエッチングされ、カバリング層3における突出パターンが形成され、第1のエッチングマスク4および第1の材料2が露出される。第1の材料2の層は、エッチングされ、第1の材料2から作られるパターンが形成される。

(もっと読む)

半導体装置の作製方法

【課題】コンタクトホールを微細化する。この時、微細化されたコンタクトホールであっ

ても、半導体装置における電極のコンタクトを確実なものとする。

【解決手段】珪化膜と樹脂材料膜とからなる多層の層間絶縁膜を形成する。その後、コン

タクトホールを形成する。このとき、珪化膜に設けられるコンタクトホールの大きさを樹

脂材料膜に設けられるコンタクトホールの大きさよりも小さくする。このような構成は、

パターンが複雑化してもコンタクトのとりやすいものとすることができる。

(もっと読む)

半導体装置

【課題】3次元的に積層された複数の半導体チップを有する半導体装置の製造歩留まりを向上できる技術を提供する。

【解決手段】半導体基板1の第2面1bからパッド3に達する貫通電極17が形成されている。貫通電極17の内部にある貫通空間は、第1孔7および第1孔7よりも孔径の小さい第2孔11によって構成されている。半導体基板1の第2面1bから半導体基板1を貫通して層間絶縁膜2の途中まで第1孔7が形成されている。そして、第1孔7の底部から層間絶縁膜2を貫通してパッド3に達する第2孔11が形成されている。このとき、半導体基板1の第1面1aに形成されている層間絶縁膜2は、第1孔7の底面と半導体基板1の第1面1aとの段差を反映して段差形状になっている。すなわち、第1孔7の底面とパッド3間に存在する層間絶縁膜2の膜厚がその他の場所の層間絶縁膜2の膜厚よりも薄くなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、アルミ配線パターンに含まれるアルミニウムと銅配線に含まれる銅とが反応して高抵抗の合金が生成されることを防止した上で、導電膜である窒化チタン膜に起因する半導体基板の反りを低減することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】第2の層間絶縁膜18に形成されたコンタクト孔27により露出された銅配線16の上面16aを覆うように、窒化チタン膜を含む第1の導電膜21を設けると共に、アルミ配線パターン23と第1の導電膜21及び第2の層間絶縁膜18との間に、窒化チタン膜を含まない第2の導電膜22を設ける。

(もっと読む)

81 - 100 / 956

[ Back to top ]