Fターム[5F033QQ16]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | 異方性エッチング (964)

Fターム[5F033QQ16]の下位に属するFターム

斜めエッチング (8)

Fターム[5F033QQ16]に分類される特許

41 - 60 / 956

電子デバイス及びその製造方法

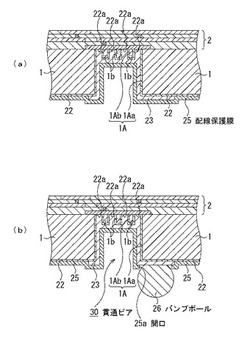

【課題】貫通電極の基板等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通電極の側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い電子デバイスを提供する。

【解決手段】基板1と、基板1の表面上方に形成された配線18と、基板1の裏面から基板1を貫通しており、基板1の深さ方向において、第1の開孔1Aaと、第1の開孔1Aaよりも開口総面積が小さい第2の開孔1Abとが接続された貫通孔1Aに形成されてなる貫通ビア30とを含み、貫通ビア30は、第1の開孔1Aaに形成された第1の電極部30aと、第2の開孔1Abに形成された第2の電極部30bとが、最外側面が一体形成される。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】携帯電話などに使用されるハイパワーアンプの出力段は、多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成するLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。本願発明者らが、このポリシリコンプラグについて、検討したところによって、熱処理に起因してポリシリコンプラグの固相エピタキシャル成長により、ポリシリコンプラグが収縮し、それによってシリコン基板に歪が発生し、リーク不良等の原因となることが明らかとなった。

【解決手段】本願発明は、LDMOSFETを有する半導体集積回路装置において、半導体基板に埋め込まれたシリコン系導電プラグのボロン濃度が、固溶限界内に於いて、8.1x1020atom/cm3以上である。

(もっと読む)

パワーデバイス

【課題】膜剥がれの要因となる有機材料を用いることなく、エレクトロマイグレーションの耐性と長期信頼性を向上できるパワーデバイスを提供する。

【解決手段】バリア層4(AlGaN)4上に形成された酸化シリコン(SiO2)からなる層間絶縁膜10と、層間絶縁膜10のソース電極5上に形成され、基板平面に対して略垂直な第1の側壁W1を有する第1コンタクトホール部10aと、第1コンタクトホール部10aの第1の側壁W1の上縁から上側に向かって徐々に広がるように層間絶縁膜10に形成され、基板平面に対して傾斜した第2の側壁W2を有する第2コンタクトホール部10bと、第1,第2コンタクトホール部10a,10b内および層間絶縁膜10上に形成された配線層12とを備える。上記配線層12は、第1コンタクトホール部10aにおいて第1の側壁W1の基板厚さ方向の寸法よりも膜厚が厚い。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極とポリシリコン抵抗素子とを同じ半導体基板に混載するとともに、半導体装置の設計の自由度を向上し、また、半導体装置の小型化を図る。

【解決手段】半導体基板1の主面上にゲート絶縁膜を介してMISFET用のメタルゲート電極が形成され、また、半導体基板1の主面上に積層パターンLPを介してポリシリコン抵抗素子用のシリコン膜パターンSPが形成されている。メタルゲート電極は金属膜とその上のシリコン膜とを有し、積層パターンLPは絶縁膜3aとその上の金属膜4aとその上の絶縁膜5aとを有し、絶縁膜3aは、前記ゲート絶縁膜と同層の絶縁膜により形成され、金属膜4aはメタルゲート電極の金属膜と同層の金属膜により形成され、シリコン膜パターンSPは、メタルゲート電極のシリコン膜と同層のシリコン膜により形成されている。シリコン膜パターンSPは、平面視で絶縁膜5aに内包されている。

(もっと読む)

半導体チップ、半導体チップの製造方法、および半導体装置

【課題】特性が良好であり、信頼性の高い半導体チップ、半導体チップの製造方法、および半導体装置を提供する。

【解決手段】実施形態の半導体チップは、第1主面と第2主面とを有し、第1主面側に、素子および配線が配置された回路部と回路部を取り囲むガードリング機構部とが設けられた半導体基板と、第1主面側から第2主面側まで通じるビアホール内に設けられたビアと、第1主面側から第2主面側まで通じる第1トレンチ内に設けられた絶縁層と、を備える。第1主面に対して垂直な方向からみて、ビアホールは、回路部が設けられた回路領域に配置されている。第1トレンチは、回路部を取り囲みガードリング機構部が設けられた外周領域に配置されている。第1主面に対して平行な方向における第1トレンチの幅は、この平行な方向におけるビアホールの幅よりも狭い。

(もっと読む)

シリコンに対する誘電材料の選択エッチング方法及びシステム

【課題】 本発明はドライプラズマエッチングを用いた基板のエッチング方法に関する。

【解決手段】 ドライプラズマエッチングシステム内で誘電体層をシリコン及びポリシリコンに対して選択的な均一エッチングを行う方法及びシステムが記載されている。エッチング用化学は、たとえばCH2F2やCHF3のようなフルオロハイドロカーボンを有する。高いエッチング選択性及び受容可能な均一性は、CH2F2の流速やドライプラズマエッチングシステムと結合する出力を含むプロセス条件を選択することによって実現されて良い。それにより、エッチングプラズマ中での活性エッチングラジカルとポリマー生成ラジカルとの適切なバランスがとられる。

(もっと読む)

半導体装置及びその製造方法

【課題】基板貫通電極の周囲に形成される絶縁分離部において、埋め込まれる絶縁膜が接合面を有していると、基板裏面の研削後の絶縁分離部は、接合面が基板主面から基板裏面に達することで、機械的強度が低下しやすく、貫通電極に応力を印加した場合に絶縁分離部の内側領域が孤立しやすい。

【解決手段】絶縁分離部5に埋め込まれる絶縁膜を第1の絶縁膜3と第2の絶縁膜4の少なくとも2段の積層構造とすることで、第1の絶縁膜3の接合面3Sと第2の絶縁膜4の接合面4Sとが第2の絶縁膜4の底面の接合面のない領域で分断され、機械的強度が増加し、絶縁分離部の内側領域の孤立を阻止することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】メモリ・ロジック混載型の半導体装置の高性能化を可能にする技術を提供する。

【解決手段】ストッパ膜17は、ストッパ膜13及び層間絶縁膜14から成る絶縁層上に形成されている。コンタクトプラグ16,65,66のそれぞれは、その上面がストッパ膜17から露出するように、ソース・ドレイン領域9,59とそれぞれ電気的に接続されてストッパ膜13、層間絶縁膜14及びストッパ膜17に設けられている。絶縁層20は、ストッパ膜17及びコンタクトプラグ16,65,66の上に設けられている。キャパシタ82の下部電極は、メモリ形成領域において、コンタクトプラグ66の上面とストッパ膜17の上面とに接触するように絶縁層20内に設けられている。

(もっと読む)

半導体装置の製造方法

【課題】LTHC膜に由来する基板の汚染を低減する。

【解決手段】基板の第1の主面を光熱変換膜を介して支持基板に張付ける工程と、支持基板上に露出した光熱変換膜を除去する工程と、を有することを特徴とする半導体装置の製造方法。支持基板上に光熱変換膜を形成する工程と、半導体基板より外側に光熱変換膜が延在するように半導体基板を前記支持基板に張付ける工程と、光熱変換膜に汚染防止処理を行う工程と、支持基板と半導体基板とを分離させる工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】 シリコン基板を貫通するビアホールの形成時におけるノッチの発生を抑制することができ、製造歩留まり及び信頼性の向上をはかる。

【解決手段】 シリコン基板貫通電極を有する半導体装置の製造方法であって、表面側に機能素子と配線層15が形成され、且つ配線層15の下層にエッチング停止層12を有するシリコン基板10の表面側に支持基板30を取着した後、基板10の裏面側を研削して厚みを減少させる。次いで、基板10の裏面側に、ビアホール用開口及び該開口よりも小径のダミーホール用開口を有するマスクを形成した後、基板10の裏面側からエッチングすることにより、配線層15の一部に達するビアホール42を形成すると共に、基板10の途中までダミーホール43を形成する。次いで、ビアホール42の側面に絶縁膜44を形成した後、ビアホール42内に配線材料を形成する。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】CMP法により、金属膜を研磨して、層間絶縁膜に設けられた開口部内に導体パターンを形成する際、リセス、ディッシング、及びエロージョンを抑制可能な半導体装置の製造方法を提供する。

【解決手段】CMP法により、層間絶縁膜14の上面よりも上方に形成された金属膜19及びバリア膜18を除去することで、開口部内に、バリア膜18及び金属膜19よりなる導体パターンを形成する研磨工程と、を有し、該研磨工程では、層間絶縁膜14の上面が露出する前に、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件を用いて研磨を行なうことで、導体パターンを形成する。

(もっと読む)

半導体装置の製造方法

【課題】反射防止膜を確実に除去して半導体装置の欠陥発生を低減する。

【解決手段】第1の層間絶縁膜の上に、絶縁膜と、反射防止膜と、レジスト膜とを順番に形成する。レジスト膜を用いて反射防止膜と絶縁膜をエッチングし、絶縁膜からハードマスクを作成する。この後、ラジカル照射によってレジスト膜と反射防止膜を除去する。ラジカル照射は、基板温度を100℃、150℃、250℃と順番に上昇させながら行う。基板温度が低い初期段階では、反射防止膜の膜材料の飛散防止と、反射防止膜の表面に残留する他の物質の除去が行われる。この後、基板温度を高くすることで、反射防止膜が確実に除去される。

(もっと読む)

電子デバイス、及び、その製造方法

【課題】素子に不具合が生じることが抑制された電子デバイス、及び、その製造方法を提供する。

【解決手段】接合された2つの基板(10,50)に素子(20,60)と貫通電極(30)とが形成されて成る電子デバイスであって、素子(20,60)は、2つの基板(10,50)の少なくとも一方に形成され、貫通電極(30)は、2つの基板(10,50)の少なくとも一方に形成されており、貫通電極(30)は、一方の基板(10)における他方の基板(50)との接合面(10a)側から、その裏面(10b)まで除去されて成るトレンチ(31)と、該トレンチ(31)を構成する壁面の一部に形成された導電膜(35)と、を有する。

(もっと読む)

パターン形成方法

【課題】微細なパターンと比較的サイズが大きめのパターンとを有するパターン形成方法で、サイズが大きめのパターンを従来に比して精度良く形成することができるパターン形成方法を提供する。

【解決手段】実施形態によれば、加工対象上の芯材膜31に開口を形成した後、マスク膜32をコンフォーマルに形成する。マスク膜32をエッチバックして芯材膜31の側面に第1の幅のマスク膜32を残す。開口の形成領域以外の領域にレジストパターン35aを形成し、これをマスクに芯材膜31をエッチングする。さらに、芯材膜31をスリミングして第1の幅より小さい第2の幅のラインアンドスペース状のパターンを形成する。側壁膜をコンフォーマルに形成した後、エッチバックし、さらに芯材膜31を除去して、加工対象上に側壁膜からなる側壁パターンを形成する。そして側壁パターンで加工対象をエッチングする。

(もっと読む)

導電性ビアの製造と充填のための方法、およびそのように形成された導電性ビア

【課題】ビアホール表面上の絶縁コーティングとビアホール内に挿入される導電材料との付着性を向上する。

【解決手段】導電性ビアを形成する方法は、一つ以上のビアホールを基板内に形成するステップを含む。ビアホールは、単一マスク、保護層、ボンドパッド、もしくは、エッチングプロセスの間にフォトマスクが除去される場合にハードマスクとして機能する、基板のその他のフィーチャで形成され得る。ビアホールは、その表面に低誘電率(低K)誘電材料を含む誘電体コーティングの付着を促進するように構成されてもよい。障壁層が各ビアホールの表面の上に形成されてもよい。種材料(seed material)を含み得るベース層は、その後のビアホールの表面上の導電材料の選択的堆積を促進するように形成されてもよい。

(もっと読む)

半導体装置およびその製造方法、並びに表示装置

【課題】3層以上の配線を接続する際に、最も効率的にかつ最小面積で接続を行えるコンタクト構造を実現可能な半導体装置およびその製造方法、並びに表示装置を提供する。

【解決手段】基板201上に3層以上のn層の導電層202〜204が積層して形成され、n層の導電層がコンタクトパターンを介して接続され、コンタクトパターンが形成される一つの主コンタクト領域には、(n−1)個の導電層202,203を接続する(n−1)個の接続領域211,212を有し、(n−1)個の導電層のうち基板201に対する積層方向(基板201の主面に対する法線方向)において第1層より上層の導電層は、その終端部がコンタクトパターンCPTNの縁の一部に臨むように形成され、(n−1)個の導電層は、第n層の導電層により電気的に接続されている。第n層の導電層は、コンタクトパターンCPTNであるコンタクト孔を埋めつくよう形成されている。

(もっと読む)

誘電フィルム及び材料における疎水性を回復する方法

【課題】誘電率の増加、シラノールの増加、または有機部分の減少、の少なくとも一つによって損傷した、基体上のシリカ誘電フィルムの損傷を回復する。

【解決手段】基体上のそのような損傷シリカ誘電フィルムを表面改質組成物と接触させて、該損傷シリカ誘電フィルムの誘電率の減少、該損傷シリカ誘電フィルムの誘電率のシラノールの減少、該損傷シリカ誘電フィルムの誘電率の有機部分の増加、の1つ以上をもたらす。このとき、該損傷シリカ誘電フィルムに疎水性を与える。

(もっと読む)

半導体集積回路のトランジスタ素子

【課題】簡易な構成であり且つトランジスタ毎にしきい値電圧が異なる半導体集積回路のトランジスタ素子の提供。

【解決手段】ソース領域16A,16D、ドレイン領域16B,16Cおよびチャネル領域を備えた支持基板(Si基板2)上に、ゲート電極10とゲート電極10を覆う中間膜18とを備える第1および第2のトランジスタ構造を、少なくとも有し、前記第1のトランジスタ構造におけるゲート電極10とチャネル領域とが重なる領域には、中間膜18上に、第1のトランジスタ構造のしきい値電圧に変動を及ぼす範囲でゲート電極10とチャネル領域とが重なる領域の大部分を覆うよう支持基板(Si基板2)に応力を印加する応力膜22を有し、前記第2のトランジスタ構造におけるゲート電極10とチャネル領域とが重なる領域には、中間膜18上に、支持基板(Si基板2)に応力を印加する応力膜22を有さない半導体集積回路のトランジスタ素子。

(もっと読む)

41 - 60 / 956

[ Back to top ]