Fターム[5F033QQ94]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 清浄化 (1,803) | 除去対象 (877) | 酸化物、酸化膜 (480)

Fターム[5F033QQ94]に分類される特許

121 - 140 / 480

半導体装置の製造方法

【課題】欠陥の発生を防止し且つ電気的特性に優れた強誘電体キャパシタを用いた半導体装置の製造方法を提供する。

【解決手段】第1の導電層40を形成し、第1の導電層40の表面に酸化膜10を形成し、酸化膜10を大気にさらし、酸化膜10を、減圧下且つ第1の温度で減圧加熱処理し、減圧加熱処理された酸化膜10を大気にさらすことなく、減圧下且つ第1の温度よりも低い第2の温度で、非晶質の第1の誘電体層41を酸化膜10上に形成し、第1の温度よりも高い第3の温度で、非晶質の第1の誘電体層41を結晶化する。

(もっと読む)

基板処理方法および基板処理装置

【課題】Cu表面の酸化銅の除去および層間絶縁膜に付着したCu含有物残渣の除去を効率良く確実に行うことができる基板処理方法を提供すること。

【解決手段】基板上のCu配線構造におけるCu表面の酸化銅膜および層間絶縁膜に付着したCu含有物残渣を有機酸含有ガスを用いて除去するにあたり、基板温度が相対的に低温の第1の温度になるように基板を加熱しつつ基板に有機酸ガスを含む処理ガスを供給してCu含有物残渣のエッチング除去を行う第1工程と、基板温度が前記第1の温度よりも高温の第2の温度になるように基板を加熱しつつ基板に有機酸ガスを含む処理ガスを供給して前記Cu表面の酸化銅膜を還元を主体とする反応により除去する第2工程とを行う。

(もっと読む)

プラズマ処理による酸化物又は他の還元可能な汚染物質の基板からの除去

【課題】VLSI技術及びULSI技術において多段相互接続は、アスペクト比の高いバイアや他の相互接続が注意深く処理されることを要する。これらの相互接続の確実な形成技術を提供する。

【解決手段】窒素と水素を含有する化合物、一般にアンモニアを使用し、次層を上へ堆積するに先立ち相対的に低い温度で酸化物又は他の汚染物質を還元する、プラズマ還元プロセスを提供する。酸化物の層の典型的な物理的スパッタ洗浄プロセスと比較して、層の粘着特性が改善され酸素の存在が減少する。このプロセスは、デュアルダマシン構造、とりわけ銅が応用されている場合の複雑な要求に特に有効であろう。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

半導体集積回路装置の製造方法

【課題】ニッケル系メタル・シリサイドとコンタクト用メタル間でのコンタクト抵抗の低抵抗化がホールの微細化に伴って、困難になるという問題がることが、本願発明者の検討により明らかとなった。

【解決手段】本願の一つの発明は、ニッケル系メタル・シリサイドによりソース・ドレイン領域等のシリサイデーションを施したMISFETを有する半導体集積回路装置の製造方法において、プリ・メタル絶縁膜に設けられたコンタクト・ホールにバリア・メタルを形成する前に、シリサイド膜の上面に対して、窒素水素間結合を有するガスを主要なガス成分の一つとして含む非プラズマ還元性気相雰囲気中で、熱処理を実行するものである。

(もっと読む)

半導体装置の製造方法

【目的】従来よりも比抵抗の低いW膜のプラグ或いは配線が得られる半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜に開口部を形成する工程(S106)と、前記開口部の少なくとも底面に、ルテニウム(Ru)膜を形成する工程(S112)と、前記Ru膜が形成された前記開口部内に、水素(H2)還元による化学気相成長(CVD)法によりタングステン(W)膜を埋め込む工程(S114)と、を備えたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】容量素子の酸素雰囲気中での焼結を制限を設けず実施した場合も、スタックコンタクトの信頼性や製造歩留まりを向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1と、その上に形成された第1の層間絶縁膜1,2および第2の層間絶縁膜3,4,5と、第1の層間絶縁膜1,2中に形成された第1のプラグ8bおよび第2のプラグ8aと、第2の層間絶縁膜3,4,5中に形成され第1のプラグ8bと接続された容量素子たるメモリセル30と、第2の層間絶縁膜3,4,5中に形成され第2のプラグ8aと接続された第3のプラグ19とを備え、第2のプラグ8aの中央部の上面は第1の層間絶縁膜1,2の上面よりも半導体基板1側に位置するように構成する。

(もっと読む)

被処理体の成膜方法及び処理システム

【課題】線幅やホール径が小さな凹部や高アスペクト比の凹部に対して十分な埋め込みを行うことが可能な成膜方法を提供する。

【解決手段】凹部6を有する絶縁層4が表面に形成された被処理体Wに対して薄膜を形成する成膜方法において、前記凹部内の表面を含めて前記被処理体の表面にTiを含むバリヤ層12を形成するバリヤ層形成工程と、前記バリヤ層上にRuを含むシード層16を形成するシード層形成工程と、前記シード層上に前記シード層に対する導通性を補助するためにCuを含む補助シード層164を形成する補助シード層形成工程とを有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】配線抵抗の上昇を抑制したまま、EM特性を改善させる半導体装置或いはその製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、絶縁膜に開口部を形成する工程(S106)と、開口部内に、ケイ化物の形成エネルギーがCuケイ化物の形成エネルギーよりも小さい金属含有膜を形成する工程(S108)と、前記金属含有膜が形成された開口部内に銅(Cu)膜を埋め込む工程(S112)と、Cu膜上に、300℃未満の温度でCuとSiとを含有する化合物膜を選択的に形成する工程(S120)と、を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】電極パッドの異常を容易に発見することが可能である。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板の第1領域における第1表面から前記第1表面に対向する第2表面まで空けられた第1貫通孔80内に形成された第1貫通電極25と、前記半導体基板の前記第1表面において、前記第1貫通電極に接して形成された第1電極パッド28と、前記第1電極パッドと離間して形成され、前記第1電極パッドと対向する第2電極パッド29と、前記半導体基板の前記第2表面上に形成され、前記第1貫通電極と電気的に接続された外部端子27と、前記半導体基板の前記第1表面において、前記半導体基板の前記第1領域と異なる第2領域における前記第1表面から前記第2表面まで空けられた第2貫通孔80上に形成され、電気的に浮遊した第3電極パッド28と、を具備する。

(もっと読む)

表示デバイスの製造方法

【課題】Al合金膜の腐食を抑制でき、透明導電膜との接触電気抵抗も低減された表示デバイスを製造する。

【解決手段】下記(1)〜(4)の工程によってAl合金膜を透明導電膜と直接接触させる。(1)Alよりも貴な金属元素を含むAl合金膜を形成する第1の工程、(2)フォトリソグラフィおよびドライエッチングによってコンタクトホールを形成する第2の工程、(3)フォトリソグラフィで生成したフォトレジストの剥離を行なう第3の工程、(4)透明導電膜を形成する第4の工程と、をこの順序で包含し、第2の工程は、オーバーエッチングにおけるガスの流量比を、SF6/(SF6+O2)の比率で30%以下に制御して前記Al合金膜の表面をAlの酸化物で覆う工程を含み、第3の工程は、pH10.5以上のアルカリ溶液に接触させて前記Alの酸化物を除去する工程を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】比誘電率の低い層間絶縁膜を用いた半導体装置において、プラズマ処理時の層間絶縁膜へのダメージを軽減でき、ダメージ層を除去する際に形成されるアンダーカットを抑制する。

【解決手段】基板上に比誘電率の低い材料からなる絶縁膜4を形成する。次に、前記絶縁膜上にチャンバ内でSiOCH膜5を形成し、前記チャンバ内にプラズマを発生させた状態で徐々に膜中のカーボン濃度を減らし、前記SiOCH膜上に連続的にSiO2膜6を形成する。前記SiOCH膜と前記SiO2膜をハードマスクに用いて前記絶縁膜をプラズマ処理し、前記絶縁膜に溝7,8を形成する。その後、前記絶縁膜に形成した溝のエッチング表面をウェットエッチングし、プラズマ処理によるダメージ層と加工残渣物を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗な電極部を有し、且つパターニング工程数の削減可能な半導体装置及びその製造方法を提供する。

【解決手段】拡散層が形成された半導体基板の上に第1の金属層を形成する工程と、前記第1の金属層の上に開口部を有する絶縁層を形成する工程と、前記絶縁層の開口部において、前記第1の金属層の上に第2の金属層を形成する工程と、前記絶縁層を除去する工程と、前記第2の金属層の露出面に前記第2の金属層よりもイオン化傾向の小さい金属を含む第3の金属層を被覆する工程と、前記第3の金属層をマスクとして前記第1の金属層を除去することにより、前記第1の金属層と前記第2の金属層と前記第3の金属層とを有する電極配線を形成する工程と、を備えたことを特徴とする半導体装置の製造方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】多層配線構造において、下層金属配線への接続用スルーホール内にボイドが発生することを防止する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に金属配線3を形成し、全面に層間絶縁膜4を形成する。絶縁膜内にスルーホールを形成する。スパッタエッチングにより、スルーホール開口部に傾斜部を設け断面を大きくするとともに金属配線の表面の酸化Alを除去する。半導体基板を冷却し、基板温度20℃〜40℃で、スルーホールの内面を含む全面に第1のチタン膜6、窒化チタン膜7、第2のチタン膜8、第1のAl層9aを形成する。続いて基板を加熱して第2のAl層9bをリフローしながら形成した後、第3のAl層9cを形成する。

(もっと読む)

半導体装置とその製造方法

【課題】ダマシン配線構造を有する半導体装置に形成される配線表面の酸化物部を選択的に除去する。

【解決手段】ダマシン配線構造を有する半導体装置を製造するに際し、配線表面を、Xeのプラズマで逆スパッタリングする。本発明によれば、Xeのプラズマガスで逆スパッタリングすることにより、配線表面の酸化物部等を選択的に効率よく除去でき、ダマシン配線構造において、上下配線間のコンタクト抵抗の増大を回避できる。また、配線の上に形成されたCFなどの絶縁膜へのダメージを抑制でき、絶縁膜の誘電率変動も抑制できる。

(もっと読む)

真空処理装置及び真空処理方法

【課題】同一の処理室で、自然酸化膜が除去された後にシリコン基板の界面の酸素を確実に除去する。

【解決手段】NH3及びN2及びNF3を導入し、シリコン基板5の酸化表面にNHxFyを作用させることで(NH4)2SiF6を生成し、シリコン基板5を所定温度に制御することにより(NH4)2SiF6を昇華させてシリコン基板5の表面の酸化膜を除去し、続けてNH3及びN2及びNF3を導入し、温度が維持された状態でシリコン基板の表面にFラジカルを作用させてシリコン層をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ誘電体膜の劣化を防止しながら、金属配線間を絶縁膜で所望に埋め込むことができる半導体装置の製造方法を提供すること。

【解決手段】シリコン基板(半導体基板)1の上方に下地絶縁膜9を形成する工程と、キャパシタQ1、Q2を下地絶縁膜9の上に形成する工程と、キャパシタQ1、Q2を覆う第1層間絶縁膜68を形成する工程と、第1、第2配線溝30、33と、該配線溝30、33の底部から下に延びる第1、第2コンタクトホール31、34とを第1層間絶縁膜68に形成する工程と、第1、第2配線溝30、33と第1、第2コンタクトホール31、34とに第1拡散防止膜35と第1銅膜36(第1導電体)とを埋め込む工程と、水素を含まない還元性ガス中において第1銅膜36をアニールする工程とを有することを特徴とする半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】低抵抗の導電部を備える、信頼性の高い半導体装置を提供する。

【解決手段】ビアホール36a内及び配線溝36b内に、バリア層37を介して、CnMnを含有する第1導電層38、及びCuを主成分とする第2導電層39を形成し、清浄化後、低温酸化を行い、第1,第2導電層38,39表面にCu酸化物層40を形成する。その後、キャップ層の形成を行い、その状態で高温条件の熱処理を行うことで、第1,第2導電層38,39内のMnをCu酸化物層40に拡散させ、キャップ層との界面に、Cu酸化物層40にMnが含有された化合物層を形成する。これにより、第1,第2導電層38,39内のMnを減少させることが可能になり、さらに、キャップ層の密着性を向上させることが可能になる。

(もっと読む)

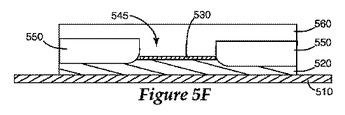

陽極酸化された薄膜構造用の電気的接続

第1の薄膜メタライゼーション層と第2の薄膜メタライゼーション層とを電気的に接続する回路ビアの形成のための手法が述べられる。ビアの形成では、第1のメタライゼーション層の陽極酸化に先立って、ビア接続領域に配置される陽極酸化バリア及び/又は補助パッドを使用する。バリアを形成するために使用される材料は、陽極酸化の際に陽極酸化液を実質的に透過せず、導電層とバリアとの間に酸化物が形成されることを阻止するものである。補助パッドは非陽極酸化性であり、陽極酸化の際に、パッドを通じて電流が流れることを実質的に防止するためにバリアによって覆われる。陽極酸化の後に、バリアは除去される。補助パッドが充分な導電性を有する場合には、バリアの除去後に第1のメタライゼーション層上に残存されてもよい。第2のメタライゼーション層が陽極酸化層上に配置され、ビア接続領域において第1の導電層と電気的に接触する。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置に設けられた半導体部品等の電極パッドとそれに接続されるべくインクジェット法により形成される配線との電気的な接続を好適に確保することのできる半導体装置、及びその半導体装置の製造方法を提供する。

【解決手段】半導体装置の第2電極パッド15に電気的に接続される金属配線膜19が、銀微粒子を分散媒に分散させた導電性インクからなる液滴(液層25L)の配置及び乾燥により形成される。このとき、第2電極パッド15の表面のメッキ層21に銀微粒子の結合層からなる中間層23Dを形成した後、中間層23Dを覆うかたちに上記分散媒を撥液する撥液材料を含む撥液層24を積層する。これにより、金属配線膜19は、その乾燥焼成を通じて中間層23Dと物理的に接続するようになり、撥液層24を間に挟みつつ第2電極パッド15と物理的に接続され、すなわち電気的にも接続されるようになる。

(もっと読む)

121 - 140 / 480

[ Back to top ]