Fターム[5F033RR22]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 有機材料 (4,730) | ポリイミド系樹脂 (1,337)

Fターム[5F033RR22]に分類される特許

1,321 - 1,337 / 1,337

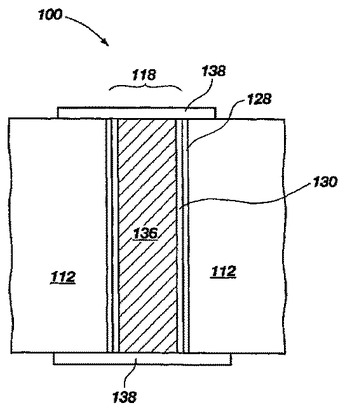

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

半導体構成部品に導電性ビアを形成するための方法が開示される。この方法は、第1の表面及び反対側の第2の表面を有する基板112を設けるステップを含む。この基板に、第1の表面と反対側の第2の表面の間に延びる少なくとも1つの穴118が形成される。基板のこの少なくとも1つの穴を画定している側壁にシード層128が形成され、導電層130でコーティングされ、この少なくとも1つの穴の内部の残りの空間に、導電性材料又は非導電性充てん材料136が導入される。基板を貫通した導電性ビアを、ブラインド・ホールを使用して形成する方法も開示される。本発明の導電性ビアを含む基板を有する半導体構成部品及び電子システムも開示される。  (もっと読む)

(もっと読む)

半導体装置、半導体装置の製造方法、識別ラベル及び情報担体

半導体装置(100)が、集積回路(20)及び第1及び第2接触面(31,33)を備える。これらは、垂直相互接続部(32,34)を用いて前記集積回路(20)へ接続される。この集積回路(20)は、基板の半導体層において存在する。この基板は、非有効領域(B)において存在しない。このことは、前記装置(100)の側面(101)において、如何なる伝導性材料又は半導体基板の部品も剥き出しにされることはないという事実を導く。これにより、2つの金属膜加工されたホイル間における識別ラベルへの装置のラミネートにおいて、装置(100)の側面(101)における不所望な接触による回路ショートのリスクは防がれる。  (もっと読む)

(もっと読む)

ボンドパッドの形成方法

パッシベーション層(68)及びポリイミド層(72)の下層には、ボンドパッド層(62)を覆うように最上層(64)が形成される。パッシベーション層(68)及びポリイミド層(72)の内部には、開口部(70,74)の形成時にボンドパッド層(62)を保護する最上層(64)を露出させるように、開口部(70,74)が形成される。一実施形態において、露出した最上層(64)は、過酸化水素及び水酸化アンモニウム等のアミンを用いて選択的にエッチングされる。この化学系は、ボンドパッド層(62)に攻撃を加えないため、ボンドパッド層の薄化が回避される。従って、ボンドパッドの信頼性が維持される。  (もっと読む)

(もっと読む)

集積接続部およびその製造方法

本発明は、電気的に導電性ではない絶縁層(34,36)における切り欠き部(37)に、少なくとも部分的または全体的に配置された外部導電構造部(44)を有する接続部に関する。切り欠き部(37)の底部には、導電性の内部導電構造部(22)が、絶縁層(34,36)の一方側に配置され、コンタクト領域において外部導電構造部と境界を形成している。コンタクト面は、切り欠き部(37)の他方側において、外部導電構造部(44)に配置されている。コンタクト領域とコンタクト面とは、互いに重ならないか、部分的にのみ重なっている。切り欠き部(37)の底部は、法線方向から見ると、コンタクト面の少なくとも半分または全面に重なるように配置されている。その結果、絶縁層(34、36)の段状部分は、コンタクト面と内部導電構造部(22)との間に延びる主要電流路の外側において、切り欠き部(37)の端部に位置する。  (もっと読む)

(もっと読む)

多層配線構造およびそれを用いた電子部品

【課題】小型化および低背化対応した多層構造の電子部品において、電子部品を構成する絶縁層の上下層に構成された配線部を電気的に接続する信頼性の高い電子部品を提供する。

【解決手段】第一の絶縁層1、第二の絶縁層2および第三の絶縁層3により構成される多層配線構造において、第一の絶縁層1上に設けられた第一の配線部と第二の絶縁層2上に設けられた第二の配線部との電気的な接続を、第二の絶縁層2に設けられた、一部に傾斜部4を有する貫通孔5に形成された導通配線部6により行なう。傾斜部4は、凸部15の上面に囲われる構成となる。

【効果】傾斜部4およびそれに繋がる第二の絶縁層2上に設けられらた導通配線部6が、凸部15の上面に保護されることで、信頼性の高い配線形成ができる。。また、信頼性の高い小型化および低背化に対応した電子部品を提供することが可能となる。

(もっと読む)

チタン・タングステンのベース層および関連構造体を含む導電構造体を形成する方法

基板、基板上の導電パッド、および基板上の絶縁層を含む電子デバイスを形成する方法であって、上記絶縁層は導電パッドの一部を露出するバイアホールを有する。詳細には、絶縁層上であり導電パッドの露出部分上に導電構造体を形成できる。導電構造体は、チタン・タングステン(TiW)のベース層と、アルミニウムおよび/または銅のうちの少なくとも1つの導電層とを含みうる。さらに、導電構造体のベース層を、導電層と絶縁層との間に形成できる。関連デバイスについても説明する。

(もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】半導体チップ上に絶縁膜を介して外部端子と再配線とが形成される半導体装置において、従来は外部端子、若しくは再配線からのノイズの影響から電子回路を保護する為、接地電位層を設けていたが、この接地電位層の為に工程が大幅に増加し、さらに、半導体装置の厚さが厚くなってしまう可能性があった。

【解決手段】本発明では、基板上の多層配線、即ち、それぞれが層間絶縁膜を介して積層された複数の層と、それぞれの層内に形成された配線とを有する多層配線の最上位の層内において、配線が配置された領域以外の領域に、定電位が与えられるノードに電気的に接続するメタル部材が形成される。これにより、工程を大幅に増加することなく、かつ、半導体装置の厚さを厚くすることなく、電子回路がノイズの影響を受けてしまう可能性を低減することができる。

(もっと読む)

半導体基板セグメント及びその製造方法並びに該セグメントを積層して成る積層半導体基板及びその製造方法

【課題】三次元積層に好適な半導体基板セグメント及びその製造方法並びに該セグメントを積層して成る積層半導体基板及びその製造方法を提供する。

【解決手段】半導体基板2のデバイス埋設側にデバイス3、感光性絶縁層4および配線5が設けられていると共に、基板端部側に第1の貫通微細導電体6が設けられている。また、デバイス電極と第1の貫通微細導電体6とが配線5により接続されている。さらにデバイス非埋設側の2bには、第1の貫通微細導電体6の先端である接続端6aが所定長さ突出すように形成されている。

(もっと読む)

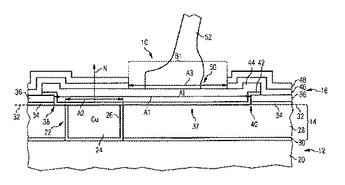

表示装置及びその作製方法

【課題】 配線抵抗による電圧降下の影響や画素への信号の書き込み不良や階調不良などを防止し、より高画質のEL表示装置や液晶表示装置を代表とする表示装置を提供することを課題とする。

【解決手段】 本発明はEL表示装置や液晶表示装置を代表とする表示装置に用いられる電極や配線として、Cuを有する配線を設ける。また、該配線のCuを主成分とする導電膜は、マスクを用いたスパッタ法により形成する。このような構成により、電圧降下や信号のなまりを低減することができる。

(もっと読む)

配線構造

【課題】 高い周波数が印加され、数cm〜数10cmの長さを有する配線の抵抗を低減し、伝送される信号波形のなまりを低減する。

【解決手段】 高周波が印加される配線111は、層間絶縁膜107を介して、配線111の線方向にそって複数設けられたコンタクトホールにより配線106と電気的に並列接続している配線構造を採用する。その配線構造を周辺回路一体型アクティブマトリクス型液晶表示装置の周辺回路に用いることで、高周波信号が印加される配線において信号波形のなまりを低減できる。

(もっと読む)

多層微細配線構造およびその作製方法

【課題】 高速情報処理用デジタル集積回路チップ内およびそのチップを搭載するためのパッケージ、モジュール、ボードなどの実装系内における多層配線の作製方法に関する新しい多層微細配線構造およびその作製方法を提案する。

【解決手段】 高解像感光性ポリイミドを絶縁層として、銅、銀、金、アルミニウム、パラジウム、ニオブなどの金属を配線層として用いて、ストリップライン、マイクロストリップライン、同軸ラインなどの伝送線路構造を有する多層微細配線構造を実現するため、広い周波数帯域について、インピーダンスが一定に制御され、デジタル高速信号伝送に適する線路を実現することができる。高解像特性を有する感光性ポリイミドを絶縁層として用いることにより、絶縁層へのビア穴加工がリソグラフィ工程のみで達成され、また、金属配線層をリフトオフ法によりパターン形成することにより、従来の多層配線技術に比べて、高密度の配線構造が実現でき、大幅に工程が簡略化される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】 アルミニウムを主成分とする導体膜パターンを有する半導体集積回路装置の信頼性を向上させる。

【解決手段】 アルミニウムを主成分とする導体膜16dを有する第1層配線L1をドライエッチング法によってパターニングした後、その加工側壁の側壁保護膜18およびエッチングマスクとして使用したフォトレジストパターン17aをプラズマアッシング処理によって除去する。続いて、絶縁膜15bおよび第1層配線L1の表面に付着した塩素成分を、酸素ガスとメタノールガスとの混合ガスを用いたプラズマアッシング処理によって除去する。この際、フォトレジストパターン17a等のアッシング除去処理時は、ウエハの主面温度が相対的に低くなるようにし、塩素成分の除去処理時は、ウエハの主面温度が相対的に高くなるようにする。また、それらのプラズマアッシング処理を別々の処理室で行う。

(もっと読む)

配線構造およびその製造方法

【課題】感光性絶縁膜を用いたダマシン配線法により、微細で信頼性の高い多層配線構造を形成する。

【解決手段】感光性ポリシラザンを主成分とした感光性絶縁膜で第1ビアホール6を有するビアホール用絶縁膜7を形成し、全面にスピン塗布法で第2の感光性絶縁膜8を形成する。そして、フォトリソグラフィ法による露光/現像のみで上記第1ビアホール6の上部に配線溝9あるいは第2ビアホール10を形成する。そして、この配線溝9および第2ビアホール10に導電体材料を埋め込んでデュアルダマシン配線を形成する。ここで、感光性絶縁膜の下層に反射防止機能を有しそのまま層間絶縁膜として使用できる絶縁膜を形成する。

(もっと読む)

半導体チップ、配線基板およびそれらの製造方法ならびに半導体装置

【課題】複数の半導体チップを配線基板に積層しても、半導体チップを積層した半導体装置の厚みおよび基板面積の増大および半導体チップ間の配線長の増加を招かない半導体チップ、その製造方法および半導体装置等を提供する。

【解決手段】半導体基板13と、半導体基板13の第1の面14に形成された第1の外部電極21と、半導体基板13の第2の面17に形成された第2の外部電極22と、半導体基板13に形成された貫通孔16とを有し、貫通孔16は第2の面17となす内角が鈍角をなして形成された斜面15に設けられ、第1の外部電極21と第2の外部電極22とは、貫通孔16の内壁および斜面15を経由して形成された導電パターン19により電気的に接続されている。

(もっと読む)

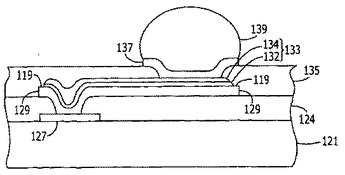

半導体装置及びその製造方法

【課題】チップサイズパッケージの実装時における信頼性を向上させる。

【解決手段】上面の面積を底面の面積より大きくすると共に、側面をくびれ形状に湾曲させた柱状端子9を形成し、この上に半田ボール12を搭載する。これにより、柱状端子9と半田ボール12の接触面積Sが従来のSに比して大きくできるため、せん断応力に対する強度を向上することができる。また、くびれ形状に湾曲させたことにより、剛性が低減し(つまりしなやかになり)、弾力性が増すことで、応力緩和性能も改善される。

(もっと読む)

多層配線構造

【課題】シールドによる配線容量の増加を抑え、シールド効果も補償できる多層配線構造を提供する。

【解決手段】半導体基板100上の酸化膜4上に所定の間隔で平行に配置された下層メタル配線3と、下層メタル配線3上の層間絶縁膜5上に下層メタル配線3と平行でかつ下層メタル配線3間に位置するように配置されたシールド用の配線メタル配線1と、メタル配線1上の層間絶縁膜6上に下層メタル配線3と重なるように配置された上層メタル配線2とから多層配線を構成し、シールド効果と同時に上層メタル配線2の全容量値の低減を図る。

(もっと読む)

配線構造及び配線形成方法

【課題】 電気的特性のみならず耐環境性にも優れた配線を実現し、ひいては当該配線を内装した半導体装置や配線基板等の信頼性の向上に寄与することを目的とする。

【解決手段】 絶縁層11,13に形成されたビア・ホールを介して下層の導体層12に電気的に導通するように絶縁層13と下層の導体層12とを覆って形成された金属薄膜14上に形成された配線層17の表面を、耐環境性に優れた材料からなる被覆層18で覆うように構成する。この被覆層18を構成する耐環境性に優れた材料としては、好適には、ニッケル/金、ニッケル/パラジウム、又はニッケル/パラジウム/金が用いられる。

(もっと読む)

1,321 - 1,337 / 1,337

[ Back to top ]