Fターム[5F033SS02]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | 原料ガス (1,958) | 無機シラン系ガス (316)

Fターム[5F033SS02]に分類される特許

1 - 20 / 316

半導体装置およびその製造方法

半導体装置およびその製造方法ならびに表示装置および電子機器

【課題】配線層の膜応力を低減し、製造歩留まりを向上することが可能な半導体装置およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】電界効果トランジスタを有する半導体装置のトランジスタ性能を向上させることのできる技術を提供する。

【解決手段】ゲート絶縁膜5およびゲート電極6n,6pの側面にサイドウォール9を形成した後、サイドウォール9の両側の半導体基板1に不純物をイオン注入して不純物領域を形成する。続いて、半導体基板1の主面上に第1絶縁膜14、第2絶縁膜15、および第3絶縁膜16を順次形成した後、イオン注入された上記不純物を活性化する熱処理を行う。ここで、第1絶縁膜14は、第2絶縁膜15よりも被覆性のよい膜であり、かつ、第2絶縁膜15とエッチング選択比が異なる膜である。第2絶縁膜15は、第1絶縁膜14よりも水素の拡散を阻止する機能が高い膜である。第3絶縁膜16は、第1絶縁膜14および第2絶縁膜15よりも内部応力の変化が大きい膜である。

(もっと読む)

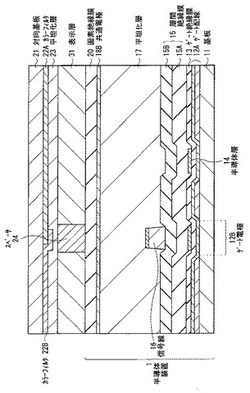

配線構造及びそれを備える薄膜トランジスタアレイ基板並びに表示装置

【課題】透明導電膜上における絶縁膜の膜浮きの発生を抑え、且つ、透明導電膜と金属膜との良好な電気的接続性を得ることができる配線構造を提供する。

【解決手段】それぞれ配線として機能する第1の導電膜2と第2の導電膜5と接続する配線変換部45において、第2の導電膜5の内側には刳り抜き部13が形成される。第2の導電膜5の上に設けられる第2の導電膜5は、第2の導電膜5の上面および刳り抜き部13に露出した端面を覆い、且つ、第2の導電膜5の外周の端面を覆わないように形成される。第1の透明導電膜6の上層の第2の透明導電膜7が、第2の導電膜5と第1の導電膜2とに接続することにより、第1の導電膜2と第2の導電膜5とが電気的に接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】論理素子のnチャネルMOSトランジスタに十分な膜厚の引張応力膜を形成し、メモリ素子がゲート電極間の層間絶縁膜の埋込不良を生じない製造方法の提供。

【解決手段】論理素子は、第1及び第2のnチャネルMOSトランジスタを含み、第1のゲート高さGH1及び第1のゲート長を有するゲート電極を有し、ゲート電極は第1の間隔Dを有し、メモリ素子は、第3および第4のnチャネルMOSトランジスタを含み、ゲート高さGH2および第2のゲート長を有するゲート電極を含み、論理素子及びメモリ素子は第1の引張応力膜64で覆われ、論理素子は、さらに第2の引張応力膜65で覆われ、論理素子及びメモリ素子のゲート間に形成された引張応力膜の最小距離は各々第1の距離LL及び第1の距離LMで隔てられ、第1のアスペクト比(GH1/LL)と、第2のアスペクト比(GH2/LM)とは略等しい。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を製造することはできないから、高抵抗の拡散抵抗は実現できなかった。

【解決手段】一組の薄膜構造体の対向する間隔に、サイドウォール形成用の絶縁膜を形成する際に生じる空隙を利用して露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を形成する。薄膜構造体を配線抵抗として利用すれば、これらを接続して設けることにより温度特性に優れる抵抗素子を構成することもできる。

(もっと読む)

成膜方法、これを含む半導体装置の製造方法、成膜装置、及び半導体装置

【課題】柱状形状を有し密に配列される電極の倒壊を防ぐことが可能な半導体装置を提供する。

【解決手段】電界効果トランジスタと、柱状形状を有するキャパシタとを有する半導体装置であって、前記電界トランジスタの不純物拡散領域と電気的に接続し、柱状形状を有する第1の電極と、前記第1の電極の少なくとも側面に形成される誘電体膜と、前記誘電体膜上に形成される第2の電極と、前記柱状形状を有する前記第1の電極の長手方向と交差する方向に延び、前記第2の電極の少なくとも一部を貫通して前記第1の電極を連結するホウ素添加窒化シリコン膜により形成される支持膜とを備える半導体装置により、上記の課題が達成される。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1のnMIS形成領域1Aにnチャネル型MISFETQnを、半導体基板1のpMIS形成領域1Bにpチャネル型MISFETQpを、それぞれ形成してから、nチャネル型MISFETQnおよびpチャネル型MISFETQpを覆うように引張応力の窒化シリコン膜5を形成し、nMIS形成領域1AおよびpMIS形成領域1Bの窒化シリコン膜5に紫外線照射処理を施す。その後、nMIS形成領域1Aの窒化シリコン膜5を覆いかつpMIS形成領域1Bの窒化シリコン膜5を露出するマスク層6aを形成してから、pMIS形成領域1Bの窒化シリコン膜5をプラズマ処理することで、pMIS形成領域1Bの窒化シリコン膜5の引張応力を緩和させる。

(もっと読む)

半導体装置の製造方法、半導体装置、電子機器

【課題】装置の信頼性や、製品の歩留まりなどを向上させる。

【解決手段】第1の開口と第2の開口との内部に金属材料を埋め込んで第1プラグと第2プラグとを設けると共に、第1プラグと第2プラグとの間を接続する接続配線を設けることで、接続導電層を形成する。そして、接続導電層において接続配線の上面を被覆するようにパッシベーション膜を形成する。このパッシベーション膜の形成工程では、高密度プラズマCVD法などのように埋め込み性に優れた成膜法で、SiO2などの絶縁膜を成膜することによって、パッシベーション膜を形成する。

(もっと読む)

半導体装置、半導体装置の製造方法、及び電子装置

【課題】縦型トランジスタのTDDB耐性を向上させ、かつ、閾値電圧がばらつくことも抑制する。

【解決手段】ゲート電極120の上端は、半導体基板100の表面よりも下に位置している。絶縁層340は、ゲート電極120上及びその周囲に位置する半導体基板100上に形成されている。絶縁層340は、第1絶縁膜342及び低酸素透過性絶縁膜344を有している。第1絶縁膜342は、例えばNSG膜であり、低酸素透過性絶縁膜344は、例えばSiN膜である。さらに、低酸素透過性絶縁膜344上には、第2絶縁膜346が形成されている。第2絶縁膜346は、例えばBPSG膜である。絶縁層340を形成した後、酸化雰囲気で処理することにより、縦型MOSトランジスタ20のTDDB耐性が向上する。また、絶縁層340が低酸素透過性絶縁膜344を有することにより、縦型MOSトランジスタ20の閾値電圧がばらつくことを抑制できる。

(もっと読む)

電気光学装置の製造方法

【課題】層間絶縁膜のコンタクトホールの内部にコンタクト用導電膜および埋め込み膜を設けた場合でも、コンタクトホールの外部で画素電極とコンタクト用導電膜とを確実に導通させることができる電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置100を製造するにあたって、層間絶縁膜45上にコンタクトホール45aの底部45eおよび内壁45fに重なるコンタクト用導電膜90をITO膜により形成した後、コンタクトホール45aの内部を埋める埋め込み膜48をシリコン酸化膜により形成し、その後、埋め込み膜48に対して反応性イオンエッチングを行い、コンタクト用導電膜90を露出させる。また、コンタクトホール45aの内部には埋め込み膜48を残す。その際、埋め込み膜48とコンタクト用導電膜90とのエッチング選択比を利用して埋め込み膜48を選択的に除去してコンタクト用導電膜90を露出させる。

(もっと読む)

パターン形成方法及び半導体装置の製造方法

【課題】基板の温度が100℃以下の低温環境下において、基板上の被処理膜をエッチングする際のマスクを所定のパターンに適切に形成する。

【解決手段】ウェハWの被処理膜400上に反射防止膜401とレジストパターン402が形成される(図10(a))。レジストパターン402がトリミングされると共に、反射防止膜401がエッチングされる(図10(b))。ウェハWの温度を100℃以下に維持した状態でプラズマ処理を行い、レジストパターン402及び反射防止膜パターン403上に、100MPa以下の膜ストレスを有するシリコン窒化膜404が成膜される(図10(c))。シリコン窒化膜404がエッチングされ、レジストパターン402及び反射防止膜パターン403が除去されて、被処理膜400上にシリコン窒化膜パターン405が形成される(図10(d))。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】シリコン層又はシリコン基板に補償ドープのために不純物を注入する必要がなく、安定的に高調波歪を低減する。

【解決手段】第1絶縁層20は、シリコン基板10上に形成されており、当該シリコン基板10に接している。また、配線40は、第1絶縁層20上に形成されている。ここで、第1絶縁層20下の不純物濃度は、2.0×1014cm−3以下である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、異なる膜特性を有する絶縁膜に形成されるコンタクト形状の制御性を向上させる。

【解決手段】半導体基板に素子領域を形成し、半導体基板の第1の領域上に、第1の絶縁膜を形成し、半導体基板の第2の領域上に、膜応力及びコンタクトの形成の際のエッチング加工時のエッチングレートが、第1の絶縁膜と異なる第2の絶縁膜を形成し、少なくとも第2の絶縁膜において、コンタクトが形成されるコンタクト領域に選択的にUV光を照射し、UV光を照射した後、第1の絶縁膜及び前記第2の絶縁膜をエッチングして前記コンタクトを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能と信頼性を向上させる。

【解決手段】nチャネル型MISFETQn1,Qn2を覆うように半導体基板1上に引張応力膜としての窒化シリコン膜5を形成する。窒化シリコン膜5は窒化シリコン膜5a,5b,5cの積層膜である。窒化シリコン膜5a,5bの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分よりも小さく、窒化シリコン膜5a,5bは、成膜後に紫外線照射処理を行って引張応力を増大させる。窒化シリコン膜5a,5b,5cの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分以上であり、窒化シリコン膜5cに対しては紫外線照射処理を行わない。

(もっと読む)

成膜方法

【課題】窒化シリコン膜と酸化シリコン膜との積層構造体を単一のプラズマCVD装置にて一貫して成膜する際に、両膜間に異質な薄膜が形成されないという機能を有しつつ、短時間で効率のよい成膜が可能な成膜方法を提供する。

【解決手段】本発明の成膜方法は、反応室2aに処理すべき基板Wを設置し、真空雰囲気中にてシリコンを含む原料ガスと窒素を含む一の反応ガスとを反応室内に導入し、放電用の高周波電力を投入してプラズマCVD法にて窒化シリコン膜を成膜する第1工程と、前記原料ガスを供給しながらプラズマ放電を維持した状態で、反応室内の窒素分圧を高める第2工程と、一の反応ガスの供給のみを停止し、酸素を含む他の反応ガスを反応室内に供給してプラズマCVD法にて酸化シリコン膜を成膜する第3工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】SOD法によって形成するシリコン酸化膜に、ボイドが発生することを抑制する。

【解決手段】基板、基板表面に形成された溝状領域G、及び溝状領域Gに埋設されたシリコン酸化膜8を有する半導体装置の製造方法であって、溝状領域Gを含む基板の表面を覆うライナー膜6を形成するライナー膜形成工程と、ライナー膜6の表面を水洗する水洗工程と、水洗後の残留水分を除去する水分除去工程と、基板表面にポリシラザン溶液をスピンコートにより塗布する塗布工程と、アニールによりポリシラザン溶液をシリコン酸化膜8に改質する改質工程とを備える。

(もっと読む)

タングステン膜又は酸化タングステン膜上への酸化シリコン膜の成膜方法及び成膜装置

【課題】 タングステン膜又は酸化タングステン膜上に酸化シリコン膜を形成しても、酸化シリコン膜のインキュベーション時間を短縮することが可能なタングステン膜又は酸化タングステン膜上への酸化シリコン膜の成膜方法を提供すること。

【解決手段】 被処理体上にタングステン膜又は酸化タングステン膜を形成する工程(ステップ1)と、タングステン膜又は酸化タングステン膜上にシード層を形成する工程(ステップ2)と、シード層上に酸化シリコン膜を形成する工程(ステップ3)と、を具備し、上記シード層をタングステン膜又は酸化タングステン膜上に、被処理体を加熱し、タングステン膜又は酸化タングステン膜の表面にアミノシラン系ガスを供給して形成する。

(もっと読む)

半導体装置

【課題】アクティブマトリクス型の液晶表示装置に代表される電気光学装置ならびに半導体装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現することを目的としている。

【解決手段】基板上に逆スタガ型のTFT上に無機材料から成る第1の層間絶縁層と、第1の層間絶縁膜上に形成された有機材料から成る第2の層間絶縁層と、前記第2の層間絶縁層に接して形成された画素電極とを設け、前記基板の端部に他の基板の配線と電気的に接続する入力端子部とを有し、該入力端子部は、ゲート電極と同じ材料から成る第1の層と、画素電極と同じ材料から成る第2の層とから形成されていることを特徴としている。このような構成とすることで、フォトリソグラフィー技術で使用するフォトマスクの数を5枚とすることができる。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数を削減し、電気抵抗値のバラツキを低減して歩留まりを向上させる。

【解決手段】まず、半導体基板1の平面1aに、開口部を有するマスク層を形成し、次いで、半導体基板1に、マスク層の開口部から電極パッド層4に達するビアホール6を形成した後、マスク層を除去する。次に、金属層形成工程において、半導体基板1に形成したビアホール6の底部6aとなる電極パッド層4上に、電極パッド層4よりも絶縁材料の密着性が低い金属層8を形成する。次に、絶縁層形成工程において、化学気相成長法にて金属層8を除く部分、即ちビアホール6の側壁部6bに絶縁材料からなる絶縁層9を形成する。そして、導電膜形成工程において、半導体基板1の平面1a及びビアホール6の内部に導電層12を形成する。

(もっと読む)

1 - 20 / 316

[ Back to top ]