Fターム[5F033SS21]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | 塗布 (1,869)

Fターム[5F033SS21]の下位に属するFターム

塗布後に焼成するもの (977)

Fターム[5F033SS21]に分類される特許

201 - 220 / 892

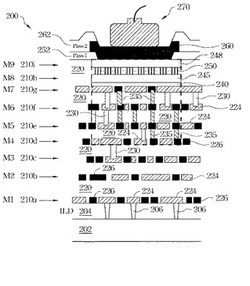

半導体装置のパッド構造

【課題】半導体装置のパッド構造を提供する。

【解決手段】半導体装置200は、半導体基板202、相互接続構造、複数のダミーメタルビア235及びパッド構造を備える。半導体基板202は、内部に複数の微小電子素子が設けられている。相互接続構造は、半導体基板202上に設けられ、複数の金属層210a〜210iと、金属層を隔離する複数のIMD層220とを有する。金属層210a〜210iは、最上金属層210iと、最下金属層210aと、最上金属層210iと最下金属層210aとの間に設けられた少なくとも2層の金属層とを含む。複数のダミーメタルビア235は、少なくとも2層の金属層間に設けられた1層又は2層以上のIMD層220内に形成される。パッド構造は、ダミーメタルビア235の上に直接設けられている。

(もっと読む)

半導体装置の製造方法

【課題】樹脂絶縁層の切削面に亀裂が生じて、絶縁信頼性が低下するのを抑制することのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板の主面上に形成した樹脂絶縁層を、バイトを用いた切削加工により一部除去する切削工程を備えた半導体装置の製造方法であり、切削工程として、表面に金属膜が積層された樹脂絶縁層の部分を切削する工程を含む。そして、金属膜が積層された樹脂絶縁層の部分を切削する際に、バイトの先端部及び該先端部の周辺部分に沿った樹脂絶縁層内の応力分布において、極大値の90%の幅が1.3μm以下となるように切削する。

(もっと読む)

半導体装置

【課題】ヒューズの線幅の縮小化を図ることが可能な半導体装置を提供する。

【解決手段】この半導体装置1では、ヒューズFUに隣接してダミーヒューズDFUを設け、ヒューズFUおよびダミーヒューズDFUの各々の配線幅を最小線幅に設定し、ヒューズFUおよびダミーヒューズDFUの間隔を最小間隔に設定した。したがって、OPCによってヒューズFUおよびダミーヒューズDFUの露光条件が最適化されるので、最小線幅のヒューズFUを形成することができる。

(もっと読む)

伝送線路および高周波デバイス

【課題】層間膜としてコンポジット膜を用いた伝送線路において伝送損失を低減するための技術を提供する。

【解決手段】接地導体膜301、層間膜310、および配線303をこの順に積層してなる伝送線路300であって、層間膜310は、第1の材料からなる粒子302Aが絶縁材料302Bに分散されてなるコンポジット膜302を含み、層間膜310の配線303側の表面からの粒子302Aの平均直径の深さまでの範囲における粒子302Aの密度が、層間膜310のそれ以外の範囲における粒子302Aの密度よりも小さい。

(もっと読む)

半導体ダイのコンタクト構造および方法

【課題】他の物体によって損傷、剥離、または亀裂を生じることなく、より粗野な処理、運送、および使用を可能にするよりよい緩衝を、半導体デバイスの金属化層に配置された低k誘電体層、ELK誘電体層、および/またはULK誘電体層の半導体ダイのコンタクトを形成するシステム、方法を提供する。

【解決手段】複数の誘電体層および導電層を含む基板101、複数の導電層の最上層115の1つと電気的に接続し、約15,000Åより大きい厚さを有する金属コンタクト105、および金属コンタクトと電気的に接続したコネクタを含む半導体デバイス。

(もっと読む)

半導体装置の製造方法

【課題】少ない工程数で樹脂コア及び樹脂保護膜を精度良く形成する。

【解決手段】電極パッド2が形成された基板(半導体基板1)上に、電極パッド2を露出させる開口3aを有する保護絶縁膜3を形成した後、感光性樹脂膜4を形成する。感光性樹脂膜4を多階調マスク5を用いて露光した後で現像する。この現像により、感光性樹脂膜4により構成される樹脂保護膜7と、樹脂保護膜7よりも厚膜の感光性樹脂膜4のパターンにより構成される樹脂コア6と、を一度に形成する。次に、樹脂コア6上から電極パッド2上に亘って配線8を形成する。

(もっと読む)

金属の付着

システム及び方法が、電圧切り換え可能な誘電体材料に1つ以上の材料を付着させることを含む。特定の態様では、電圧切り換え可能な誘電体材料が、導電バックプレーン上に配置される。いくつかの実施形態では、電圧切り換え可能な誘電体材料が、付着に関する特性電圧が相違する複数の領域を含む。いくつかの実施形態は、マスキングを含み、取り除くことが可能なコンタクトマスクの使用を含むことができる。特定の実施形態は、電気グラフトを含む。いくつかの実施形態は、2つの層の間に配置される中間層を含む。 (もっと読む)

半導体装置およびその製造方法

【課題】MRAMを含む半導体装置において、MRAMの特性を向上することができる技術を提供する。

【解決手段】配線L3およびデジット配線DLを形成した層間絶縁膜IL3の表面に対してプラズマ処理を実施する。まず、半導体基板1Sをチャンバ内に搬入し、窒素を含有する分子(アンモニアガス)と窒素を含有しない不活性分子(水素ガス、ヘリウム、アルゴン)とからなる混合ガスをチャンバ内に導入する。このとき、窒素を含有する分子の流量よりも窒素を含有しない不活性分子の流量が多い条件で、混合ガスを導入し、混合ガスをプラズマ化してプラズマ処理を実施する。

(もっと読む)

半導体装置

【課題】温度が上昇するほど電子又はホールの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板中のPウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Pウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ負の膨張係数を有しチャネル領域に引っ張り応力を加える第1絶縁層20を備えたN型の絶縁ゲート型電界効果トランジスタN1と、半導体基板中のNウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Nウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ正の膨張係数を有しチャネル領域に圧縮応力を加える第2絶縁層30を備えたP型の絶縁ゲート型電界効果トランジスタP1とを具備する。

(もっと読む)

湿式処理方法及び湿式処理装置

【課題】微細な穴を有する板状体を処理液に浸漬して行う湿式処理において、穴に気泡が残留することをより十分に抑制し、より均一な湿式処理を実現することが可能な湿式処理方法及び湿式処理装置を提供する。

【解決手段】密閉容器11内に板状体3を保持した状態で密閉容器11内を減圧する減圧工程と、減圧工程の後,密閉容器11内が減圧された状態で密閉容器11内へ処理液2に溶解可能な溶解性気体8を導入する溶解性気体導入工程と、溶解性気体導入工程の後,密閉容器11内が溶解性気体8で充満された状態で密閉容器11内へ処理液2を導入する処理液導入工程とを備えることにより、微細な穴に気泡が残留しない状態で基板3の湿式処理ができるようにしている。

(もっと読む)

半導体装置及びその製造方法

【課題】基板の内部であって、活性領域と素子分離領域との境界領域にコンタクトホールが形成された場合に、基板に流れるリーク電流を抑制できるようにする。

【解決手段】半導体基板10の上部に形成された素子分離領域10a及び活性領域10bと、半導体基板10の上に形成された絶縁膜12と、絶縁膜12に少なくとも活性領域10bを露出するように形成され、且つ、素子分離領域10aにおける活性領域10bとの境界領域を含む領域に形成されたコンタクトホール13と、コンタクトホール13における、活性領域10bの上に位置する第1の底面の上に形成された第1のバリアメタル膜14と、コンタクトホール13における、最下端に位置する第2の底面と第1の底面とをつなぐ壁面上に形成された第2のバリアメタル膜17とを備える。第2のバリアメタル膜17は、第1のバリアメタル膜14よりも比抵抗が高いことを特徴とする。

(もっと読む)

銅プラグを有する半導体デバイスおよびデバイスを形成するための方法

【課題】絶縁層がデバイスの最終配線層と接触する銅プラグを有する、半導体デバイスを提供する。

【解決手段】銅プラグと絶縁層とを分離する障壁層も存在可能である。他の実施形態では、絶縁層と銅プラグとの間にアルミニウム層も存在可能である。半導体デバイスを生成するためのプロセスも開示される。

(もっと読む)

半導体装置の製造方法

【課題】ダマシン法により絶縁膜に埋め込まれた配線を形成する半導体装置の製造方法に関し、絶縁膜にビアホールや配線トレンチ等の開口部を形成する際のエッチング処理を安定化しうる半導体装置の製造方法を提供する。

【解決手段】Cuを含む配線層と、絶縁膜と、有機膜と、第1の開口部を有するレジスト膜とを有する複数の半導体基板について、レジスト膜をマスクとして、第1の開口部内の有機膜をエッチングする工程と、第1の開口部内の絶縁膜をエッチングし、絶縁膜に、配線層を露出する第2の開口部を形成する工程と、第2の開口部内に露出した配線層の表面を水素プラズマ処理する工程とを、同じエッチング装置の処理室で連続して処理する際に、一の半導体基板について水素プラズマ処理を行う工程を行った後、一の半導体基板の次に処理する他の半導体基板について有機膜をエッチングする工程を行う前に、処理室内に付着したCu堆積物を除去する。

(もっと読む)

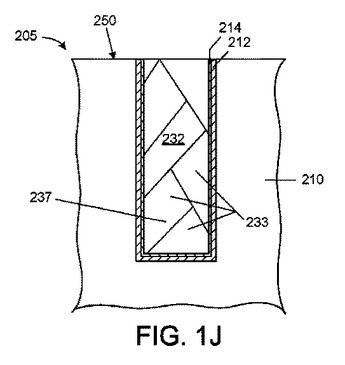

切欠構造のなかで長尺状ルテニウム膜上に多段階式銅鍍金を行う方法。

先端の集積回路にみられる切欠構造(206,207,208,209,211,213,264,275a,275b)において、長尺のルテニウム金属膜(214)に多段階で銅鍍金を行う方法である。長尺のルテニウム金属膜 (214)を利用すると、銅金属がトレンチ(266)及びビア(268)のような高アスペクト比の切欠構造(206,207,208,209,264,275a,275b)を充填するあいだ、不要な微細気泡が形成を防ぎ、前記ルテニウム金属膜(214)上に長尺の銅金属層(228)を含むサイズの大きい銅粒(233)が鍍金形成される。銅粒(233)は銅が充填された切欠構造(206,207,208,209,211,213,275a,275b)の電気抵抗を低下させ、集積回路の信頼性を向上させる。  (もっと読む)

(もっと読む)

半導体基板の製造方法

【課題】半導体基板が厚い場合においても貫通電極を高生産性、高品質で低コストで実現できる半導体基板の製造方法を提供することを目的とする。

【解決手段】半導体基板(101)にアクティブ面が露出する開口部(104)を有する電極パッド(102)を形成し、開口部(104)からアクティブ面の反対側の面に向かって凹部(105a)を形成し、凹部(105a)の内側に絶縁膜(106)を形成し、絶縁膜(106)と電極パッド(102)の表面に導電経路(107)を形成し、アクティブ面の反対側の面から半導体基板(101)を薄型化して凹部(105a)の底部を貫通させる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート配線が保護膜に覆われた構造において、保護膜に発生するクラックがゲート配線に到達することを防止することにより、ゲート−エミッタ間のショート不良を防止する。

【解決手段】第1保護膜25が表面電極17およびゲート金属配線18の間に配置されると共に、ゲート金属配線18を覆っている。また、第2保護膜26が第1保護膜25の上に形成されている。この場合、第2保護膜26は、第1保護膜25のうちの少なくともはんだ29に覆われる部分の上に形成されている。これにより、はんだ29実装前に引っかき傷等によって第2保護膜26にクラック31が発生したとしても、当該クラック31の進展を第1保護膜25と第2保護膜26との境界面で阻止することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート配線が保護膜に覆われた構造において、保護膜に発生するクラックがゲート配線に到達することを防止することにより、ゲート−エミッタ間のショート不良を防止する。

【解決手段】第1保護膜25が表面電極17およびゲート金属配線18の間に配置されると共に、ゲート金属配線18を覆っている。また、第2保護膜26が第1保護膜25の上に形成されている。この場合、第2保護膜26は、第1保護膜25のうちの少なくともはんだ29に覆われる部分の上に形成されている。これにより、はんだ29実装前に引っかき傷等によって第2保護膜26にクラック31が発生したとしても、当該クラック31の進展を第1保護膜25と第2保護膜26との境界面で阻止することができる。

(もっと読む)

カーボンナノチューブ配線及びその製造方法

【課題】カーボンナノチューブを有するプラグ配線において良好な電気的接続を得ることができるカーボンナノチューブ配線及びその製造方法を提供する。

【解決手段】第1配線層12上に層間絶縁膜13が形成され、層間絶縁膜13上に第2配線層14が形成されている。第1配線層12と第2配線層14との間の層間絶縁膜13内にはコンタクト孔15が形成される。コンタクト孔15内には、一端が第1配線層12に接続され、他端が第2配線層14に接続された複数のカーボンナノチューブ16が形成されている。さらに、層間絶縁膜13と第2配線層14との間にはストッパ膜17が形成され、ストッパ膜17の一部は複数のカーボンナノチューブ16の前記他端間に充填されている。

(もっと読む)

回路基板の製造方法

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

半導体装置

【課題】スルーホールの深さを正確に制御して、特定の配線層に選択的にエアギャップを形成した半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体素子を有する半導体基板1と、半導体基板1の上方に形成され、配線10a、10b、10c、10d、配線10c、10dの周囲のエアギャップ101、およびエアギャップ101に連続するスルーホール102含む配線構造と、スルーホール102下に形成されたスルーホールストッパー103と、を有する。

(もっと読む)

201 - 220 / 892

[ Back to top ]