Fターム[5F033TT08]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 側壁絶縁膜 (2,038) | 電極、配線の側壁 (1,106)

Fターム[5F033TT08]に分類される特許

181 - 200 / 1,106

基板構造物の製造方法及び半導体装置の製造方法

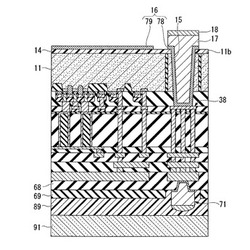

【課題】製造工程を増加させることなく、基板構造物及び半導体装置の反りを調整することのできる基板構造物の製造方法、及び半導体装置の製造方法を提供する。

【解決手段】半導体基板11の裏面11b側から半導体基板11に、貫通電極接続用配線パターン38を露出する貫通孔15を形成し、次いで、半導体基板11の裏面11b及び貫通孔15を覆うと共に、第1及び第2のシード層78,79により構成された裏面シード層16を形成し、次いで、第1のシード層78が形成された貫通孔15に、めっき法により貫通電極17を形成し、次いで、第1のシード層78と、貫通電極17が形成されていない第2のシード層79とを絶縁するように、エッチングにより、第1のシード層78の周囲に位置する部分の裏面シード層16を除去して、反り調整部材として機能する第2のシード層79を残す。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】1メモリセルが6トランジスタを有するSRAMにおいて、コンタクトの微細化をするとリークの発生を回避できる半導体記憶装置及びその製造方法を提供する。

【解決手段】1メモリセルが第1及び第2ドライバトランジスタ(DTr1、DTr2)、第1及び第2転送トランジスタ(TTr1,TTr2)並びに第1及び第2ロードトランジスタ(LTR1,LTr2)の6トランジスタを有するSRAMにおいて第1ドライバトランジスタと第2ドライバトランジスタのソースドレイン領域に基準電位を印加するための接地コンタクトCgと、第1ロードトランジスタと第2ロードトランジスタのソースドレイン領域に電源電位を印加するための電源電位コンタクトCcの径が、共通コンタクトCsを除く他のコンタクト(Cb,Cn,Cw)の径より大きく形成された構成とする。

(もっと読む)

半導体装置

【課題】本発明は小型化を図ると共に、デバイス形成層を保護した状態で貫通孔及び貫通電極を形成することを課題とする。

【解決手段】デバイス形成層18と電極パッド20を有する半導体素子14の電極パッド20と半導体素子14の他面側に形成された再配線パターン52とを接続する貫通電極56を有する半導体装置50であって、半導体素子14の上面側にデバイス形成層18及び電極パッド20を形成し、電極パッド20及びデバイス形成層18の表面に第1レジスト層62を形成し、電極パッド20にエッチングにより開口64を形成し、開口64に連通する位置に貫通孔54をエッチングにより半導体素子14に形成する。第1レジスト層62によりデバイス形成層18を保護すると共に、貫通電極56を設けてフリップチップ接続を可能にして小型化を図る。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置及びその製造方法

【課題】発熱に対して効率的に冷却を行うことができる、半導体装置を提供する。

【解決手段】半導体層の表面に形成された活性領域5,6と、N型の不純物を有する半導体から成るN型ゲート7Nと、P型の不純物を有する半導体から成るP型ゲート7Pと、N型ゲート7N及びP型ゲート7P及び活性領域5,6に接続された第1の金属配線13と、P型ゲート7P及びN型ゲート7Nに接続された第2の金属配線と15、第2の金属配線15に接続され、熱を外部に放出するための放熱部19とを含む冷却機構素子を備えた半導体装置を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】第1の領域中の層間絶縁膜を湿式エッチングにより除去する際に、使用する薬液が第2の領域に浸透することを防止する。これにより、第2の領域の特性の劣化がない、高性能の半導体装置を提供する。

【解決手段】第1の領域と、第1の領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた第2の領域と、を有する半導体装置。第1の領域は、導電性を有する第1の膜によって構成された第1の電極を有する。第1の領域中の第1の電極の表面は、第2の膜で覆われていない。ガードリングは、凹状の溝の内壁を覆う第1の膜と、凹状の溝の内部において少なくとも第1の膜の表面の一部を覆う絶縁性の第2の膜を有する。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】磁気素子を備えた半導体装置の製造で、磁気素子のダメージを抑止し、下部電極膜の加工に灰化処理を用いないことで下層に存する導電部材の酸化を防止する。

【解決手段】半導体基板10上で、上部電極膜43上に形成したレジストマスク44で上部電極膜43をエッチングして上部電極43aとし、上部電極43aをマスクとしてMTJ膜42をエッチングしてMTJ42aとし、上部電極43a及びMTJ42aを覆う保護膜45aを形成し、上部電極43a及びMTJ42aを保護膜45aを介して覆うように、保護膜45a上にレジスト46を形成し、レジストマスク46で保護膜45aをエッチングし、保護膜45aをマスクとして下部電極膜41エッチングして下部電極41aとし、上部電極43a、MTJ42a及び下部電極41aを覆うように保護膜45bを形成して、保護膜45b上に層間絶縁膜47を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極にシリサイドを形成しつつ、拡散領域に接続するコンタクトとゲート電極の間隔を確保する。

【解決手段】被覆絶縁膜120は、ゲート電極140のチャネル幅方向における少なくとも一部上に形成されている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、ゲート電極140上、及び被覆絶縁膜120上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。シリサイド層142は、ゲート電極140上に形成されている。サイドウォール160は、被覆絶縁膜120が形成されている領域においてはゲート電極140より高く形成されている。そしてコンタクト210は、ゲート電極140のうち被覆絶縁膜120が形成されている領域に面している。

(もっと読む)

半導体装置及びその製造方法

【課題】温度変化に起因したパッシベーションクラックを適切に防止することができる半導体装置の提供。

【解決手段】本発明による半導体装置1は、絶縁膜11と、絶縁膜11上に形成されるバリア層16と、バリア層16上に配されるアルミ配線12と、アルミ配線12の上部に設けられるキャップメタル18又は防腐処理部21と、アルミ配線12の側部に設けられるサイドウォール17と、を備えることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラートランジスタにおいて、ゲートコンタクトとシリコン基板との間のショートを抑制した半導体装置及びその製造方法を得るという課題があった。

【解決手段】半導体からなる基板1と、一面1aから突出され、前記半導体からなる第1の突出部2と、一面1aに設けられた溝部1cに充填された第1の絶縁体3と、第1の突出部2に隣接して一面3aから突出され、第1の絶縁体3からなる第2の突出部4と、第1の突出部2の側面を覆うゲート絶縁膜5と、ゲート絶縁膜5を覆うゲート電極6と、第1の突出部2に設けられた上部拡散層13と、下部拡散層14と、第2の突出部4の側面を覆うとともにゲート電極6に接続された連結電極60と、第1の突出部2及び第2の突出部4を覆う層間絶縁膜と、前記層間絶縁膜を貫通して連結電極60に接するゲートコンタクト10と、を有する半導体装置及びその製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

歪み材料を有する半導体デバイス

歪み材料を有する半導体デバイスが開示される。特定の実施形態では、半導体デバイスは、第1ドレインと第1ソースとの間に第1ゲートを含む第1セルを含む。半導体デバイスはまた、第1セルに隣接する第2セルを含む。第2セルは、第2ドレインと第2ソースとの間に第2ゲートを含む。半導体デバイスはさらに、第1ソースと第2ソースとの間にシャロートレンチ分離領域を含む。第1ソースおよび第2ソース上の第1量の歪み材料は、第1ドレインおよび第2ドレイン上の第2量の歪み材料より多い。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMを含む半導体装置において、MRAMの特性を向上することができる技術を提供する。

【解決手段】配線L3およびデジット配線DLを形成した層間絶縁膜IL3の表面に対してプラズマ処理を実施する。まず、半導体基板1Sをチャンバ内に搬入し、窒素を含有する分子(アンモニアガス)と窒素を含有しない不活性分子(水素ガス、ヘリウム、アルゴン)とからなる混合ガスをチャンバ内に導入する。このとき、窒素を含有する分子の流量よりも窒素を含有しない不活性分子の流量が多い条件で、混合ガスを導入し、混合ガスをプラズマ化してプラズマ処理を実施する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】縦型MOSトランジスタを備えた半導体装置を形成する際のゲート電極とコンタクトプラグとの短絡を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、前記半導体基板上にシリコン窒化膜(SiN膜)からなるマスク窒化膜のパターンを形成したのちに、溝および半導体ピラーを前記半導体基板に形成する第一工程と、前記マスク窒化膜を残存させたまま、前記溝を覆うゲート絶縁膜を形成したのちに前記半導体ピラーよりも低い高さのゲート電極を形成する第二工程と、前記溝を覆うように、シリコン酸窒化膜(SiON膜)からなるライナー膜を形成したのちに、前記ライナー膜上を覆い、かつ、前記溝内を充填するように層間膜(SOD膜)を形成する第三工程と、前記マスク窒化膜をエッチングにより選択的に除去する第四工程と、を採用する。

(もっと読む)

半導体装置

【課題】温度が上昇するほど電子又はホールの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板中のPウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Pウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ負の膨張係数を有しチャネル領域に引っ張り応力を加える第1絶縁層20を備えたN型の絶縁ゲート型電界効果トランジスタN1と、半導体基板中のNウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Nウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ正の膨張係数を有しチャネル領域に圧縮応力を加える第2絶縁層30を備えたP型の絶縁ゲート型電界効果トランジスタP1とを具備する。

(もっと読む)

半導体集積回路装置

【課題】MISFETのソース/ドレイン間の寄生容量を減少させる電極および配線を有したメモリや、メモリ混載のロジック等の半導体集積回路を提供する。

【解決手段】ゲート電極5より上方に少なくともキャパシタ電極14,16または情報記憶部の一部を有する半導体集積回路装置において、MISFETは、ソース・ドレイン拡散層7に接続する少なくとも1つずつの第1のプラグ9を有する。ソース・ドレイン拡散層7のどちらか一方に、第1のプラグ9を介して接続し、キャパシタまたは情報記憶部の一部の下部電極14と同一工程またはそれより前工程の配線層から成る第1の配線21を設け、一方のソース・ドレイン拡散層7の上方に第1の配線21と他の配線22を接続するプラグを設けず、また、ソース・ドレイン拡散層7の他方の領域の上方に第1の配線21と同一工程の配線を設けないようにする。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を高い製造歩留まりで提供し得る半導体装置の製造方法を提供することにある。

【解決手段】側壁にサイドウォール絶縁膜が形成されたゲート配線20を形成する工程と、第1の応力膜38を形成する工程と、第1の応力膜上にエッチングストッパ膜40を形成する工程と、エッチングストッパ膜をエッチングし、第1の応力膜のうちのサイドウォール絶縁膜を覆う部分上にエッチングストッパ膜を選択的に残存させる工程と、第2の領域4を露出する第1のマスクを用いて第2の領域内の第1の応力膜をエッチングする工程と、第2の応力膜42を形成する工程と、第1の領域2を露出する第2のマスクを用いて第1の領域内の第2の応力膜をエッチングする工程と、第1の領域と第2の領域との境界部におけるゲート配線に達するコンタクトホール46aを形成する工程とを有している。

(もっと読む)

電子部品の製造方法

【課題】側壁転写プロセスにより複数層に形成された配線層を有する電子部品を簡便且つ安価な方法で得ること。

【解決手段】パターン27の側壁に沿った閉ループを有する側壁膜30を形成し、このパターン27を除去して前記側壁膜30を残存させた後この側壁膜30をマスクとして下地材料を選択的に除去する側壁転写プロセスを用いて下層配線層21を形成する第1の工程と、前記下層配線層21の上層に、前記側壁転写プロセスを用いて1層以上の上層配線層41,51を他の層22,23,24,42,43,44を介して形成する第2の工程と、前記下層配線層21および前記上層配線層41,51のそれぞれを切断するエッチングを一括で行うことにより、前記下層配線層21と前記上層配線層41,51に対して閉ループカットを施す第3の工程と、を含む。

(もっと読む)

集積回路構造

【課題】導電ビア(TSV)に接続されるウェハ背部の相互接続構造を有する集積回路構造を提供する。

【解決手段】集積回路構造は、正面と背面を有する半導体基板と、半導体基板を貫通する導電ビアと、半導体基板の背面上の金属構造と、を備える。金属構造は、導電ビアを被覆して、接触する金属パッド、及び、導電ビア上の金属線を含む。金属線は、デュアルダマシン構造を含む。集積回路構造は、更に、金属線上のバンプを具備する。

(もっと読む)

181 - 200 / 1,106

[ Back to top ]